Chip power consumption optimization method, device, computer equipment and storage medium

An optimization method and power consumption technology, which is applied in computing, instruments, electrical digital data processing, etc., can solve problems such as insufficient power consumption reduction and unsatisfactory chip battery life, and achieve the effect of saving chip power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0048] In order to make the purpose, technical solution and advantages of the present application clearer, the present application will be further described in detail below in conjunction with the accompanying drawings and embodiments. It should be understood that the specific embodiments described here are only used to explain the present application, and are not intended to limit the present application.

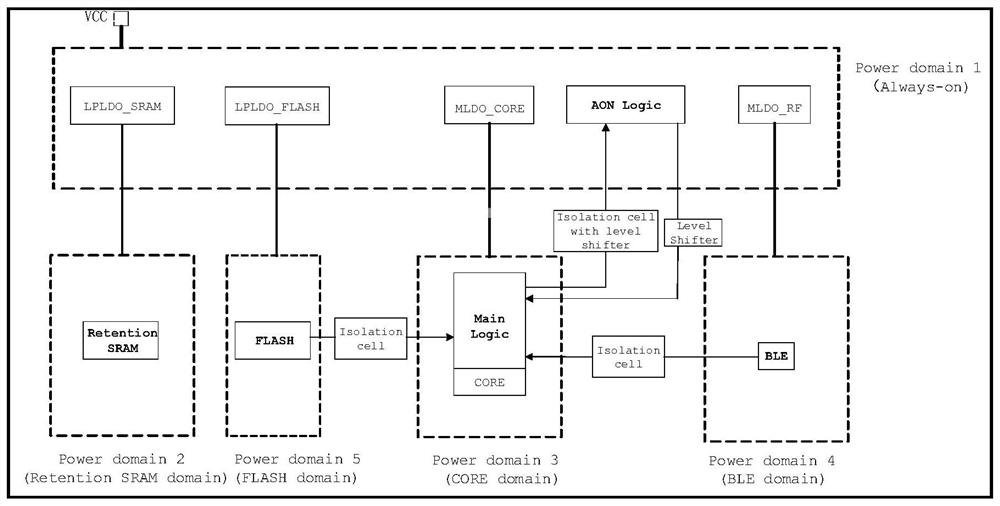

[0049] The chip power consumption optimization method provided by this application can be applied to such as figure 1 shown in the chip power domain architecture. Among them, the whole chip system is divided into 5 power domains, which are power domain 1 (Always-on domain, normally open power domain), power domain 2 (Retention SRAM domain, static memory power domain), power domain 3 (CORE domain , core power domain), power domain 4 (BLE domain, Bluetooth power domain), power domain 5 (FLASH domain, flash memory power domain), each power domain uses its own voltage for pow...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com