Low-power-consumption chip architecture awakened by utilizing I2C address matching and awakening method

A technology of address matching and low power consumption, applied in the fields of instruments, electrical digital data processing, digital data processing components, etc. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

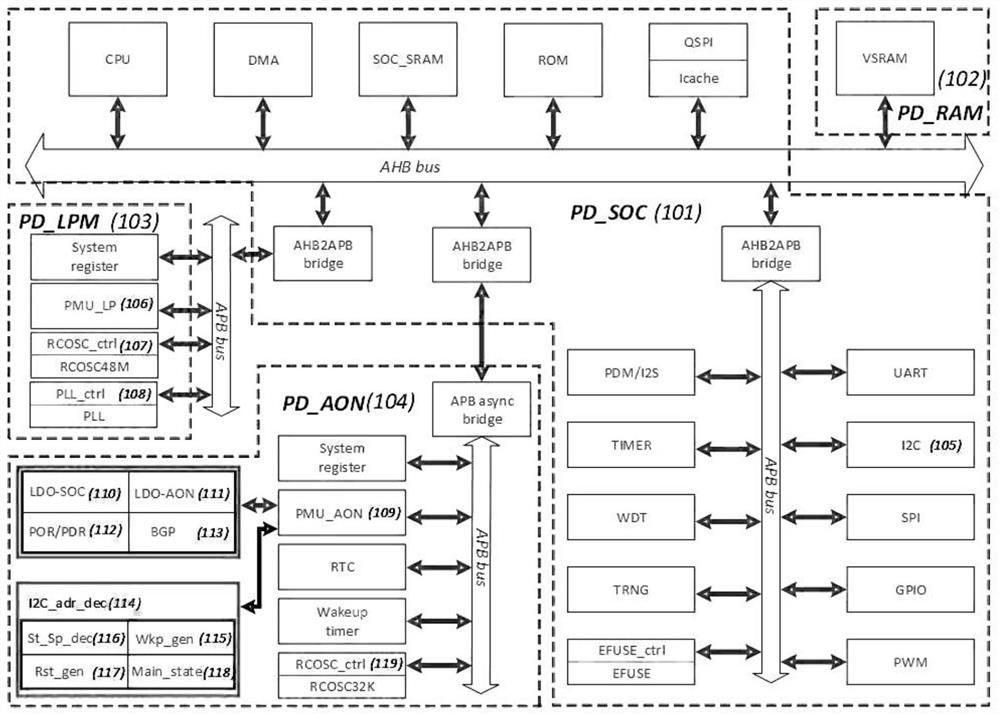

[0032] This embodiment discloses a low-power chip architecture that uses I2C address matching to wake up, see figure 1 As shown, the I2C slave low-power chip designed with this architecture includes four power domains including PD_SOC power domain (101), PD_RAM power domain (102), PD_LPM power domain (103) and PD_AON power domain (104). The descriptions of the four power domains are as follows:

[0033] PD_SOC power domain (101): the components of the system on chip including CPU, memory, bus, DMA and peripherals, which are the parts that realize the main functions of the system on chip;

[0034] PD_RAM power domain (102): includes a group of components including SRAM with retention and powerdown modes, which can realize the combination of various low-power modes such as overall power on and off, retention and powerdown of each group, etc., which is to flexibly respond to different Part of the scene's memory requirements.

[0035] PD_LPM power domain (103): components in...

Embodiment 2

[0044] This embodiment discloses a specific working process and principle of an I2C slave low-power chip with a low-power chip architecture awakened by I2C address matching;

[0045] An I2C slave low-power chip in the embodiment of the present invention has 6 power consumption modes in total, and the working conditions of each power supply in different power consumption modes are shown in the following table:

[0046]

[0047] Table 1 Power Supply Component Behavior

[0048] The working conditions of each power domain in different power consumption modes are shown in the table below:

[0049]

[0050] Table 2 Power Domain Behavior

[0051] An I2C slave low-power chip disclosed in the embodiment of the present invention, the switching of each power consumption mode is as follows: image 3 shown. When you need to switch between various low-power modes, you need to return to Normal mode first. The way to enter each mode from the Normal mode is to run the software by the...

Embodiment 3

[0057] This embodiment discloses a method for waking up a low-power chip architecture by using I2C address matching. First, low-power modes Sleep_1 and Sleep_2 are defined. In Sleep_1 mode and Sleep_2 mode, PD_SOC is powered off, and the I2C_adr_dec slave address matching module of PD_AON is activated. Start, at this time, use the I2C slave address matching module I2C_adr_dec to complete the I2C slave address matching without a clock, and generate a wake-up signal to trigger the chip to exit the low-power mode.

[0058] RCOSC32K (119) still works in Sleep_1 mode, and the RTC module and Wakeup timer module of PD_AON (104) can also operate, both of which can be used as the self-awakening source of the I2C slave low-power chip, triggering the chip to exit from Sleep_1 mode to normal operation model.

[0059] In Sleep_2 mode, RCOSC32K (119) stops working, and the RTC module and Wakeup timer module of PD_AON (104) also stop running. The I2C slave low-power chip has no self-awakenin...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com