Multi-core package-level system based on core particle framework and task mapping method thereof for core particles

A task mapping and chip technology, applied in complex mathematical operations, instruments, electrical digital data processing, etc., can solve problems such as reduced bandwidth efficiency, large routing delay, etc., achieve on-chip storage, reduce local storage requirements, and reduce DRAM. The effect of the number of visits

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0046] The present invention will be further described in detail below in conjunction with specific embodiments, which are explanations of the present invention rather than limitations.

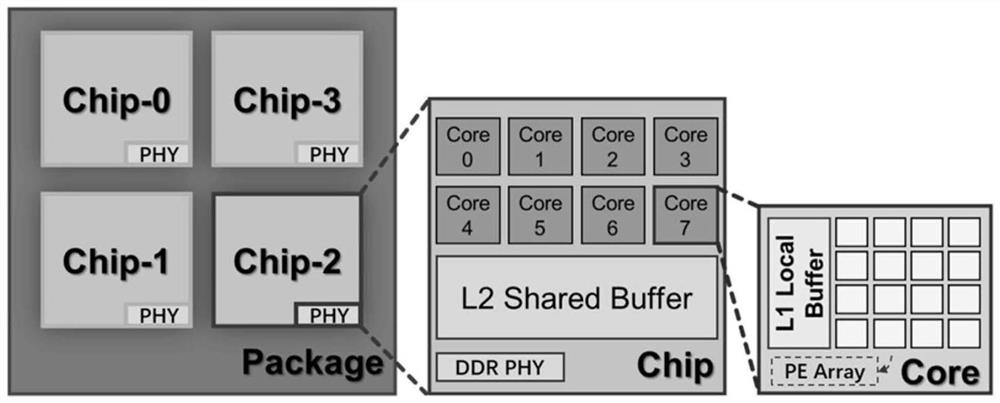

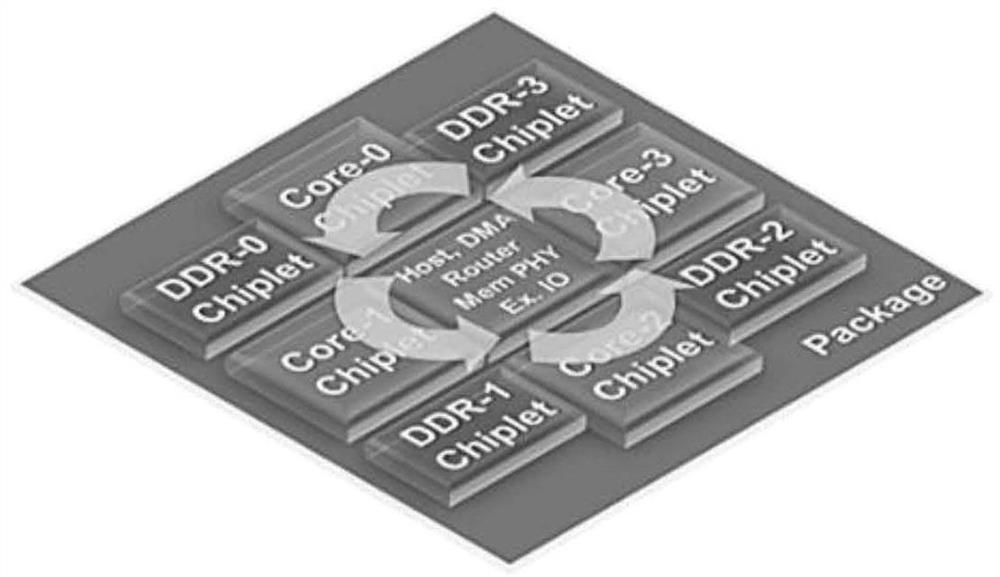

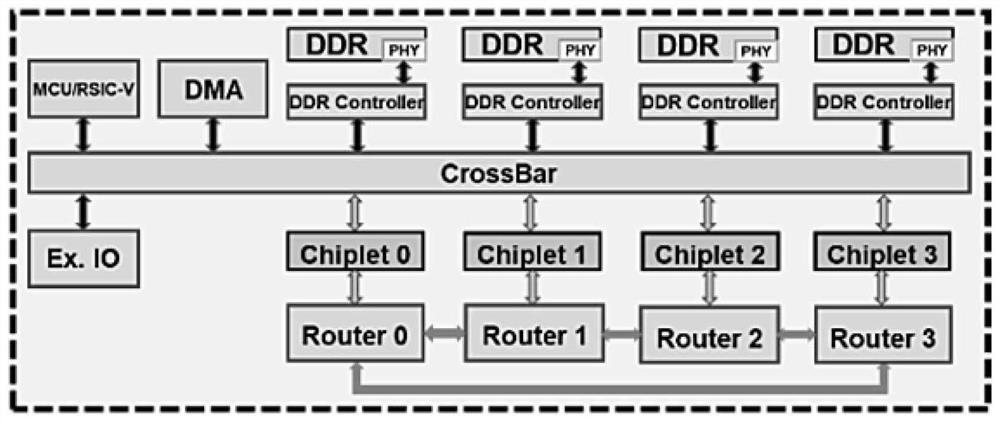

[0047] The present invention establishes a chip-based multi-core packaging system and a chip-oriented task mapping method. Taking the DNN scene as a research example, it can provide the optimal allocation scheme in different computing layer configurations: realize the communication between Chiplets , Chiplet storage space allocation, chiplet access to DRAM better solution. Guide the development of Chiplet systems for a series of benchmark tasks.

[0048] In the multi-core package-level system based on chip architecture described in the present invention, the parallel level is divided into three: parallel between chiplets, parallel between cores, and parallel between processing units (PEs). parallel. When deploying large-scale DNN operations to the Chiplet system, by allocating the work task...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More