Chip algorithm module verification method and system based on C algorithm model

An algorithm model and algorithm module technology, applied in the computer field, can solve problems such as increased development costs, increased number of files, and large storage space, and achieve the effects of ensuring confidentiality, improving verification efficiency, and saving storage space

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

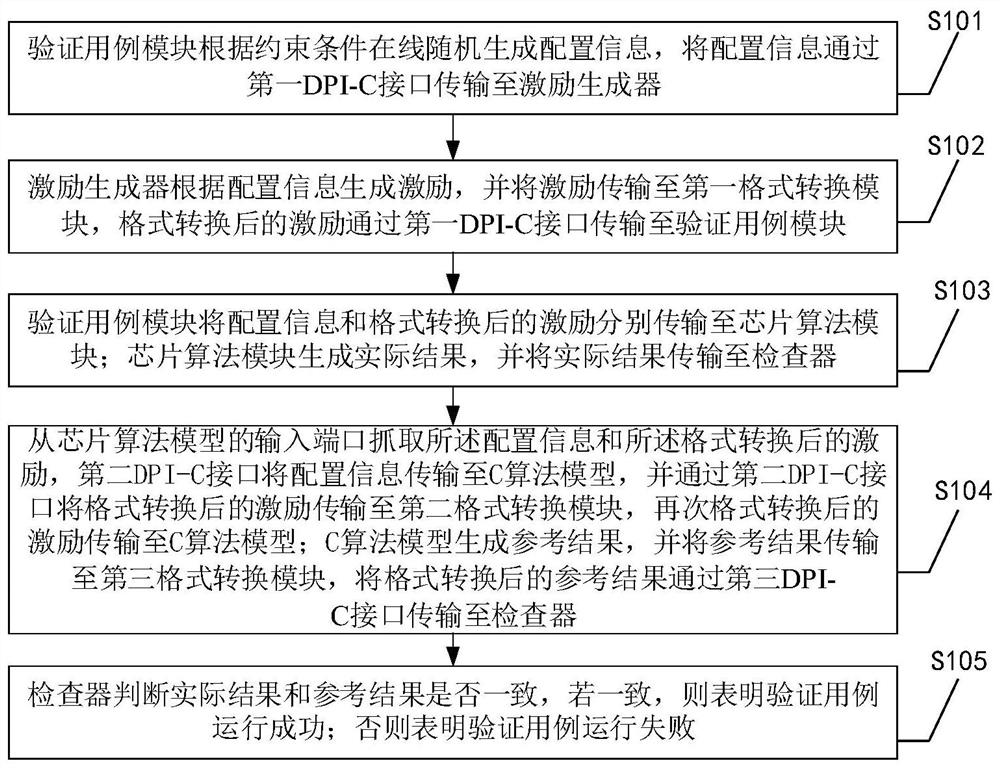

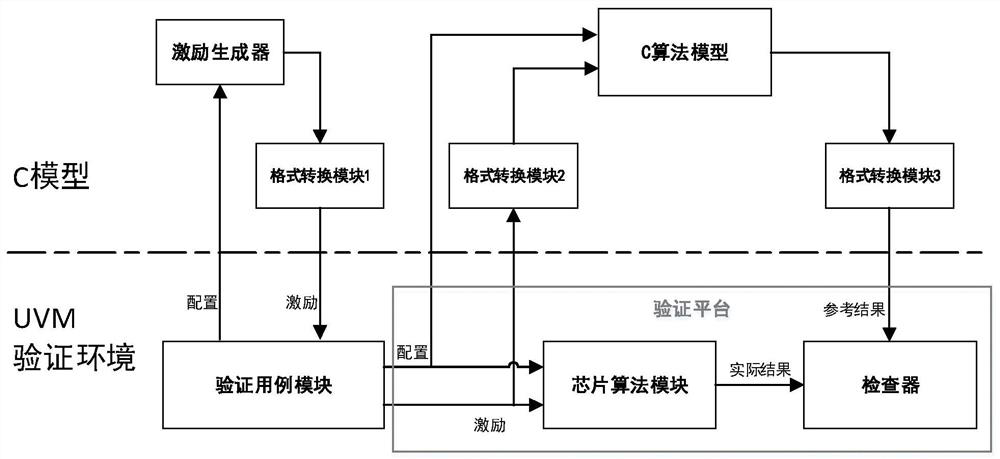

[0067] Embodiment 1 of a chip algorithm module verification method based on a C algorithm model provided by the present application will be introduced below. see figure 1 and figure 2 , the first embodiment includes:

[0068] S101. The verification use case module randomly generates configuration information online according to the constraints, and transmits the configuration information to the incentive generator through the first DPI-C interface;

[0069] DPI-C interface, direct programming interface C, is a programming method for direct interaction between System Verilog (a hardware design and verification language, SV for short) and C.

[0070] S102, the incentive generator generates incentives according to the configuration information, and transmits the incentives to the first format conversion module, and the format-converted incentives are transmitted to the verification use case module through the first DPI-C interface;

[0071] S103, the verification use case mod...

Embodiment 2

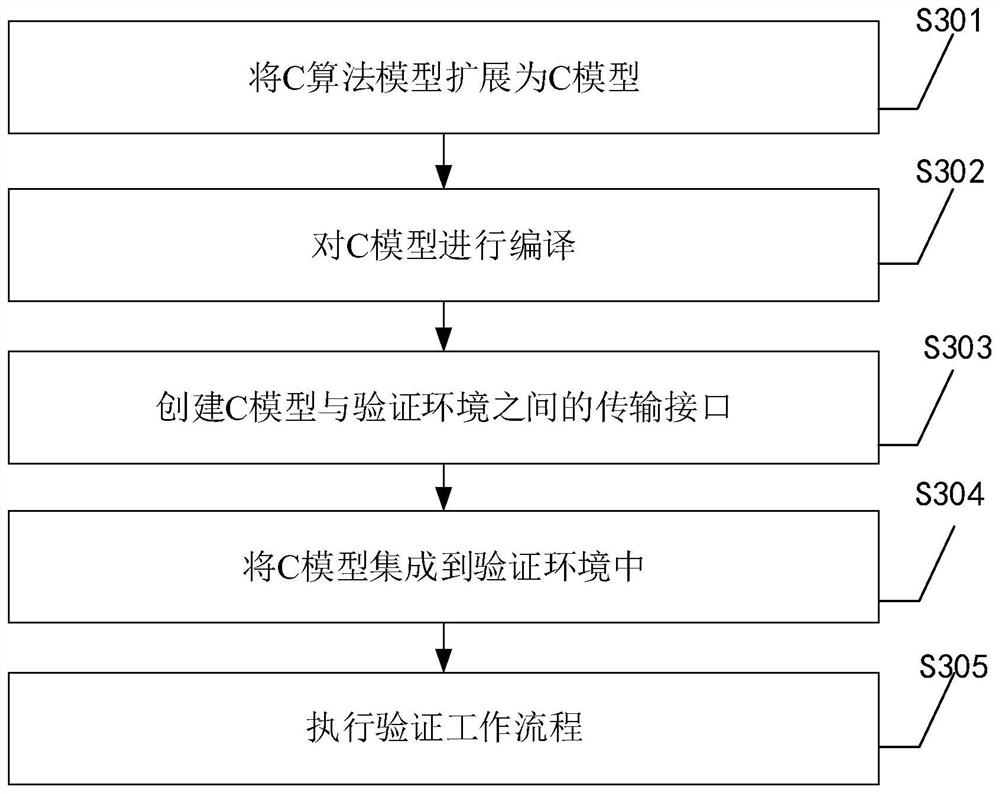

[0102] The second embodiment connects the C model with the verification environment through the DPI-C interface, and realizes the automatic operation of the verification case and the automatic comparison of the results without using the file as the data transmission medium. see image 3 and Figure 7 , the implementation process of the second embodiment is as follows:

[0103] S301. Extend the C algorithm model into a C model.

[0104] Extend the C algorithm model and add related functional modules, while ensuring that the C algorithm model can run independently and is easy to debug, and at the same time realize the matching with the hardware, making it easy to integrate into the verification environment. C algorithm model extension such as Image 6 shown, where the dashed box and the dashed arrow represent optional functions, which can be enabled or disabled by dynamic switches. The C model specifically includes:

[0105] (1) The test routine module is used to receive th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com