Chip splicing platform and chip splicing substrate leveling method

A chip and platform technology, applied in the field of chip splicing platform and chip splicing base plate leveling, can solve the problems affecting the flatness of the chip splicing surface, and achieve the effect of ensuring the flatness, improving the chip yield and improving the splicing efficiency.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

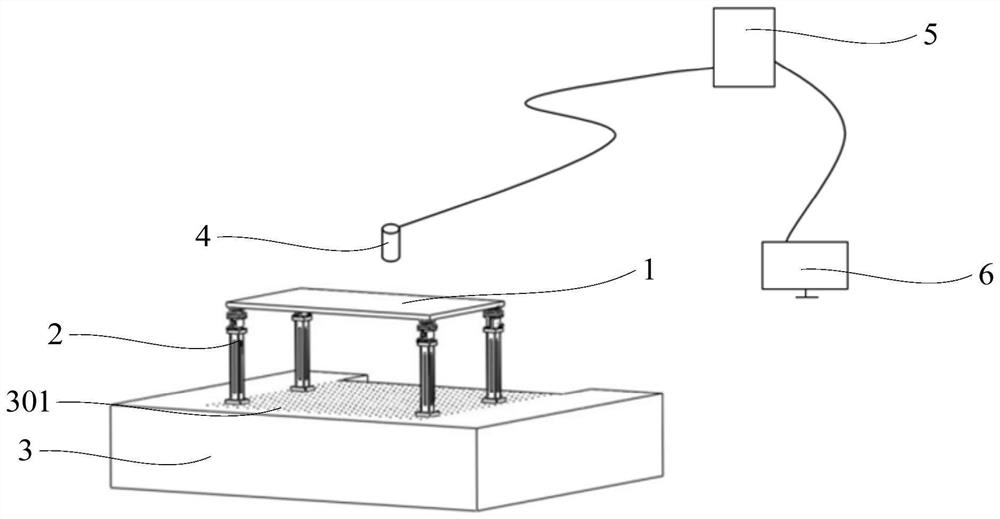

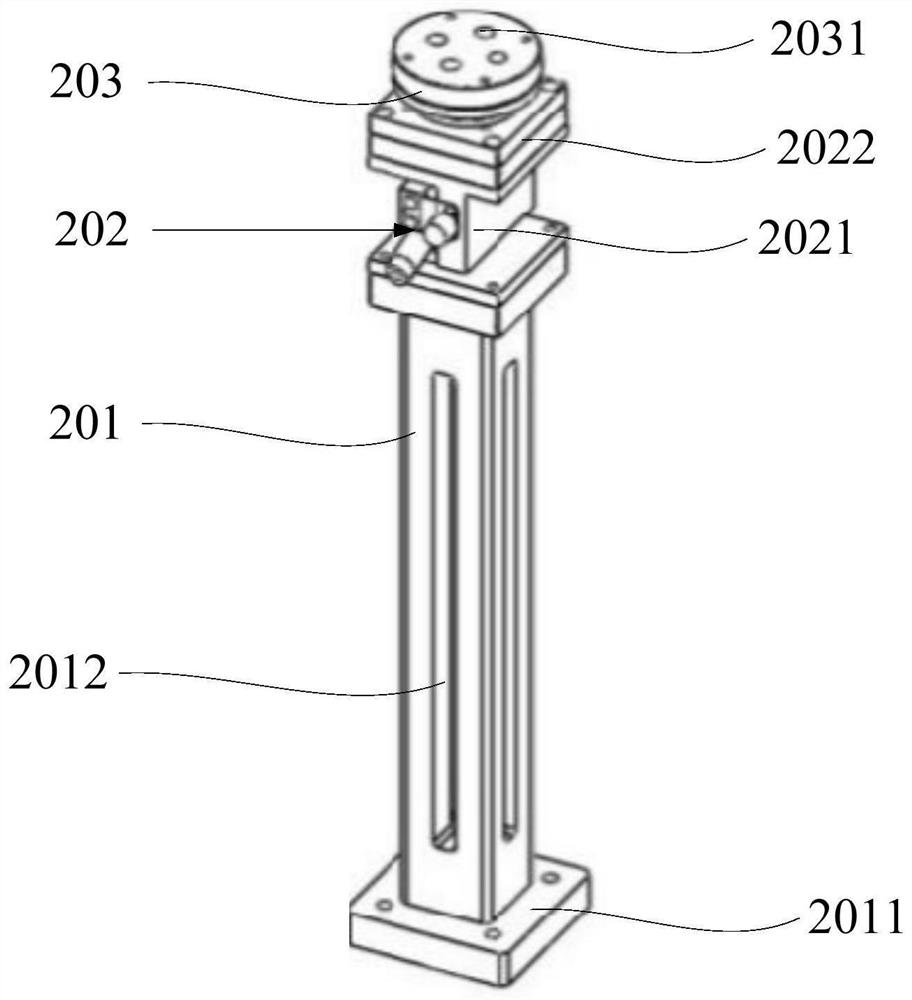

[0048] see figure 1 and figure 2 As shown, the embodiment of the present application provides a chip splicing platform, including:

[0049] Splicing the substrate 1 to form a splicing surface for supporting the chip;

[0050] The leveling component is connected with the splicing base plate 1, and the leveling component has a retractable structure, and the leveling component is used to support the splicing base plate 1 and adjust the flatness of the splicing surface.

[0051]The chip splicing platform provided by this application includes a splicing base plate 1 and a leveling component, wherein the splicing base plate 1 is formed with a splicing surface for supporting chips, and the splicing of the chip is completed on the splicing surface, and the leveling component is in phase with the splicing base plate 1 The connection, the leveling component can support the splicing base plate 1, the part of the leveling component has a retractable structure, and the height of the lev...

Embodiment 2

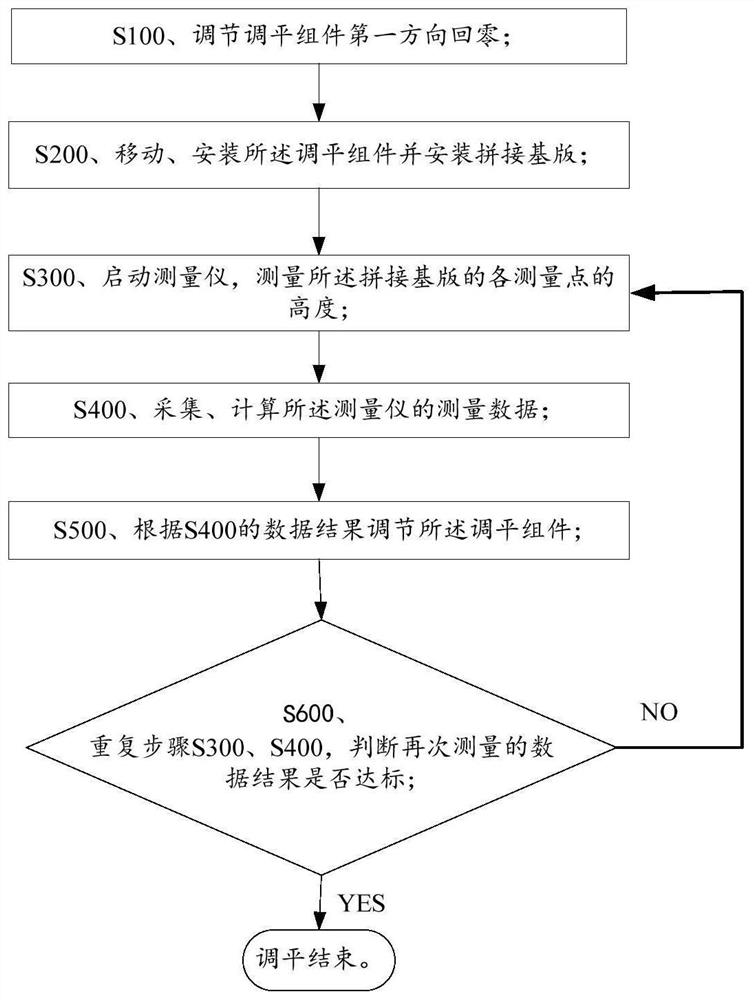

[0079] see image 3 As shown, Embodiment 2 of the present application also provides a chip splicing substrate leveling method, using the chip splicing platform described in the above-mentioned Embodiment 1, therefore, it has all the beneficial technical effects of the chip splicing platform, and the same technical features And the beneficial effects will not be repeated.

[0080] The chip splicing substrate leveling method provided in this embodiment specifically performs the following steps:

[0081] S100. Adjust the leveling assembly to return to zero in the first direction;

[0082] Specifically, select an appropriate number of leveling units according to the size of the splicing substrate, and restore the driving end of the driving device of each leveling unit of the adjustment assembly to the initial position, so that the self-adaptive leveling module is in the initial state, so that the leveling assembly is in the initial state. The lifting amount in the third directio...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More