Semiconductor assembly and manufacturing method thereof

A manufacturing method and semiconductor technology, applied in semiconductor devices, semiconductor/solid-state device components, electric solid-state devices, etc., can solve the problems of multi-chip area, occupancy, yield loss, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

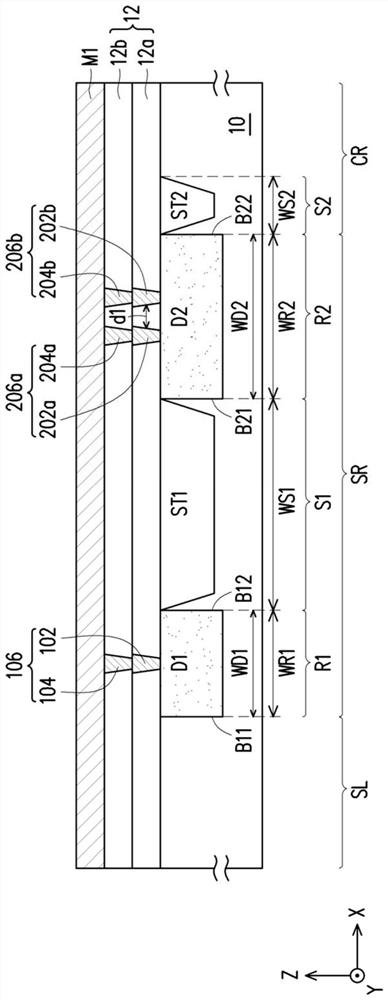

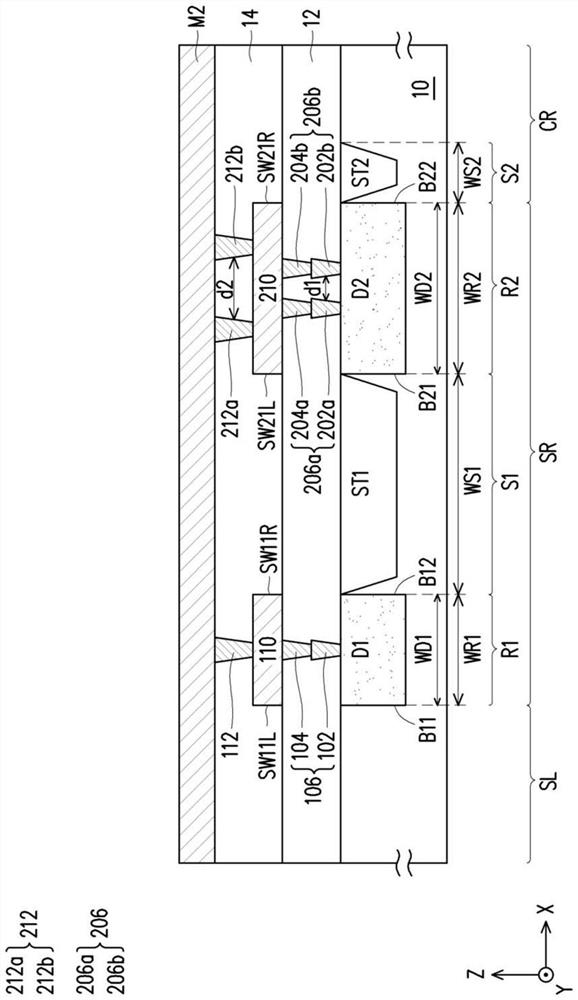

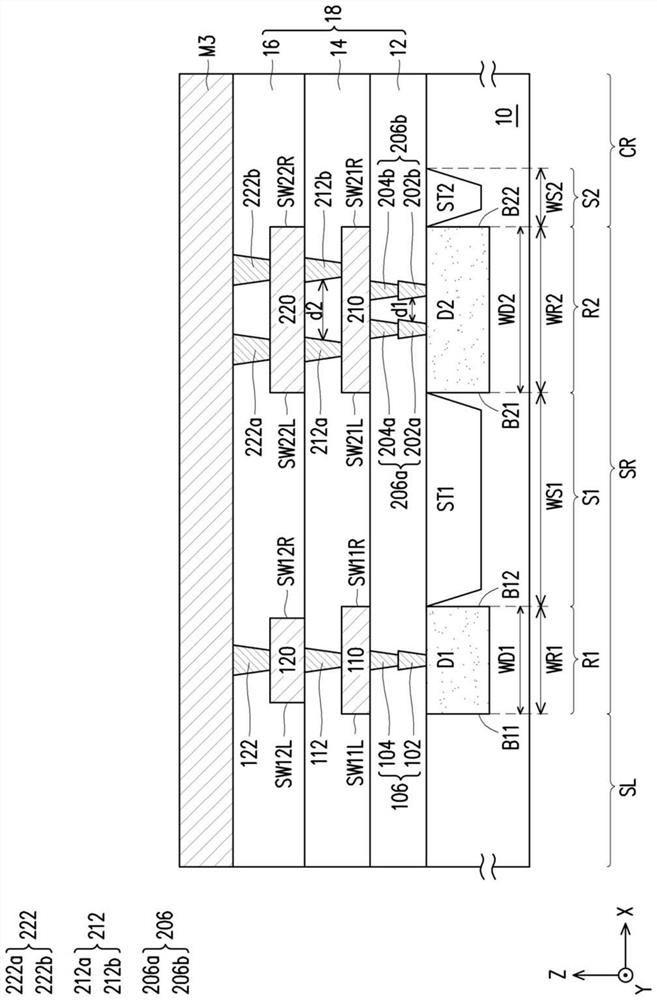

[0024] Please refer to Figure 1A , providing a substrate 10 . The substrate 10 may be a semiconductor substrate 10 . The substrate 10 may include a chip region CR, a seal ring region SR and a cutting region SL. The chip region CR may be used to form electronic components. The cutting area SL surrounds the chip area CR. During the subsequent singulation step, cleavage can be performed along the cleavage zone SL. The seal ring area SR is located between the chip area CR and the cutting area SL. A sealing ring can be formed in the sealing ring region SR, and can prevent the cracks generated by dicing the wafer from extending to the chip region CR and damaging the electronic components in the chip region CR during the subsequent singulation step.

[0025] A plurality of isolation structures ST1 and ST2 are formed in the chip region CR and the sealing ring region SR. The isolation structure is, for example, a shallow trench isolation structure.

[0026] The width WS1 of the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More