Patents

Literature

31results about How to "Improve ladder coverage" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

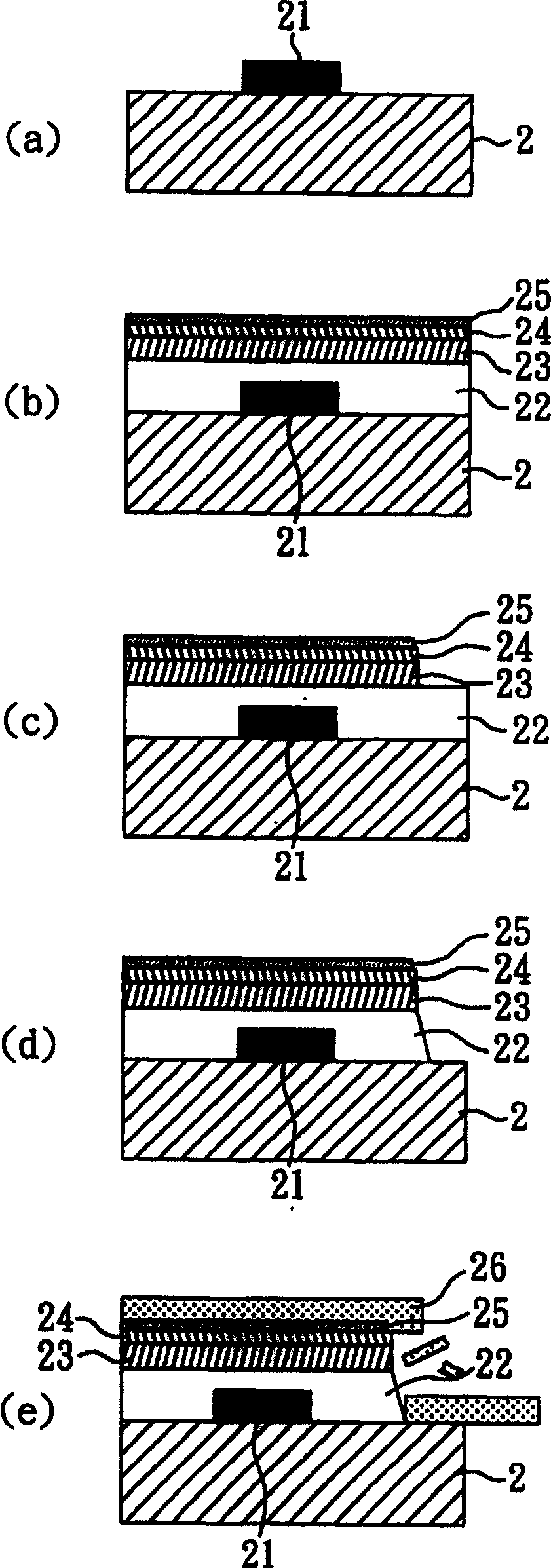

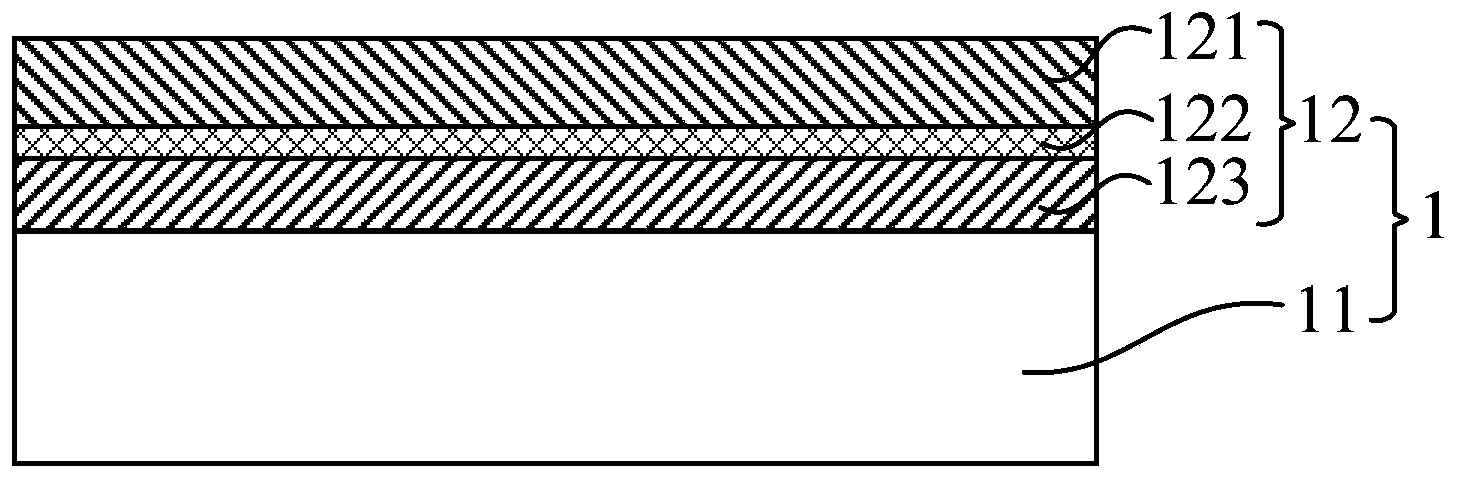

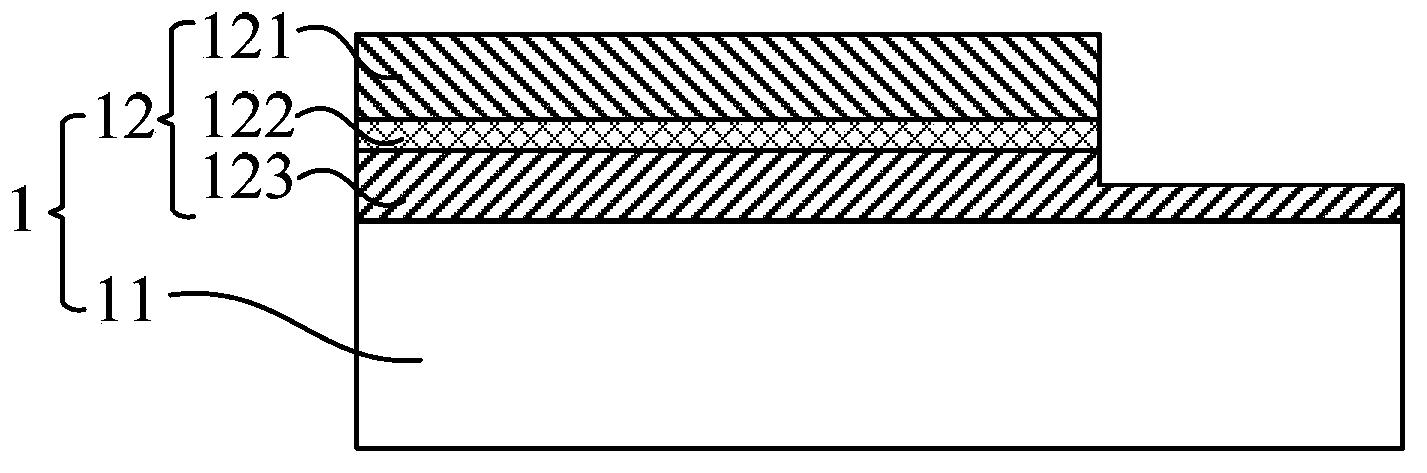

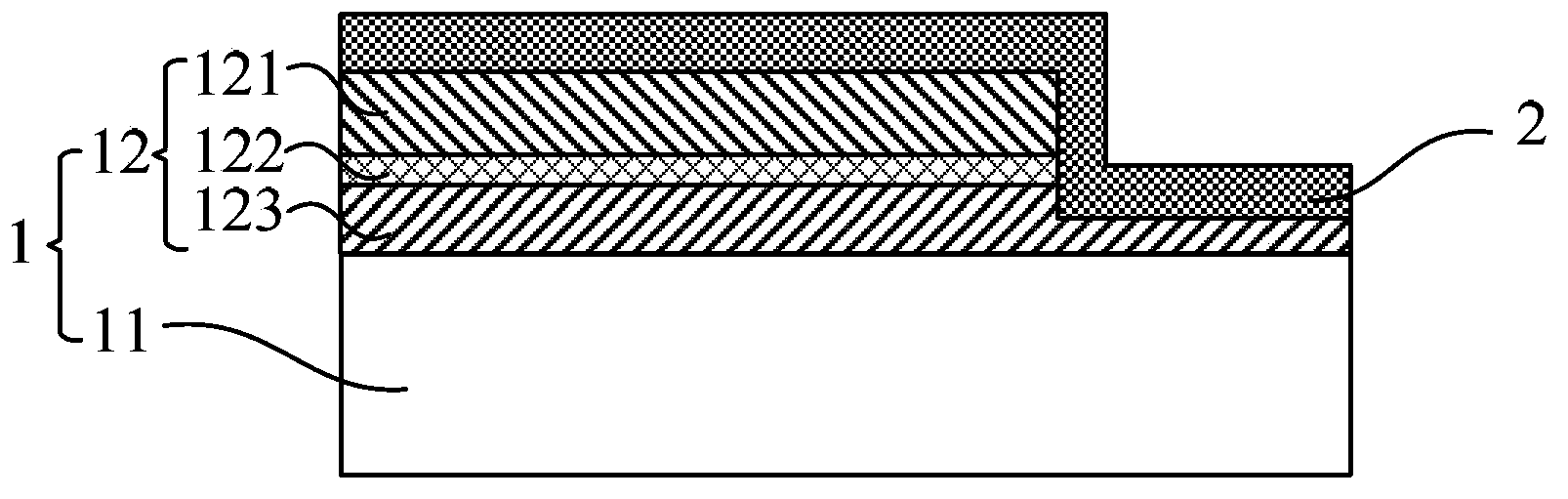

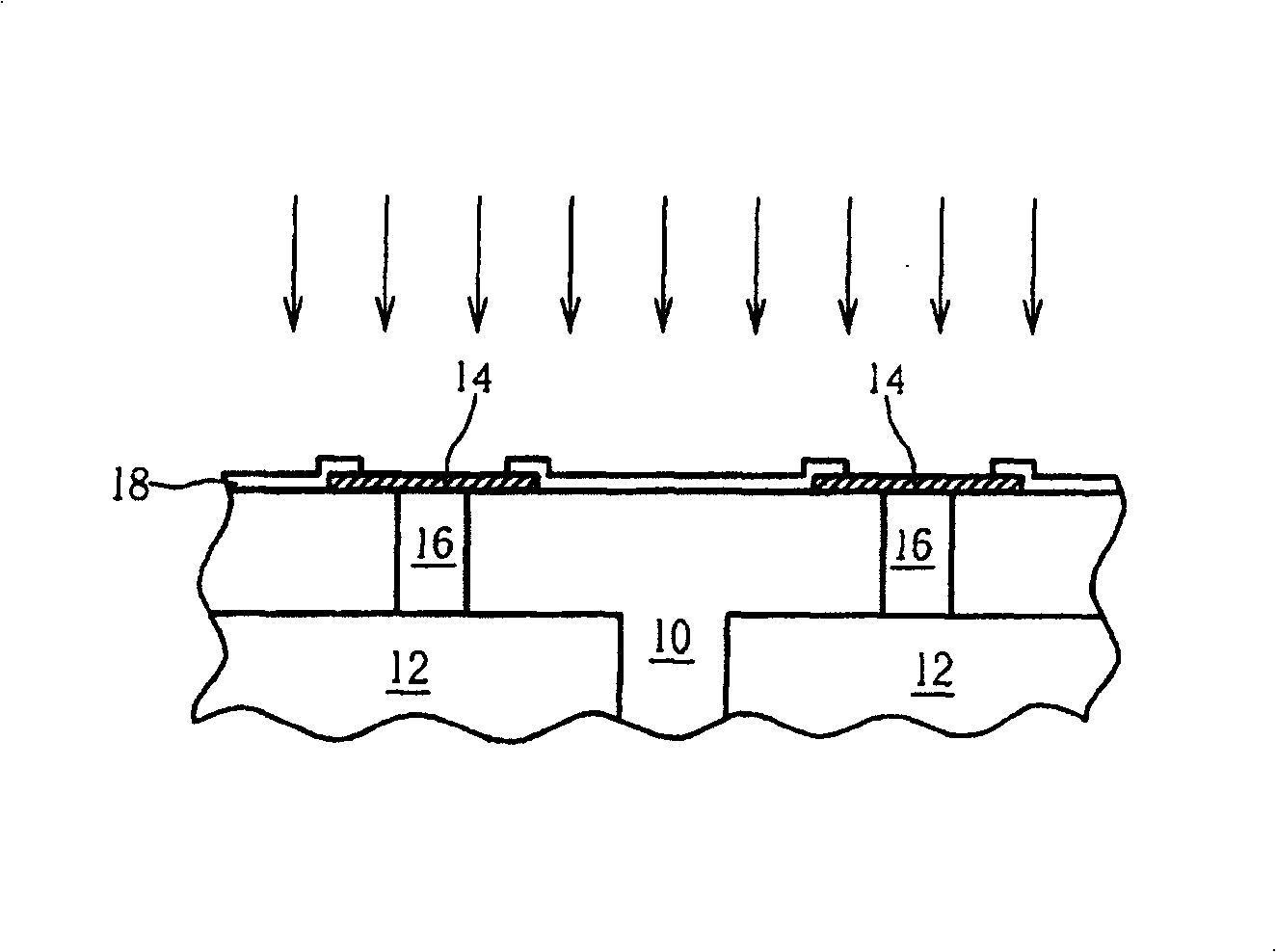

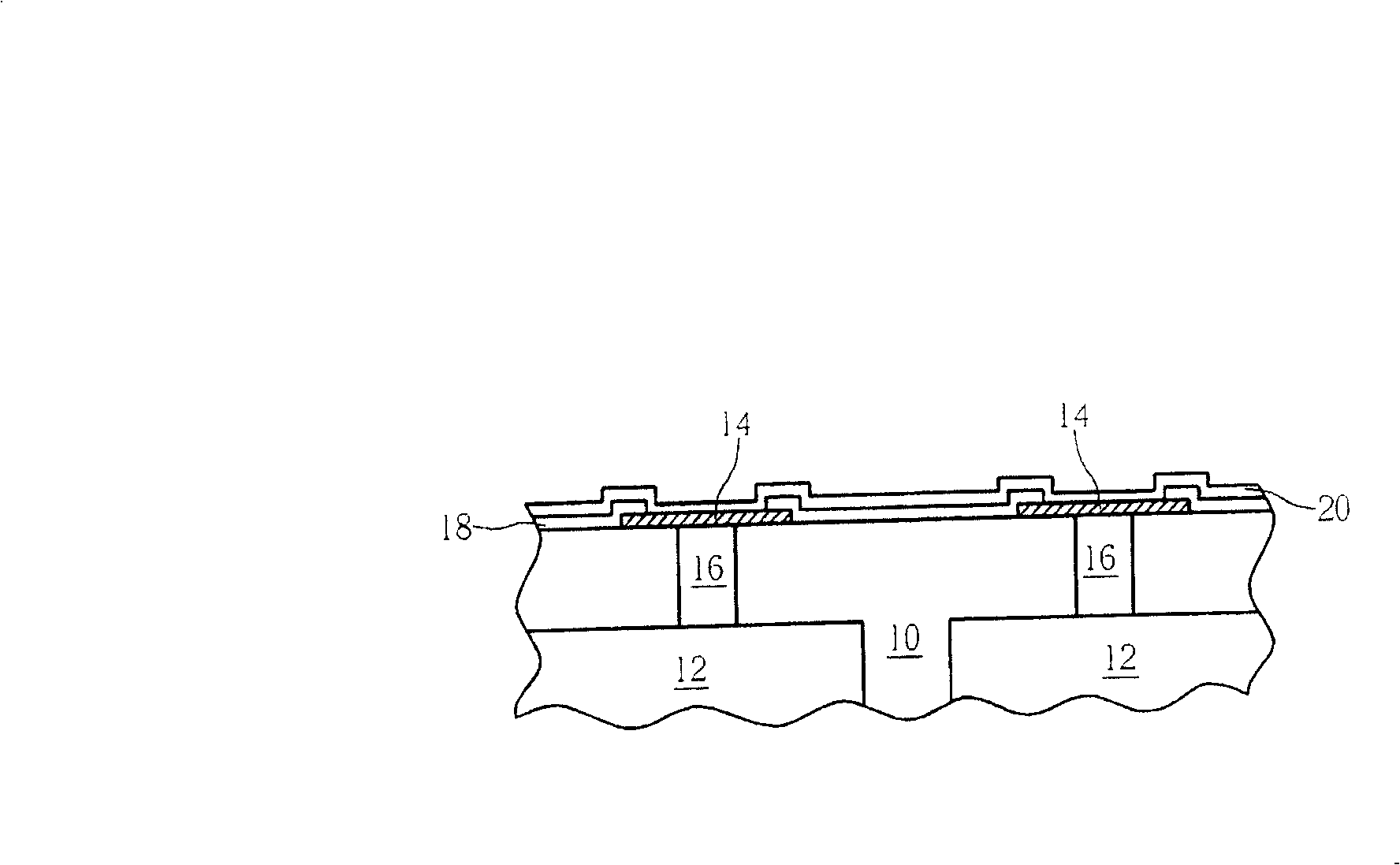

LED (Light Emitting Diode) chip provided with stepped current blocking structure and fabricating method thereof

ActiveCN102751410AImprove electro-optical conversion efficiencyIncrease brightnessSemiconductor devicesPower flowEngineering

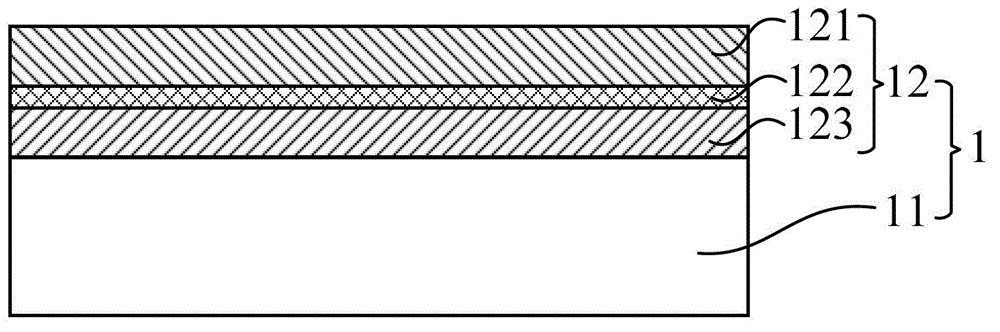

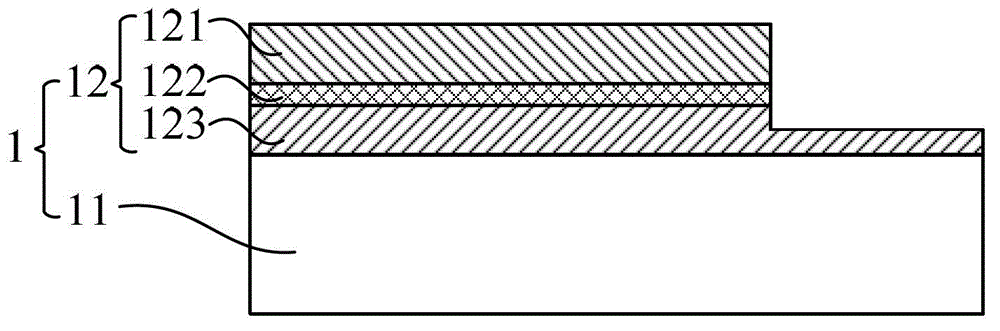

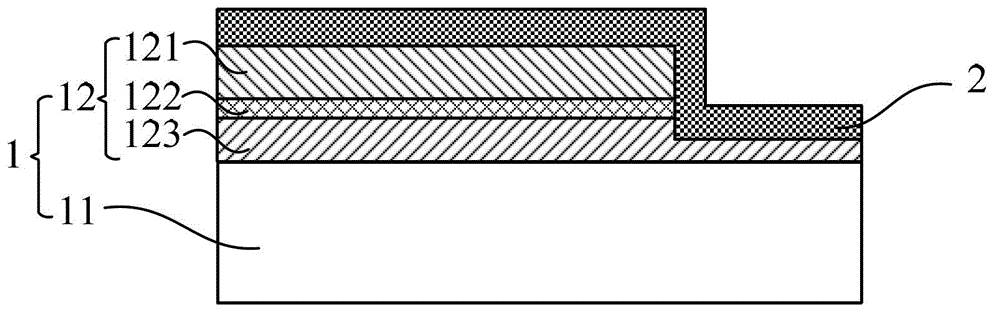

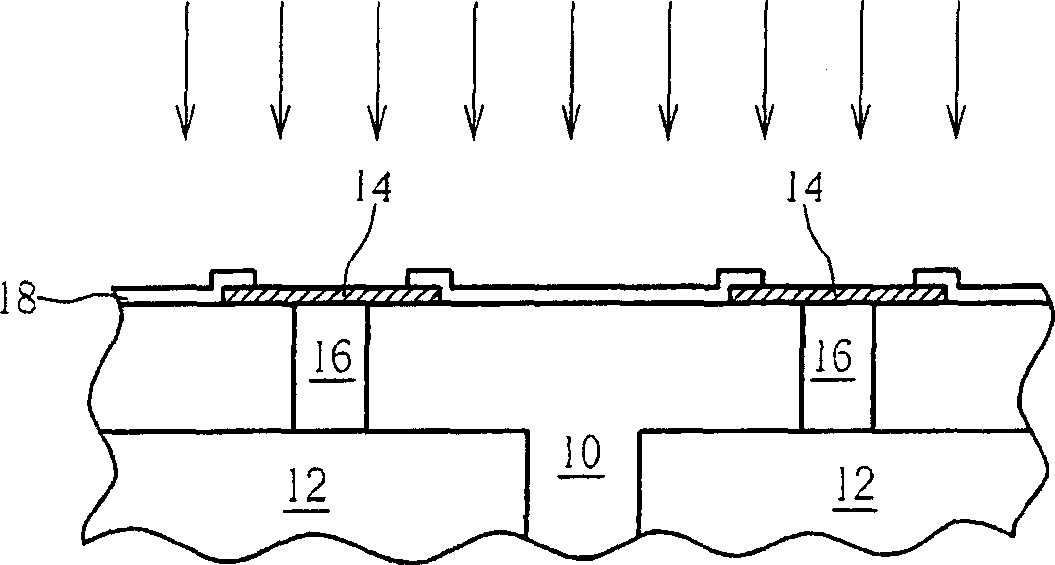

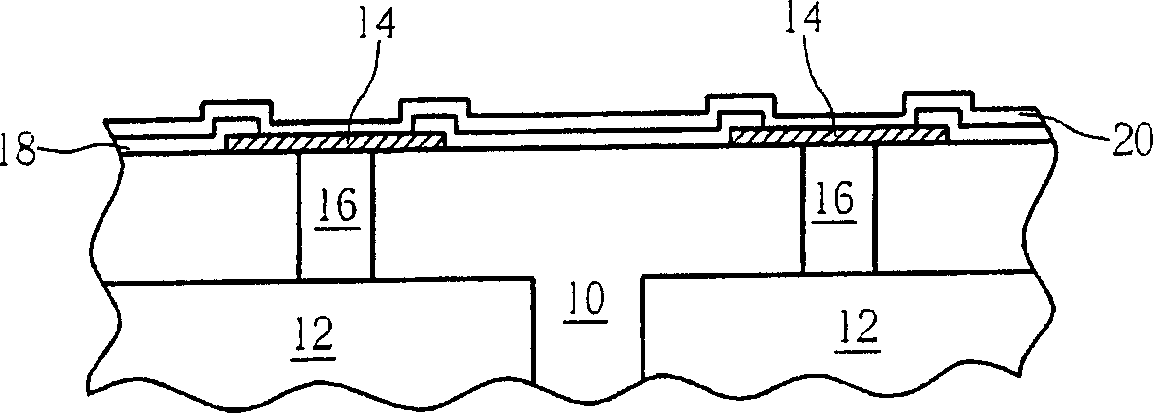

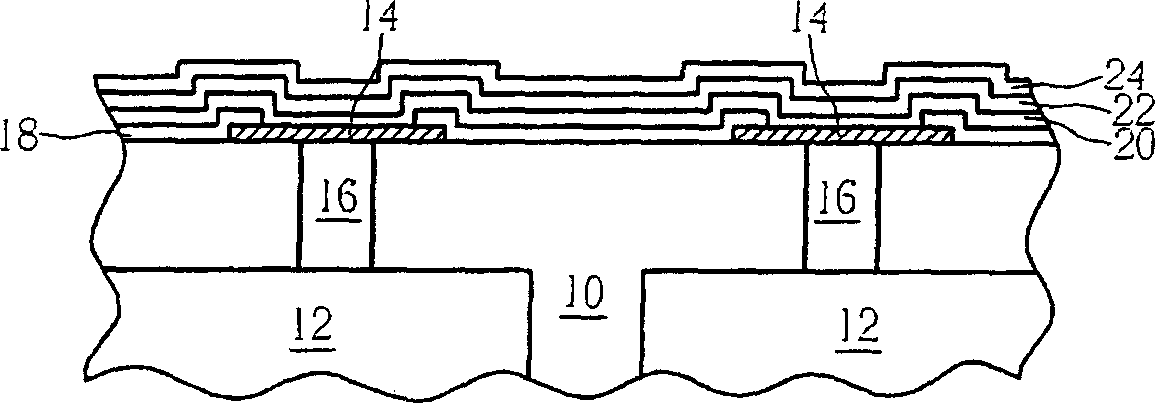

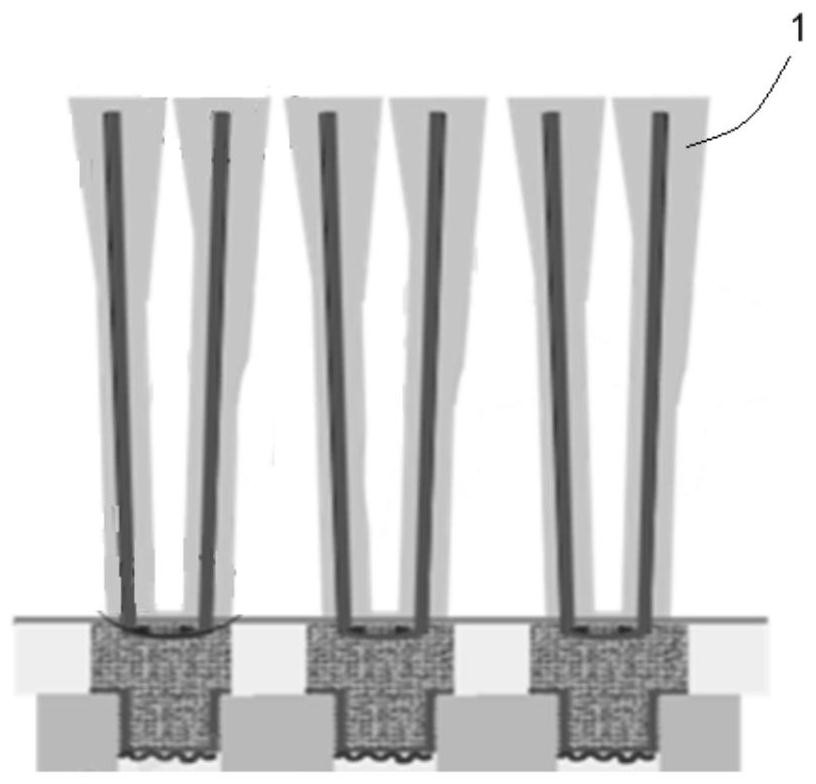

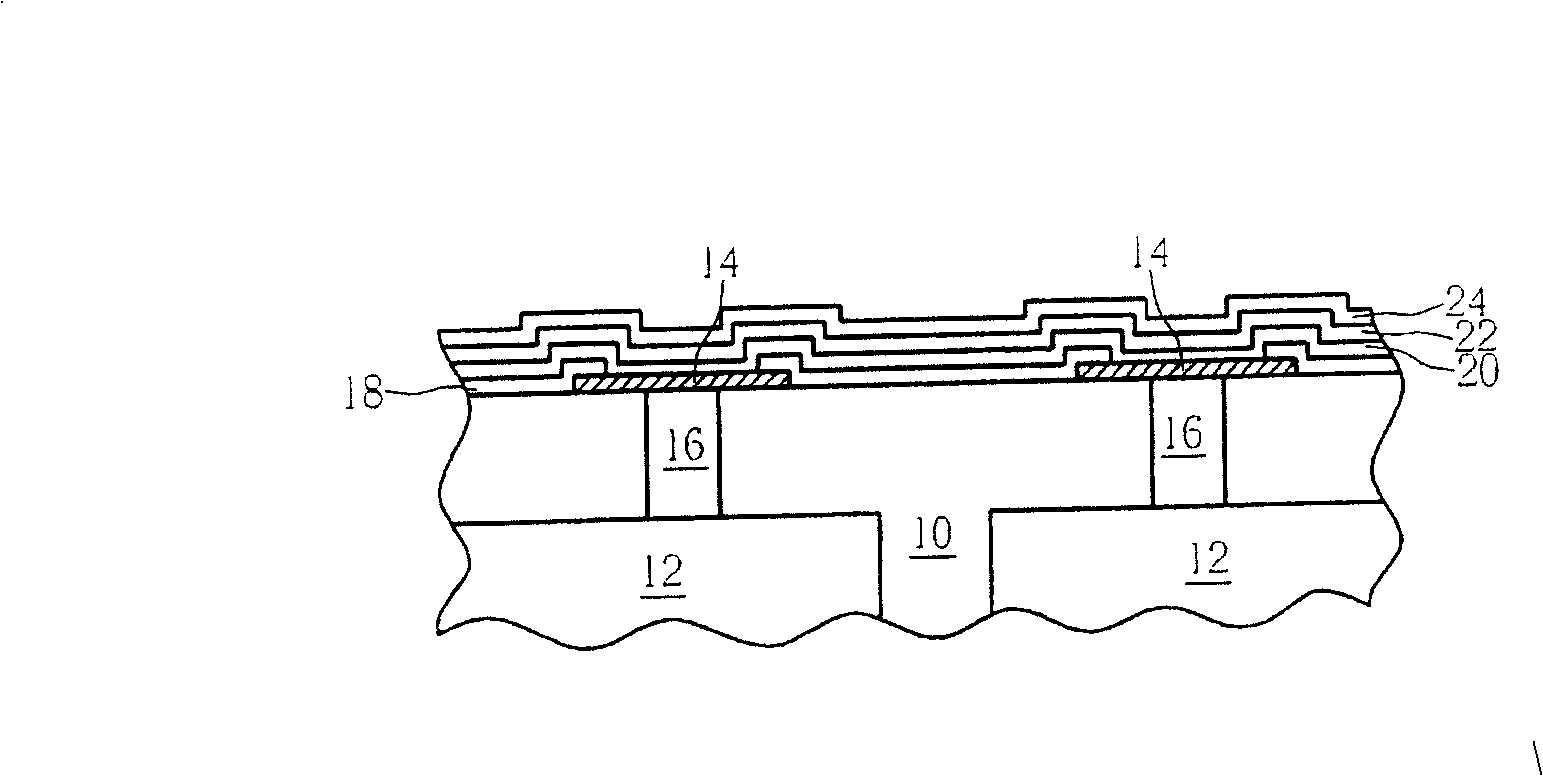

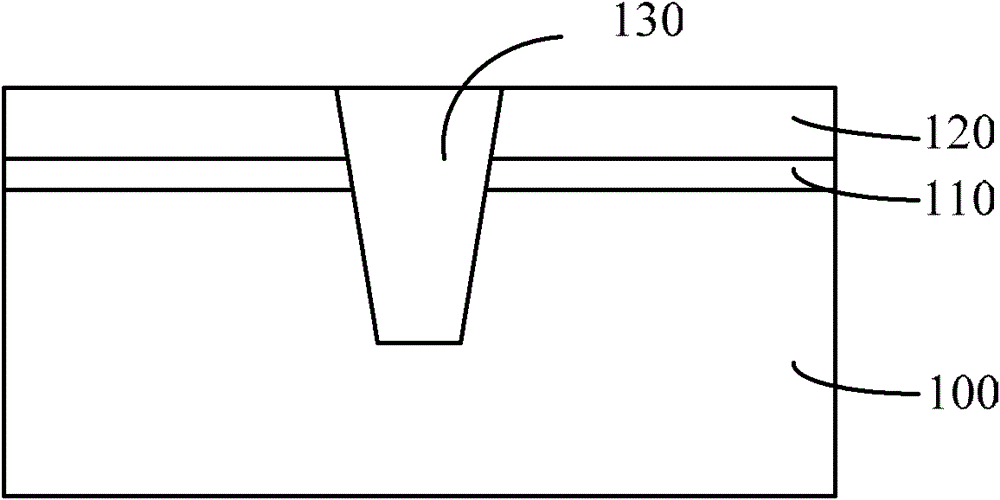

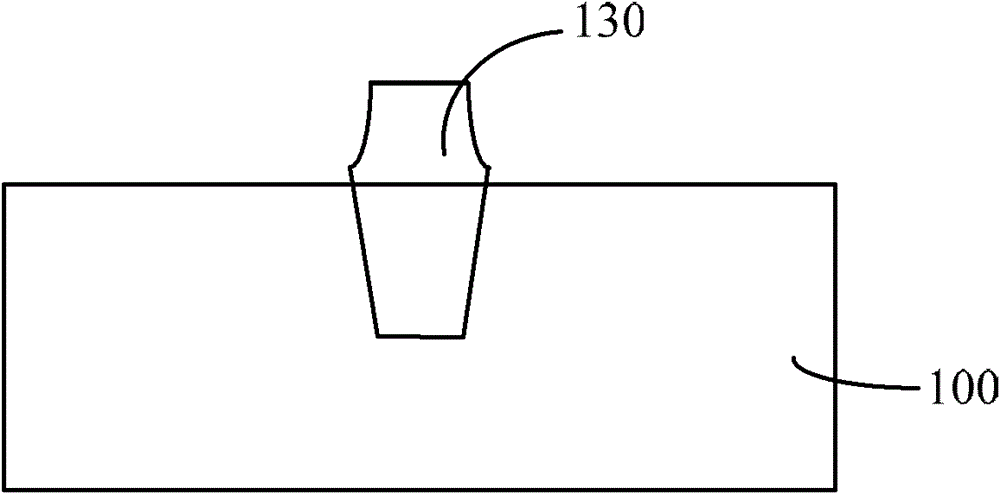

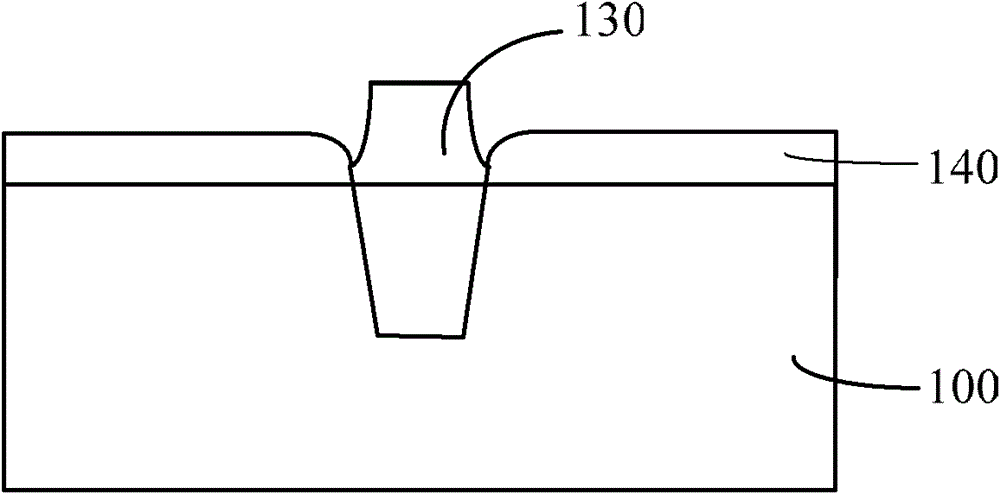

The invention provides an LED (Light Emitting Diode) chip provided with a stepped current blocking structure and a fabricating method thereof. The fabricating method comprises the steps of: providing at least one LED epitaxial wafer comprising a substrate and a light emitting epitaxial structure on the LED epitaxial wafer; fabricating the stepped current blocking structure on the surface of the LED epitaxial wafer vertical to a region of a first electrode correspondingly prefabricated; and fabricating transparent conductive layers on the surfaces of the LED epitaxial wafer and the stepped current blocking structure, and then fabricating a first electrode, a second electrode and a protective layer correspondingly. According to the LED chip provided with a stepped current blocking structure and the fabricating method of the LED chip provided with the stepped current blocking structure provided by the invention, the gradient at the edge of the stepped current blocking structure is slowed so that the contact area of the transparent conductive layer and the stepped current blocking structure is increased, the situation that the transparent conductive layer (ITO) on the side wall (at the step) at the edge of the current blocking structure becomes thinner and even breaks can be avoided, the step covering capacity of the transparent conductive layer is improved, the current spreading capacity of the transparent conductive layer is further improved, the electro-optical conversion efficiency of the LED chip is increased, and the brightness of the LED chip is enhanced.

Owner:宁波安芯美半导体有限公司

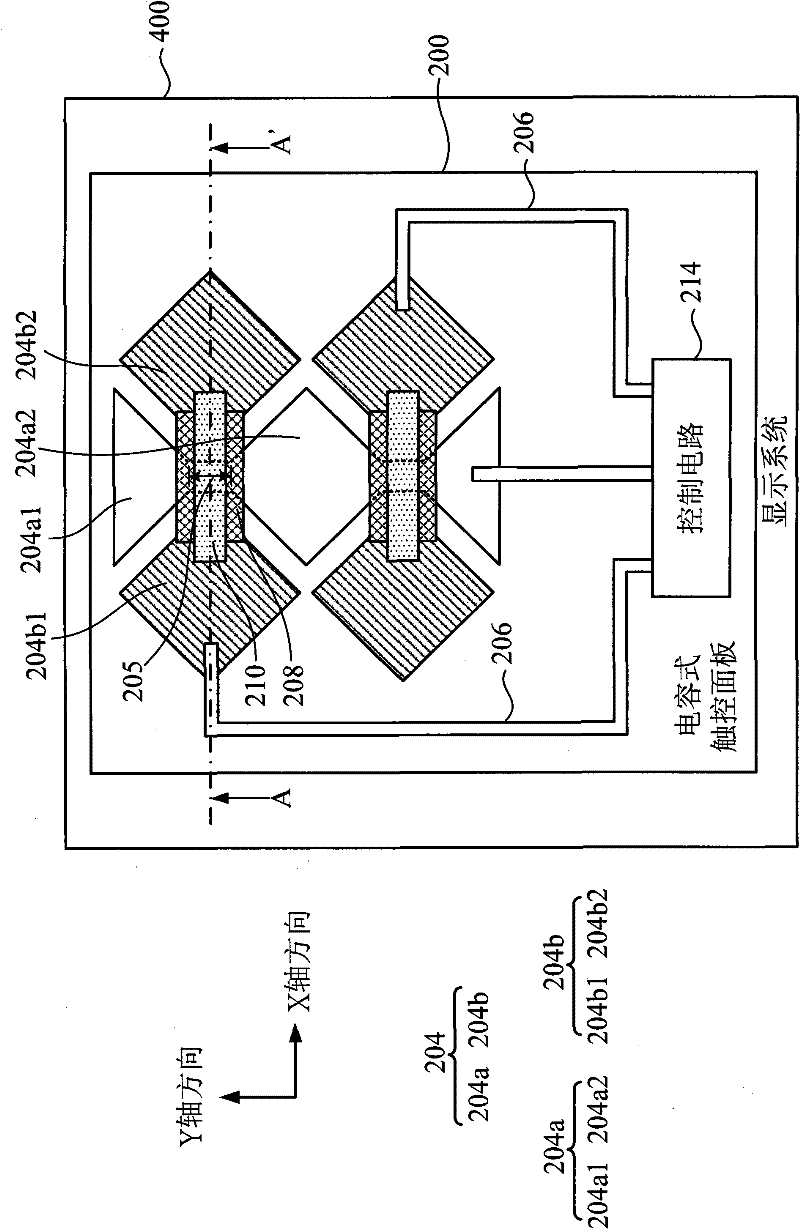

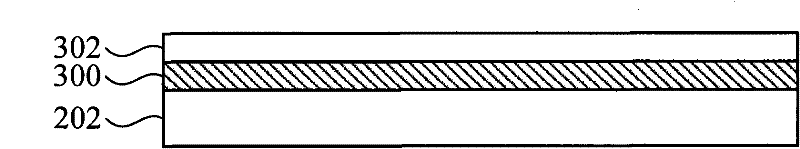

Display system with capacitive touch panel and manufacturing method thereof

InactiveCN102346609AThe overall thickness is thinImprove processing yieldInput/output processes for data processingEngineeringDielectric layer

The invention provides a display system with a capacitive touch panel and a manufacturing method thereof. The display system with a capacitive touch panel comprises a substrate, an electrode circuit, a plurality of signal lines, a dielectric layer and an electrode bridging structure, wherein the electrode circuit is provided with a first electrode and a second electrode, the first electrode comprises a plurality of first conductive patterns, the second electrode comprises a plurality of second patterns, and the first conductive patterns are mutually electrically connected; the plurality of signal lines are formed on the substrate; the dielectric layer is formed on the electrode circuit and covers the electrode circuit; and in the invention, the electrode bridging structure with uniform thickness is formed on the dielectric layer by using a metal open repair technique, so that the second patterns are mutually electrically connected.

Owner:INNOCOM TECH SHENZHEN +1

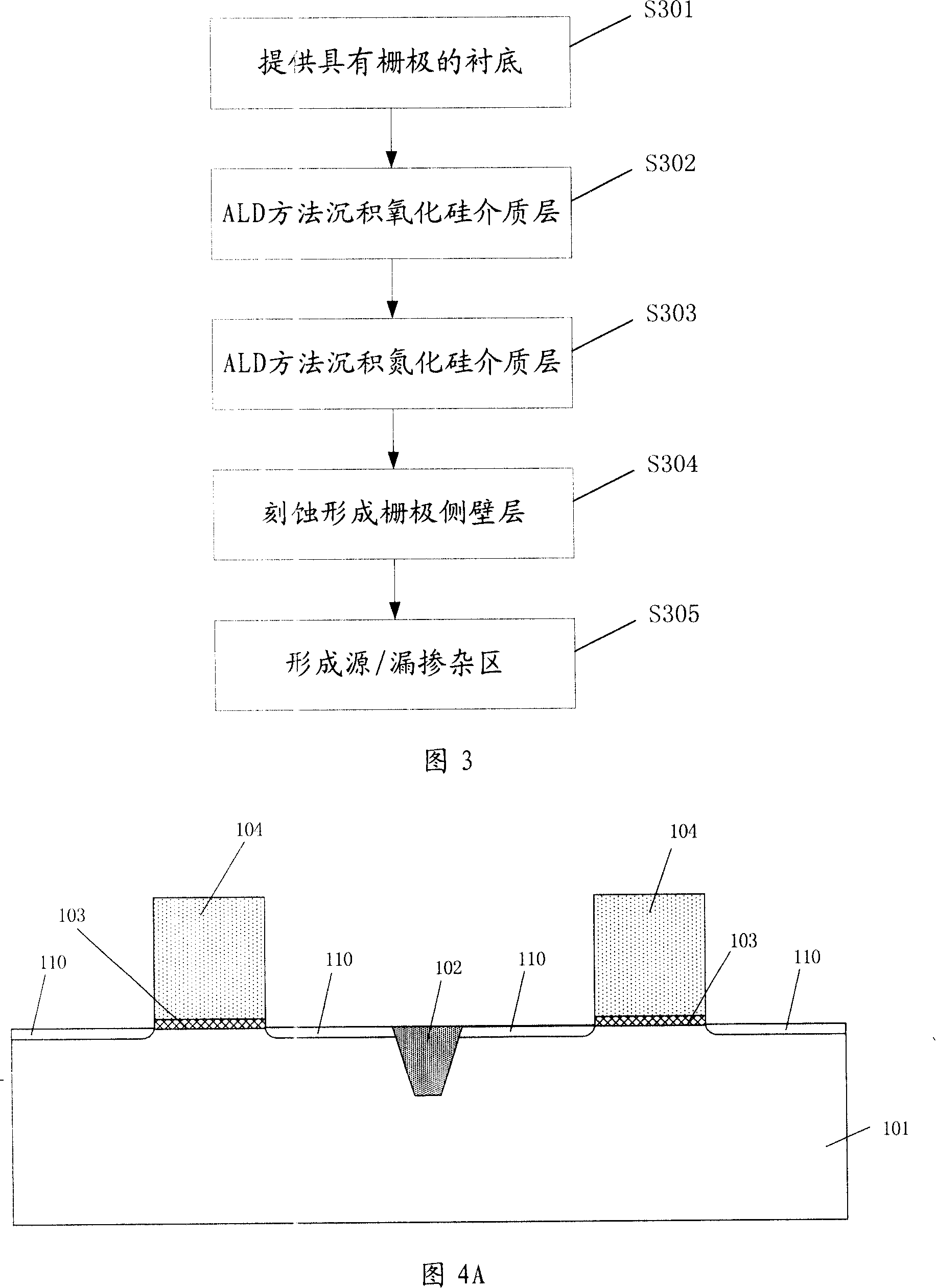

Method for forming grid side wall layer

ActiveCN101154571AProtectImprove thickness uniformitySemiconductor/solid-state device manufacturingSemiconductor devicesOptoelectronicsMedia layer

The invention discloses a method of forming a grid wall layer, including the following steps that: a substrate with at least a grid is provided; the method of atomic layer deposit is utilized to form a complex medium layer in the substrate; a side wall layer is formed in the grid by etching the complex dielectric layer. The invention is not only favorable to improve the performance of the parts with lower heat budgeting, but also improves the uniformity of the performance of the parts with better uniformity of the formed grid side wall layer.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

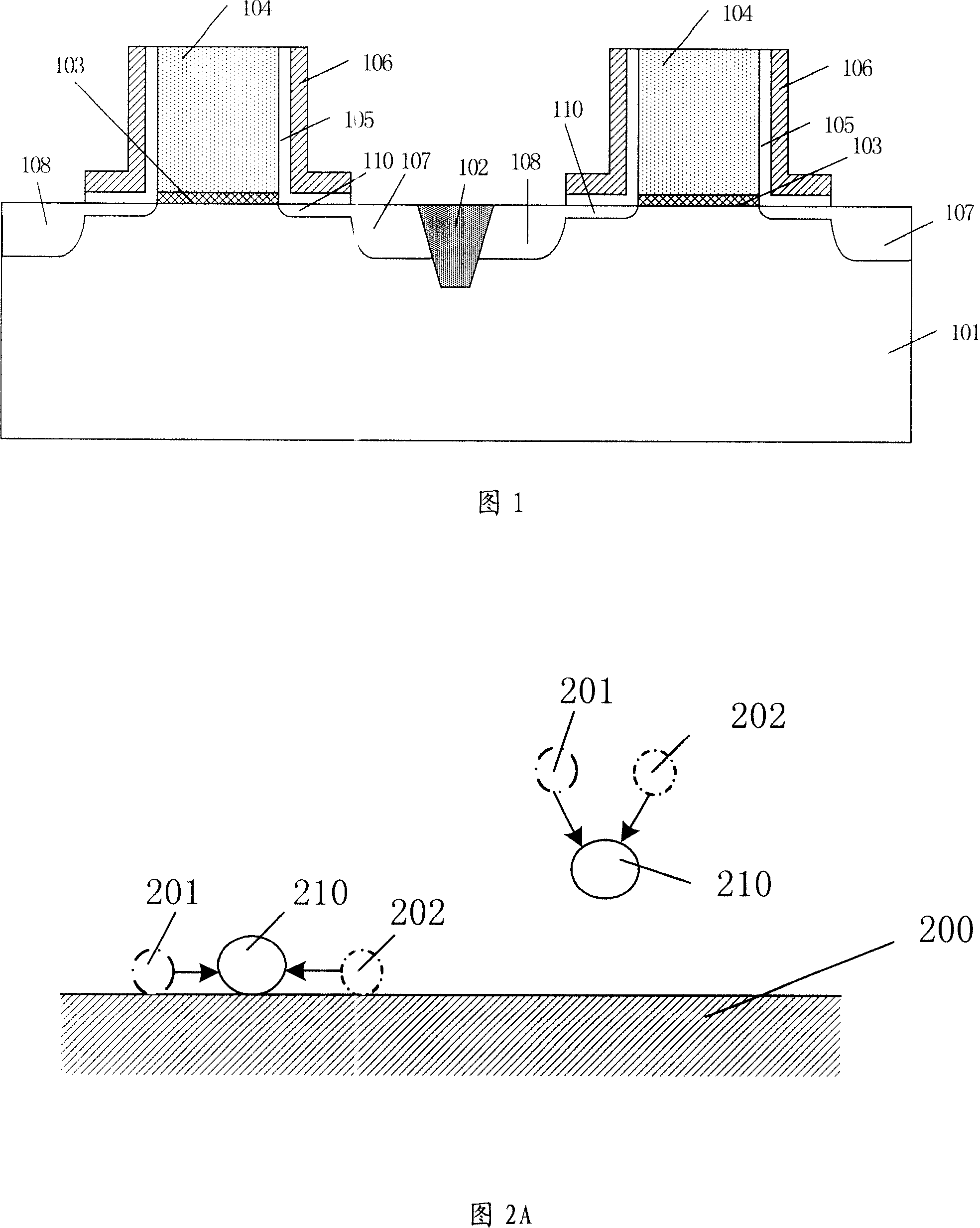

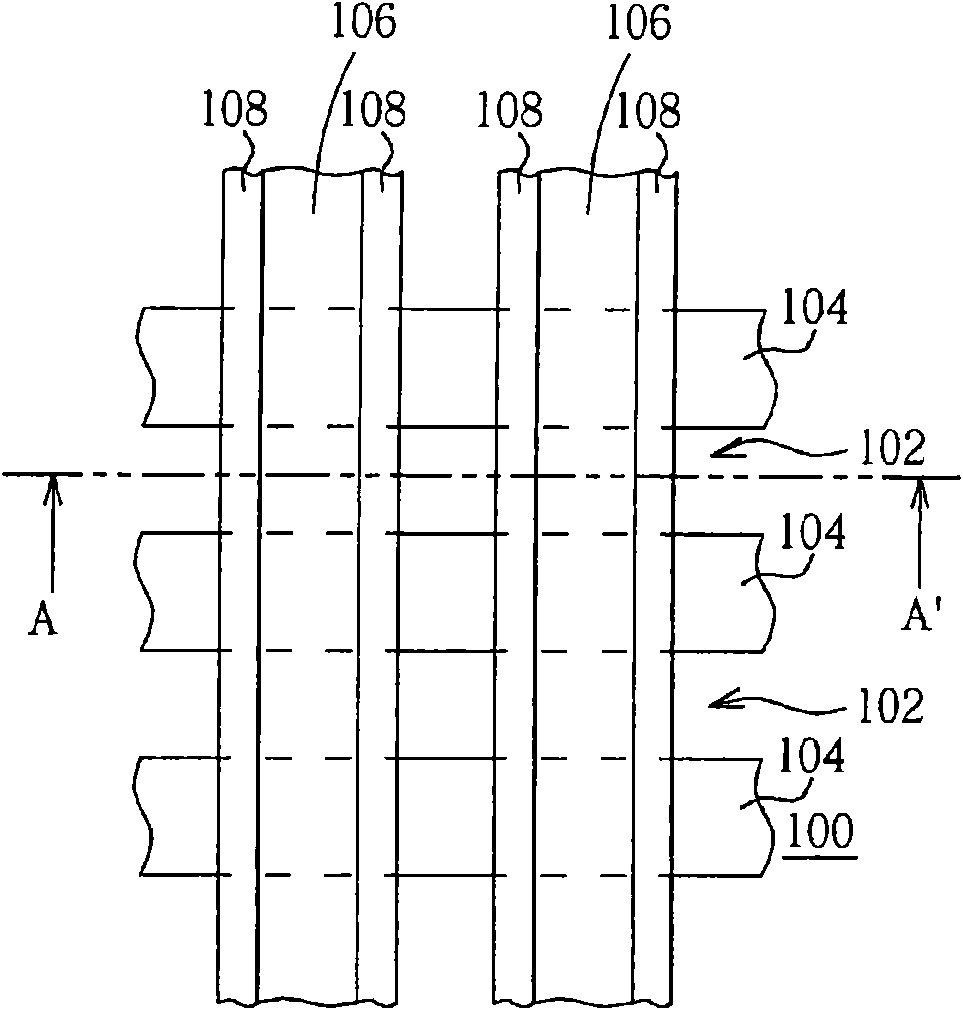

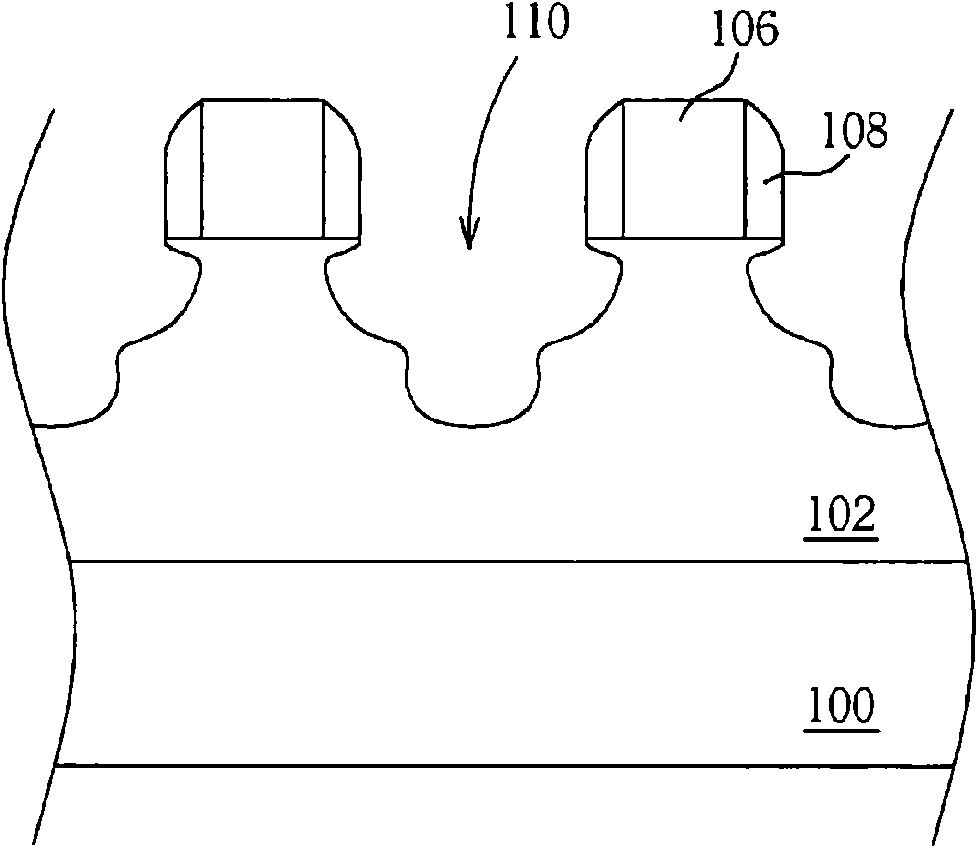

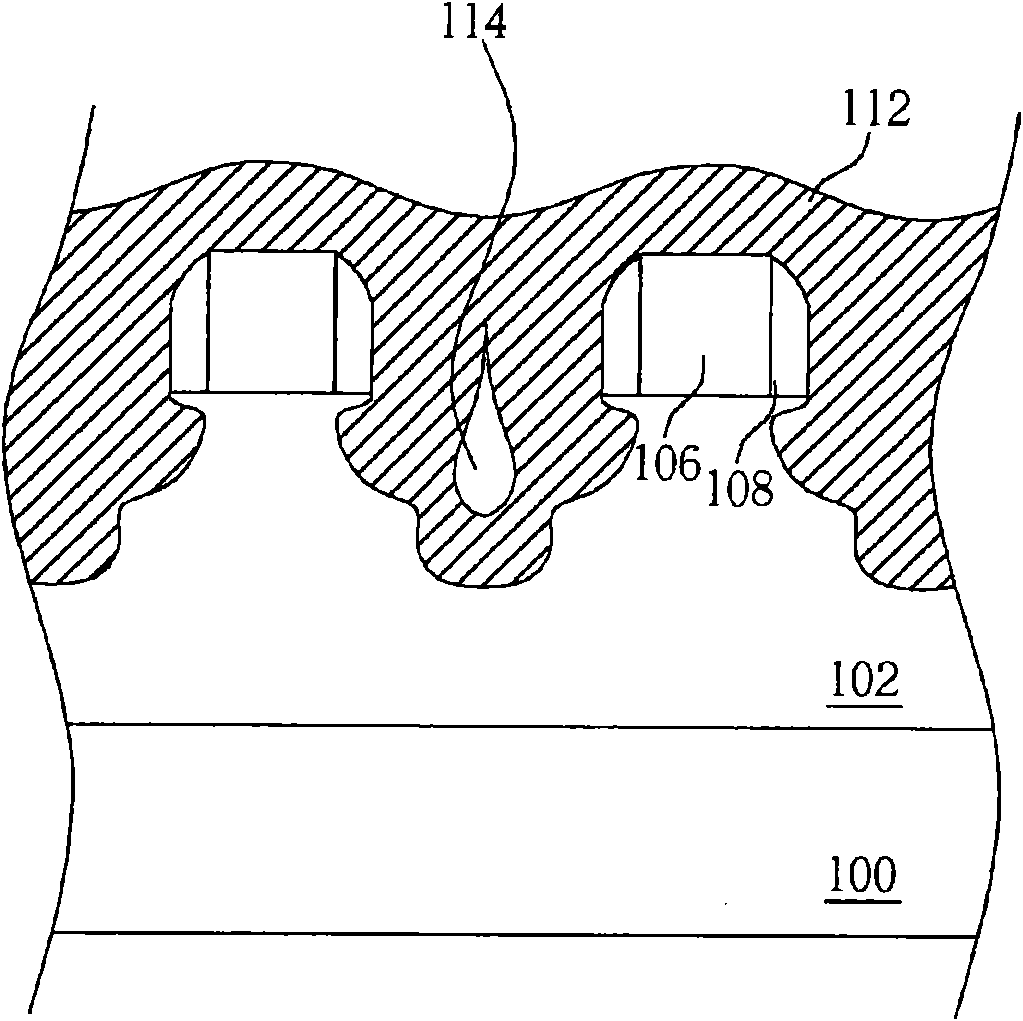

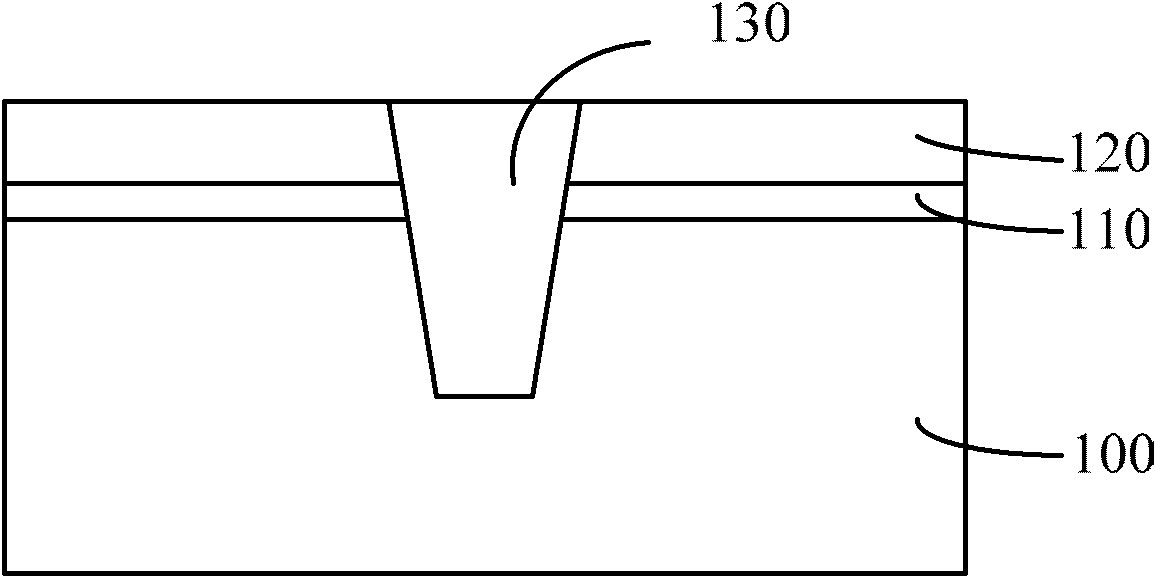

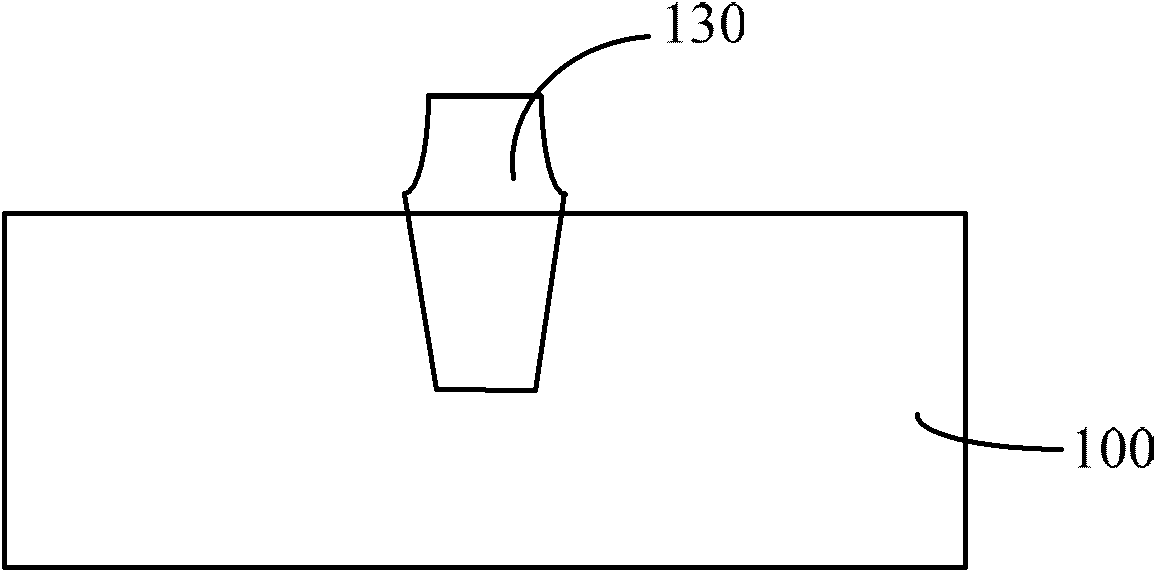

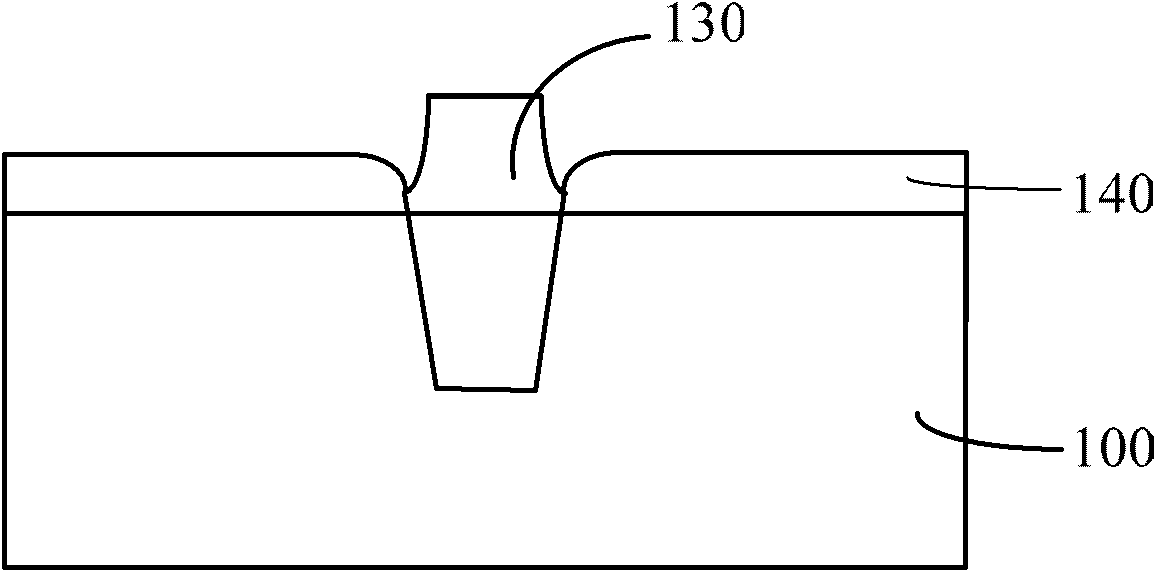

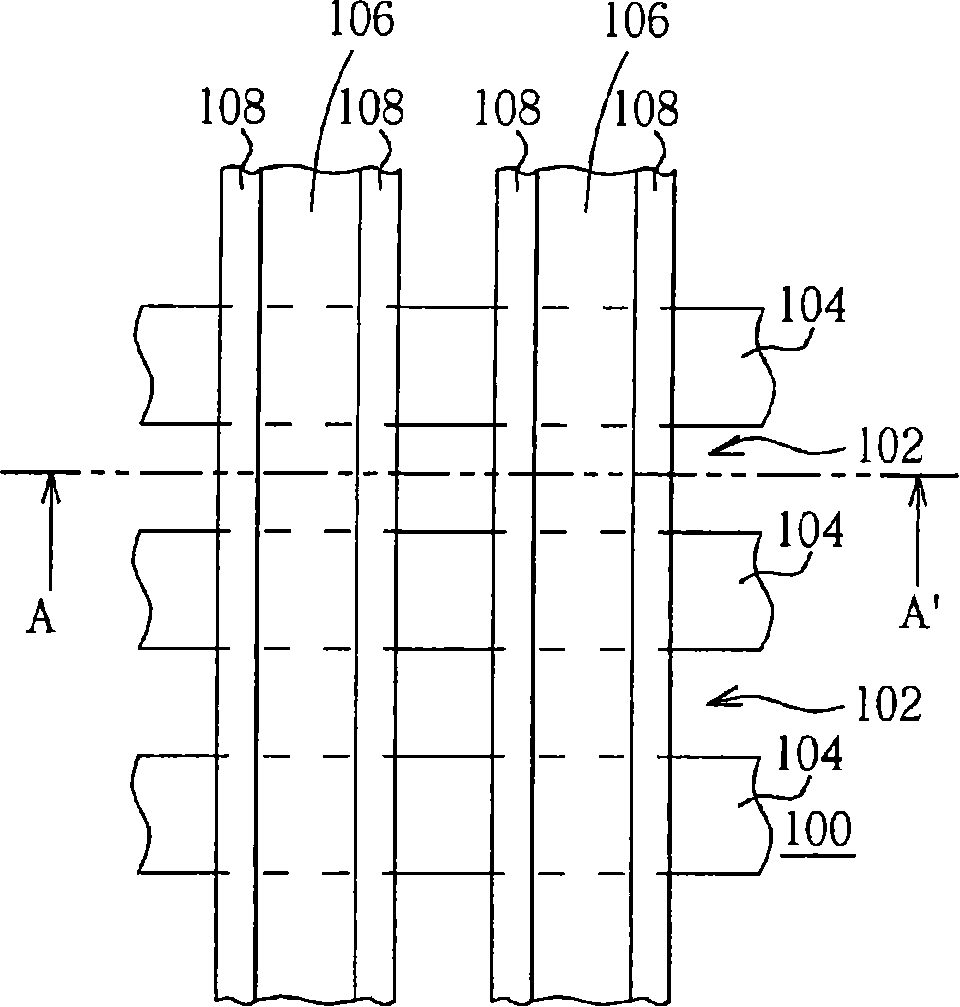

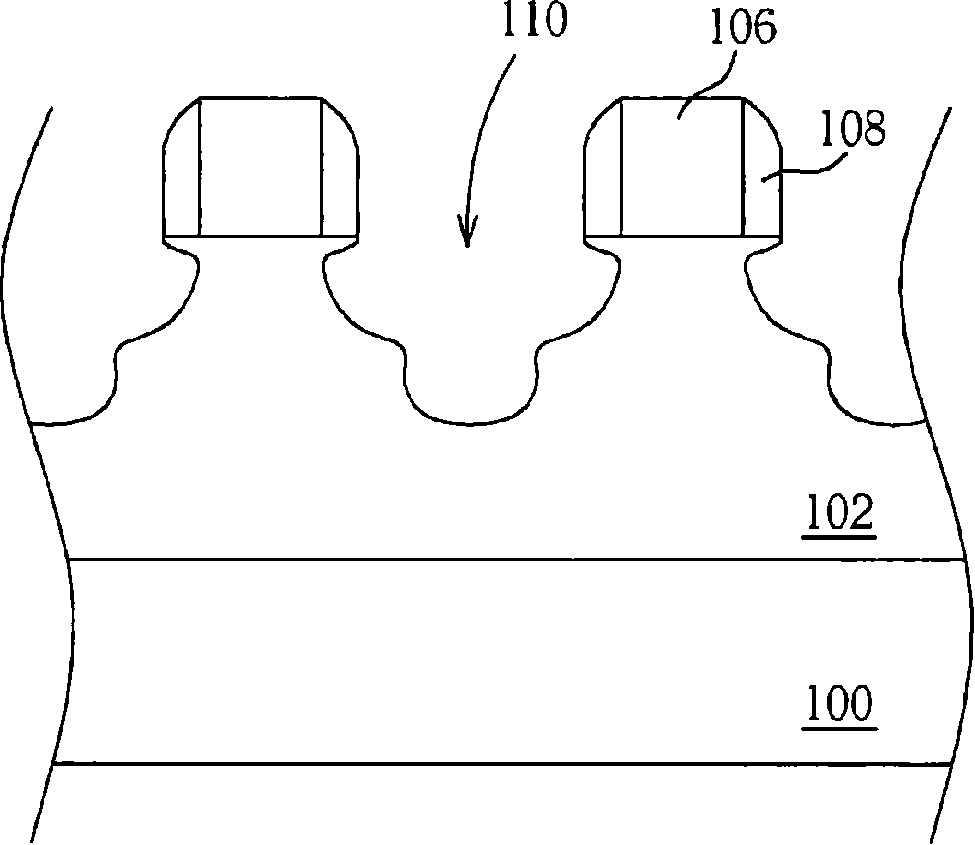

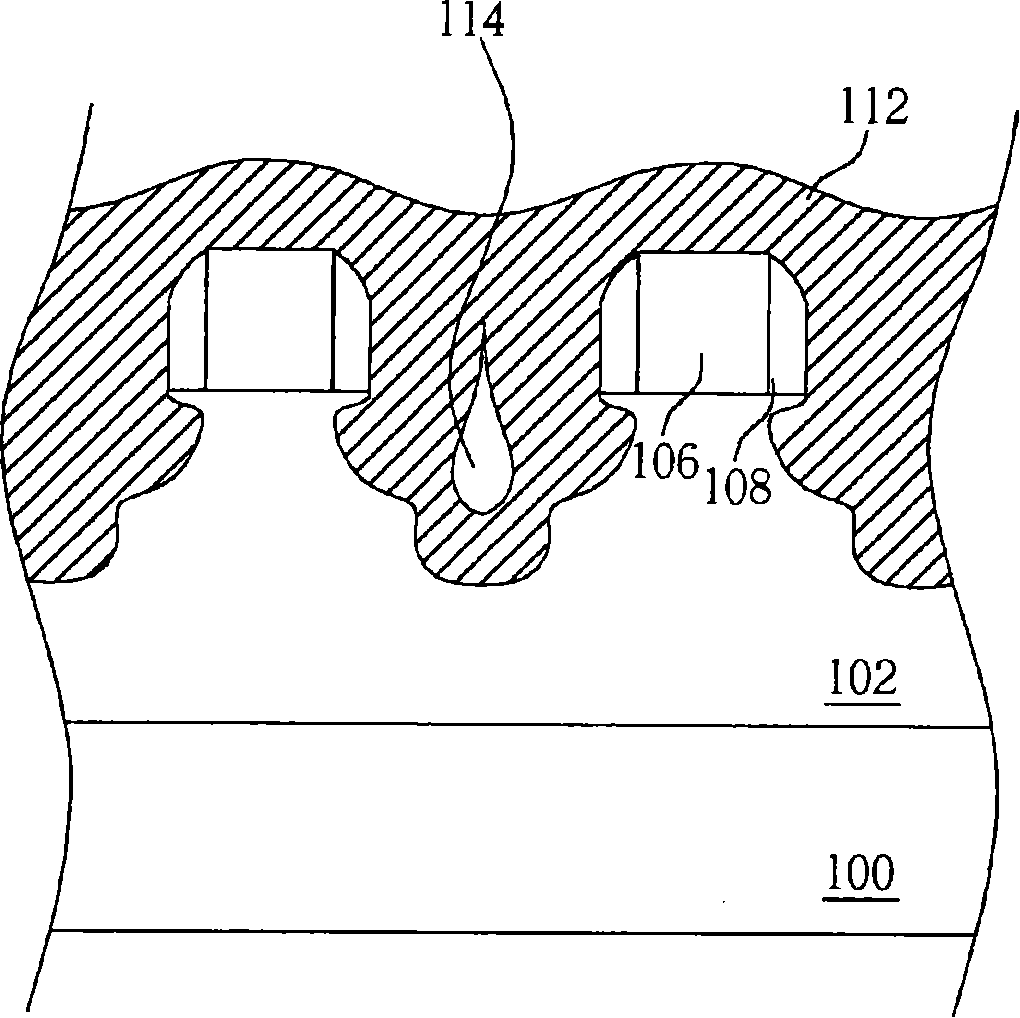

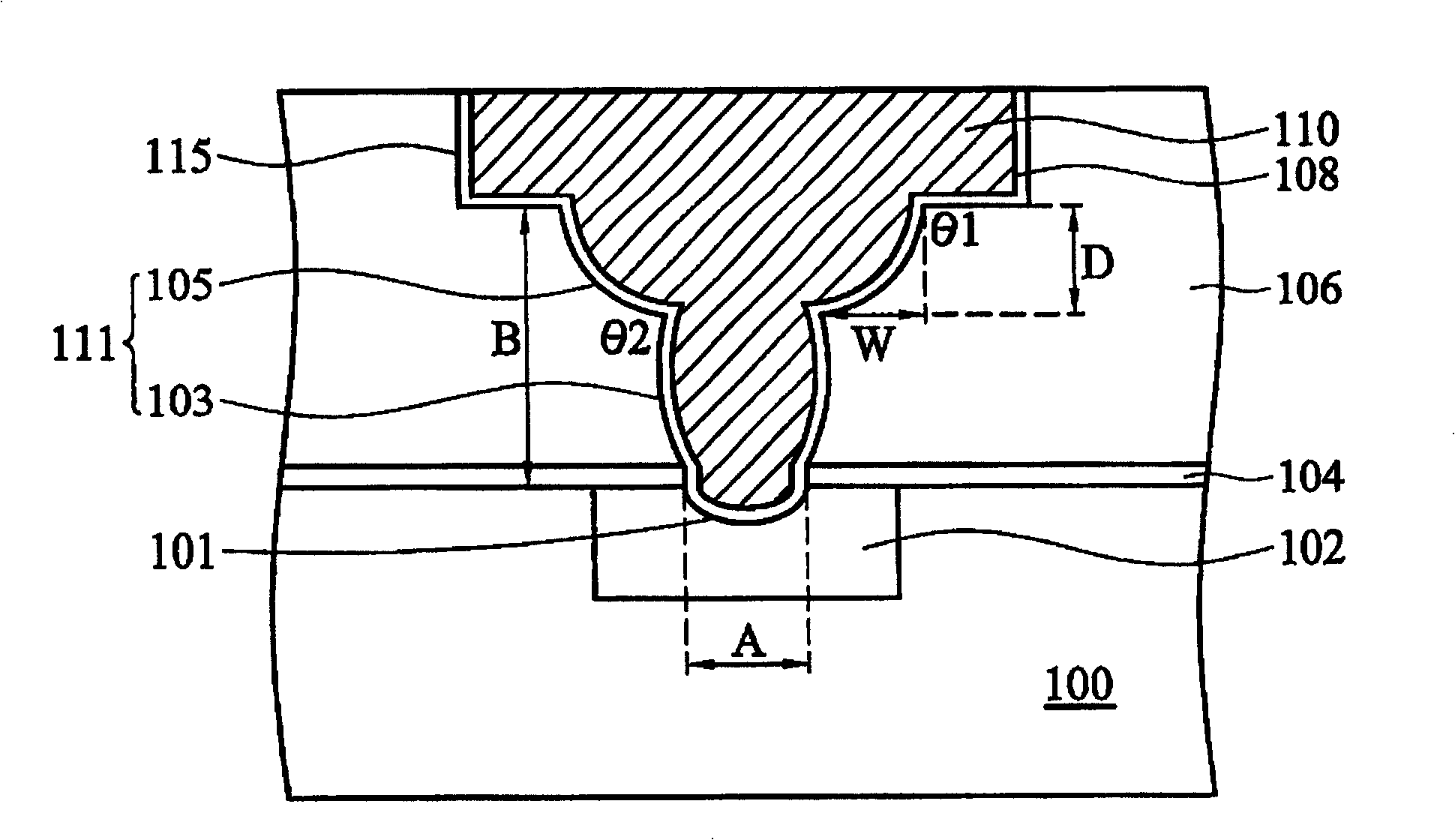

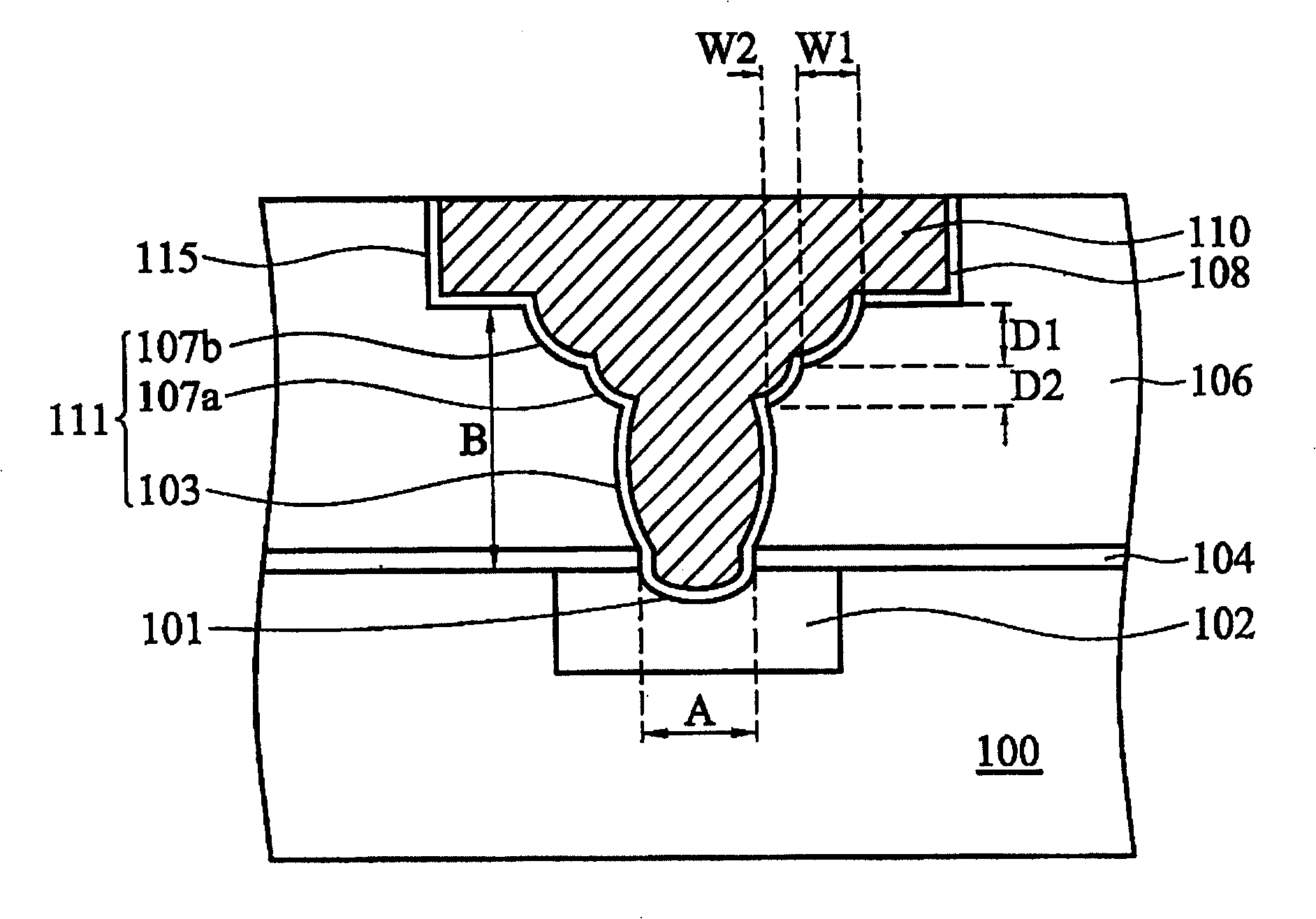

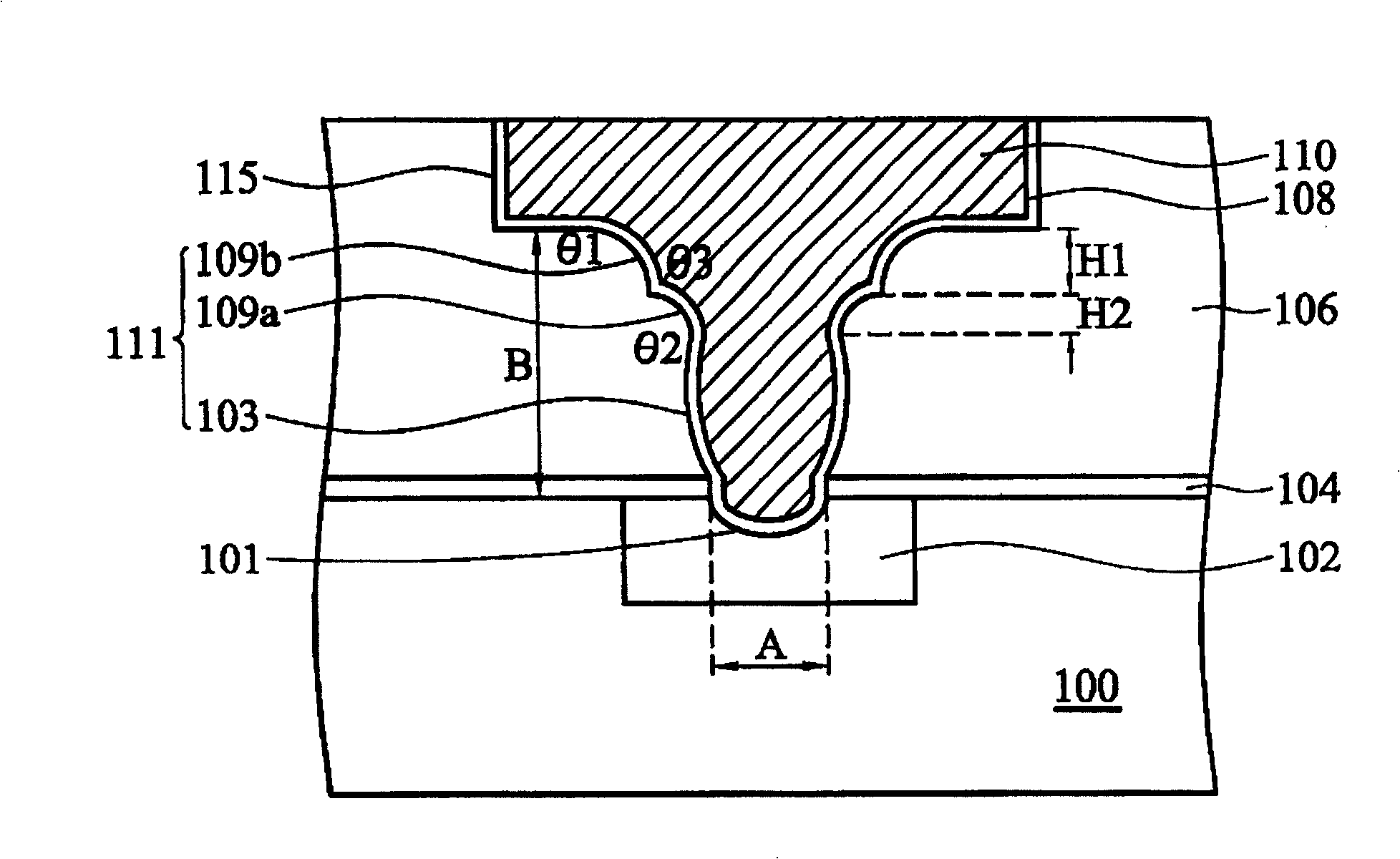

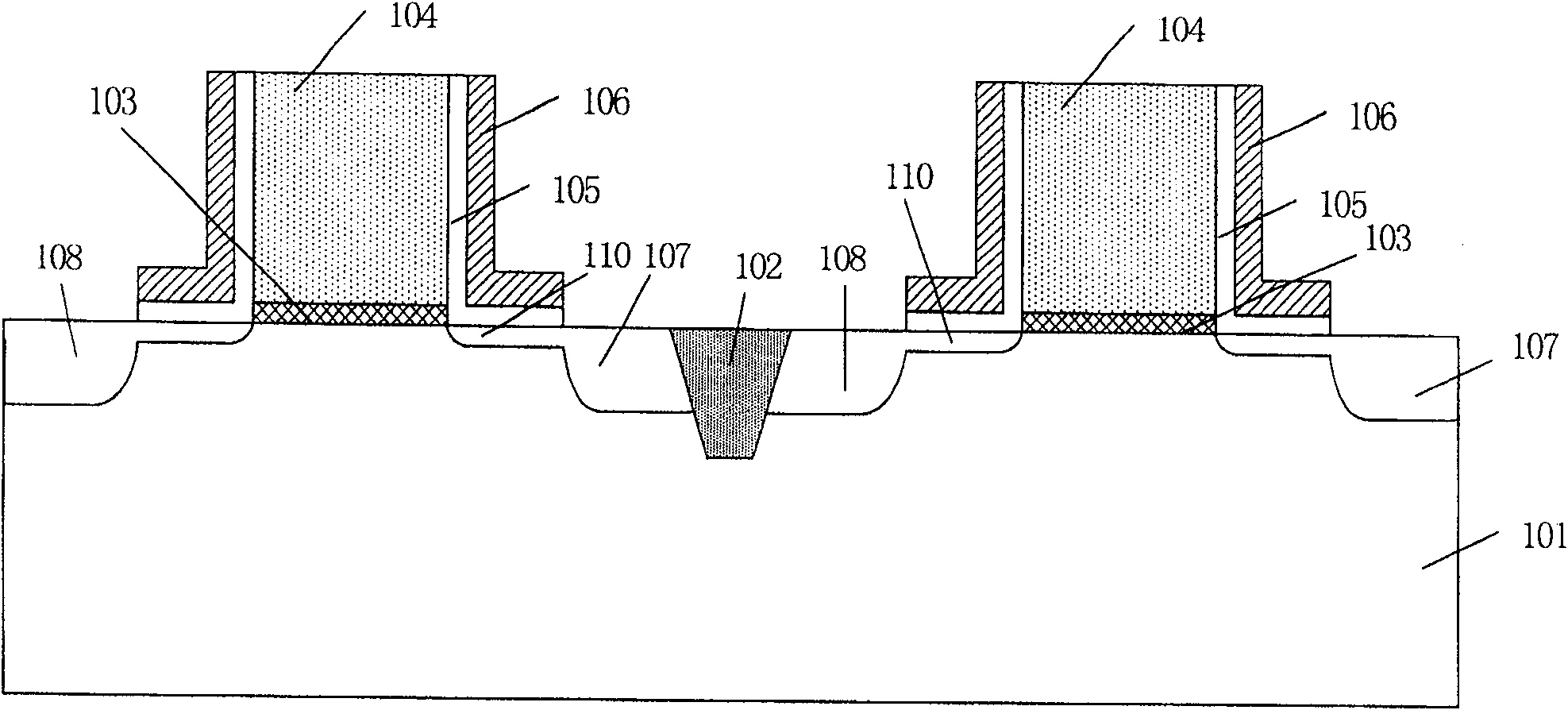

Semiconductor element isolating structure and forming method thereof

ActiveCN101599454AImprove ladder coveragePrevent bridgingSemiconductor/solid-state device detailsSolid-state devicesEngineeringMetal

The invention discloses a semiconductor element isolating structure and a forming method thereof. The forming method of the semiconductor element isolating structure comprises the following steps: firstly, providing a substrate with at least one shallow-groove isolating structure; then, carrying out a metal silicification process to form a dent on the surface of the shallow-groove isolating structure; forming a covering layer to cover the substrate and fill the dent; etching the covering layer to remove the covering layer outside the dent; and finally, forming a contact window etching-stopping layer to cover the substrate and fill the dent. The covering layer is filled in the dent in advance so that the contact window etching-stopping layer covered on the substrate and filled in the dent can not generate gaps or holes.

Owner:UNITED MICROELECTRONICS CORP

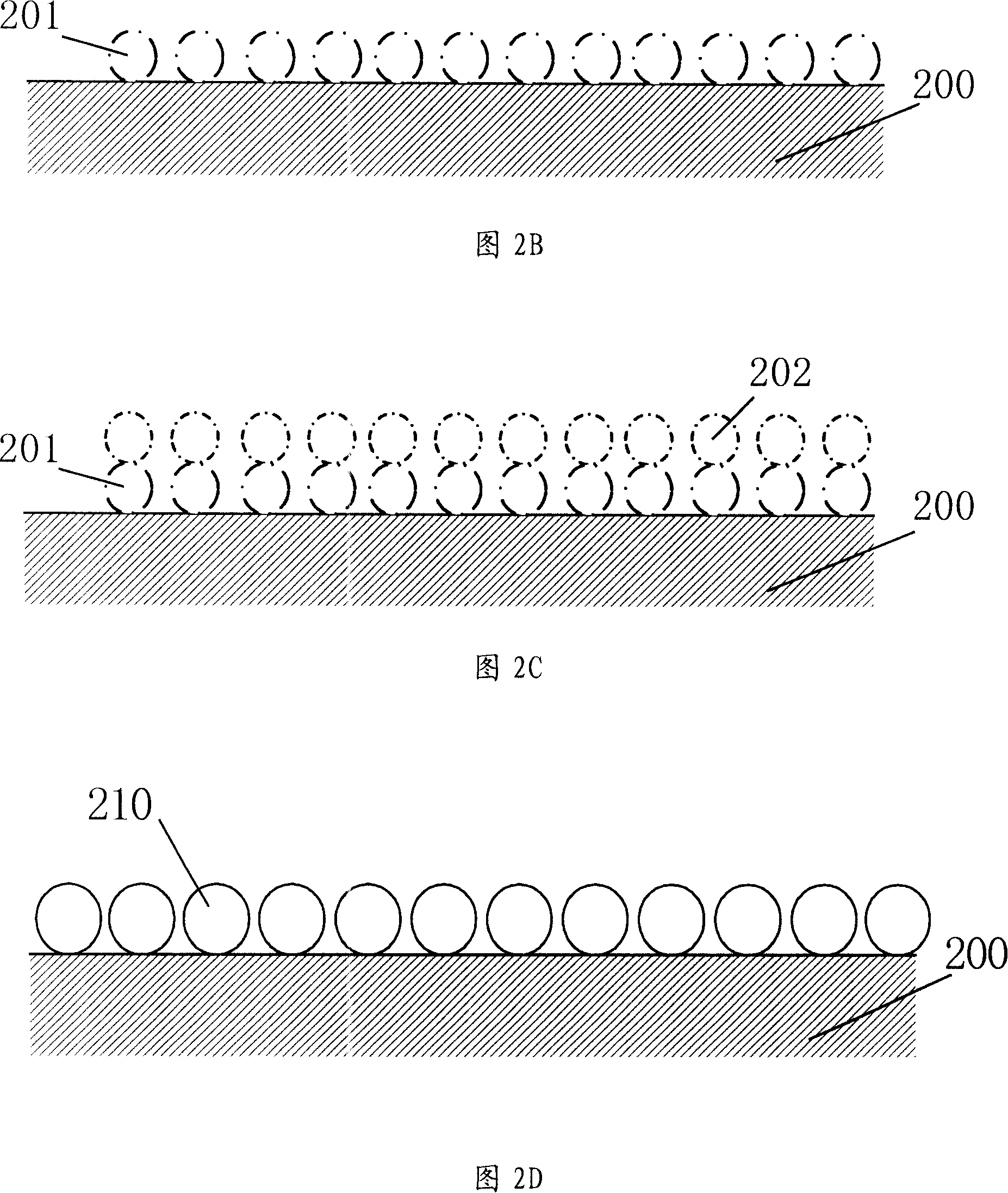

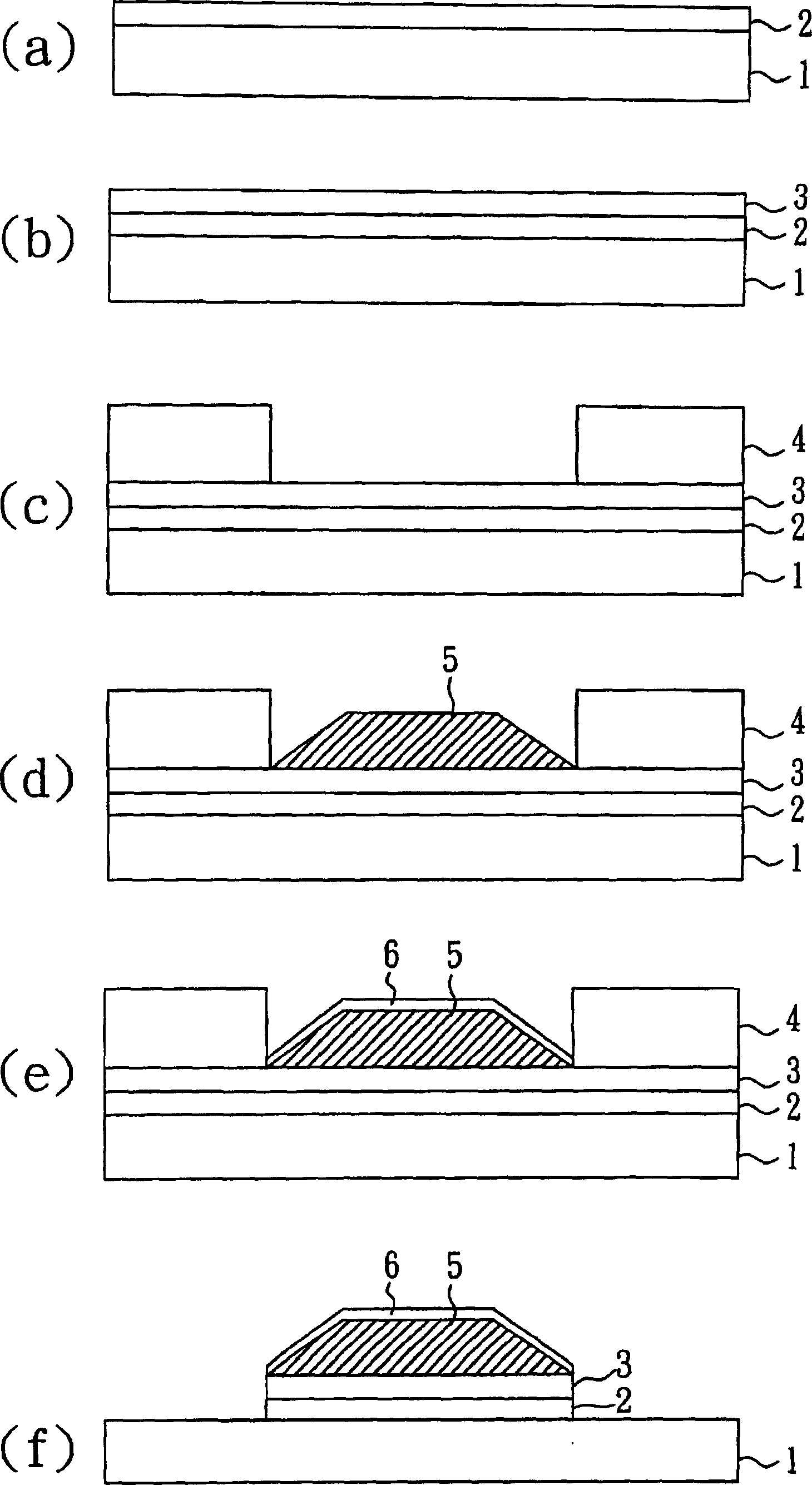

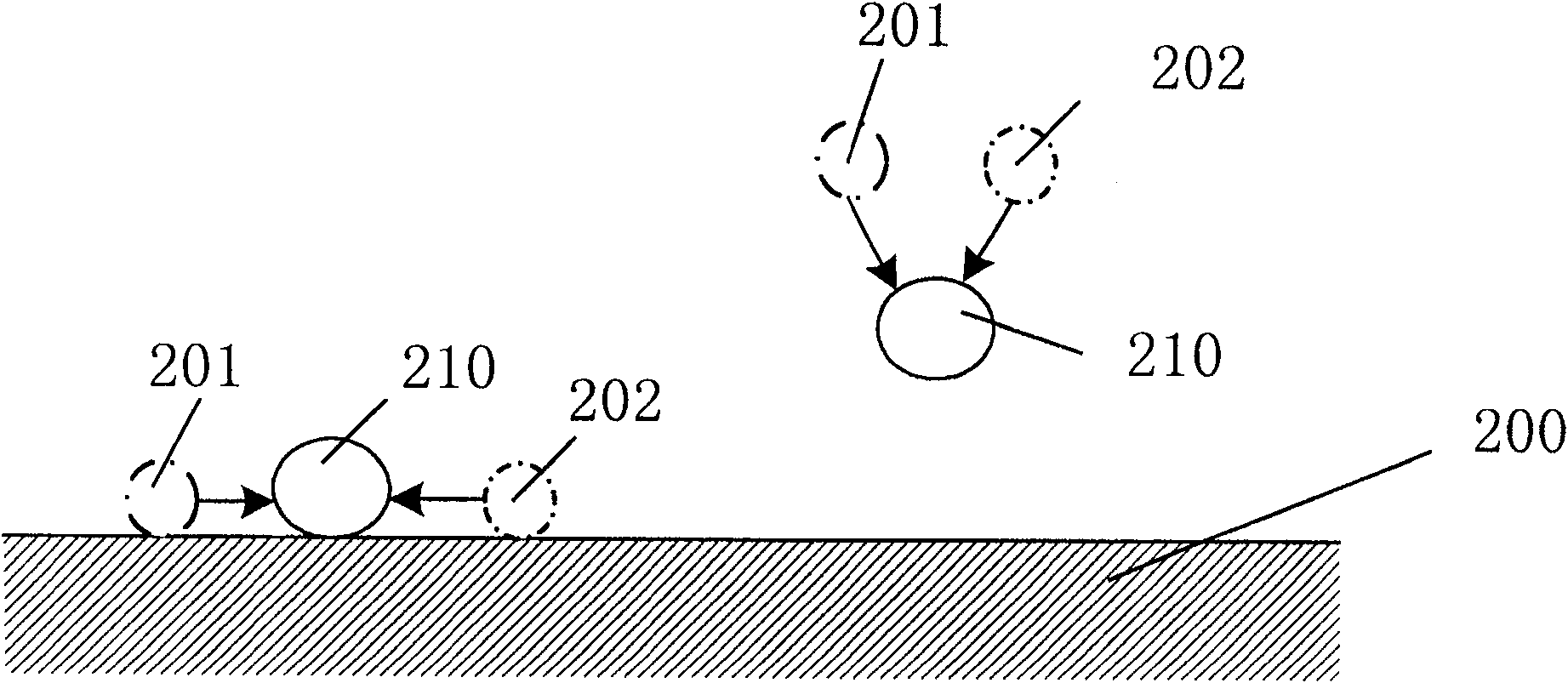

Method for preparing copper conductor for plane display substrate

ActiveCN1825560AAvoid generatingImprove ladder coverageSemiconductor/solid-state device manufacturingConductive pattern formationSulfur containingElectrolyte

The invention relates to a method for preparing copper leads for a flat display substrate, comprising the steps of: providing a substrate, forming a crystal seed layer on the surface of the substrate, forming a photoresistance layer with pattern on the surface of the crystal seed layer to expose part of the surface of the crystal seed layer and plating a copper lead layer on the partial exposed surface of the crystal seed layer, where the plating electrolyte comprises sulfur-containing compound. In addition, the contact surface between the prepared copper lead layer and the crystal seed layer makes an included angle greater than 0 deg. but less than 90 deg. with the surface of the copper lead layer. Thus, the prepared copper leads can improve the step covering property in the follow-up course and reduce produced holes and form inclined angles without traditional complex etching process.

Owner:AU OPTRONICS CORP

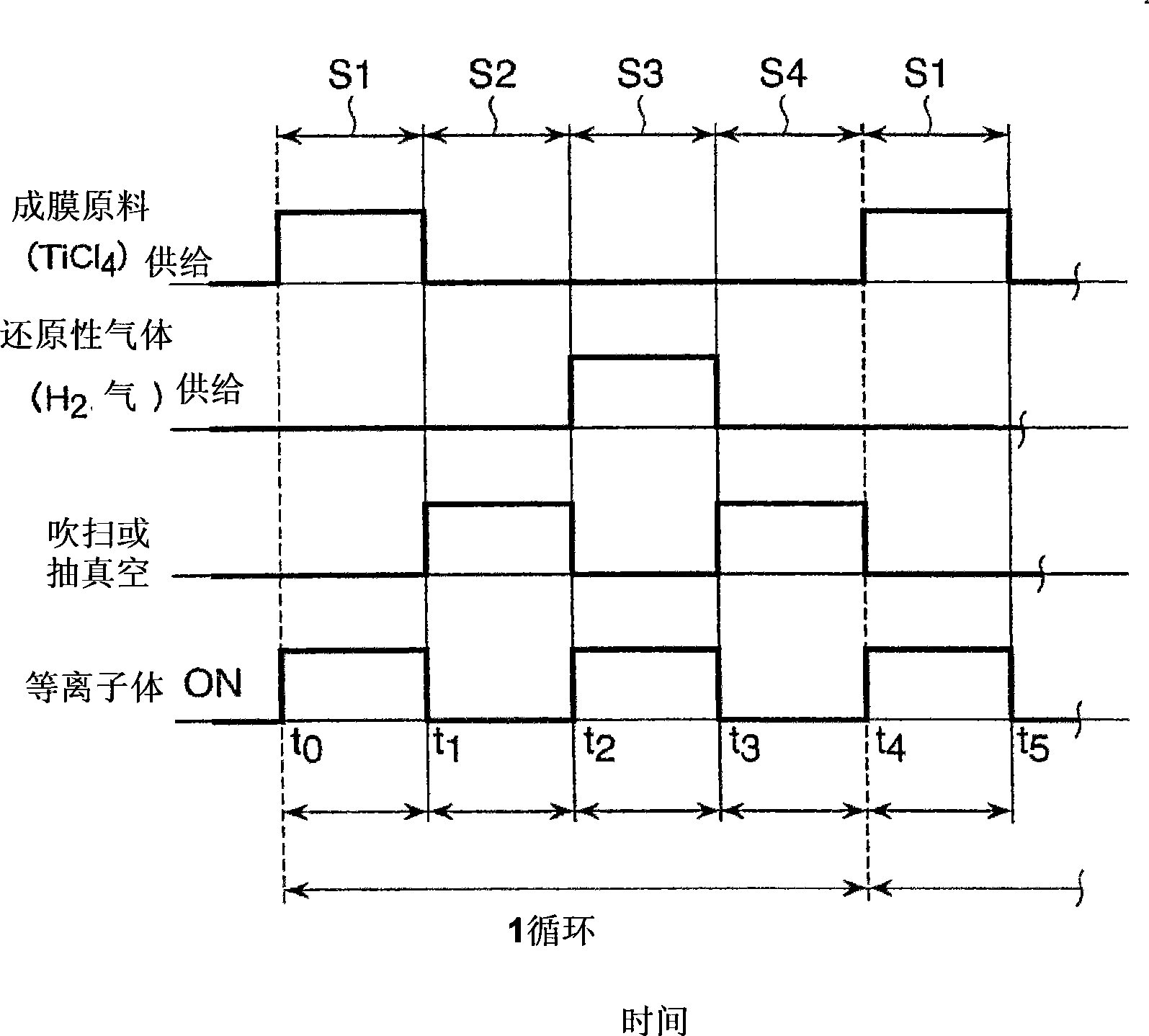

Film forming method

InactiveCN1906327AImprove adsorption capacityImprove uniformitySemiconductor/solid-state device manufacturingChemical vapor deposition coatingGas phaseMetallurgy

A film forming method is provided for forming a thin film including a metal on a substrate by alternately supplying the substrate with a film forming material including the metal and a reducing gas. At least a part of the film forming material is dissociated or decomposed in vapor phase by plasma and supplied onto the substrate.

Owner:TOKYO ELECTRON LTD

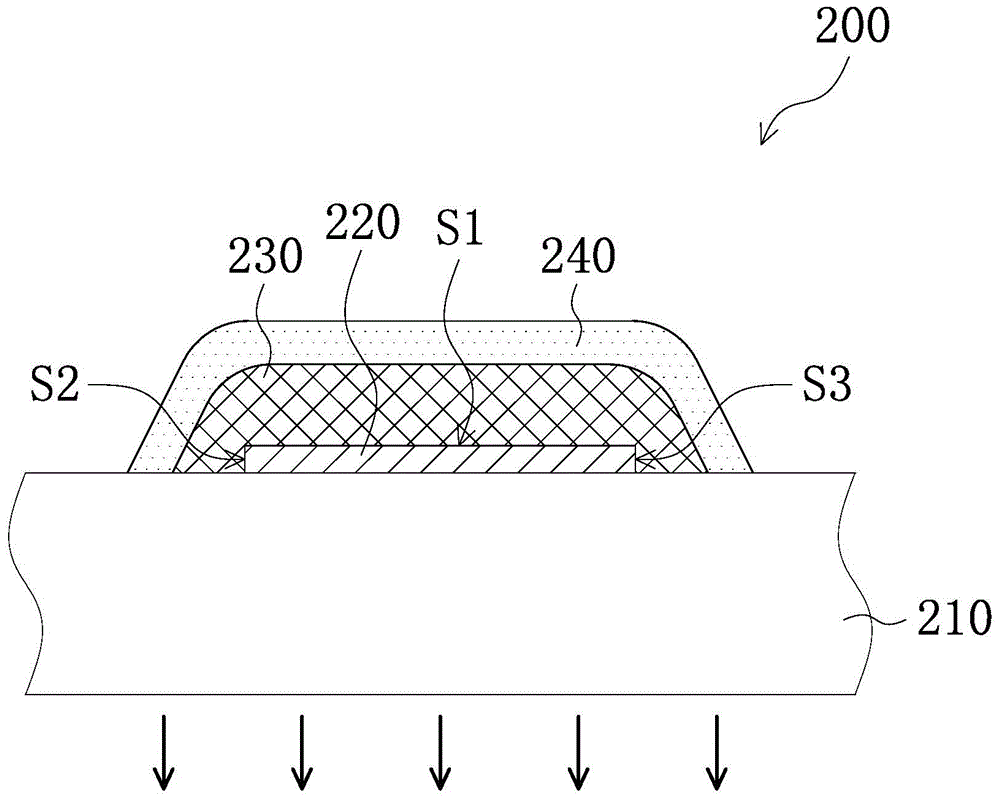

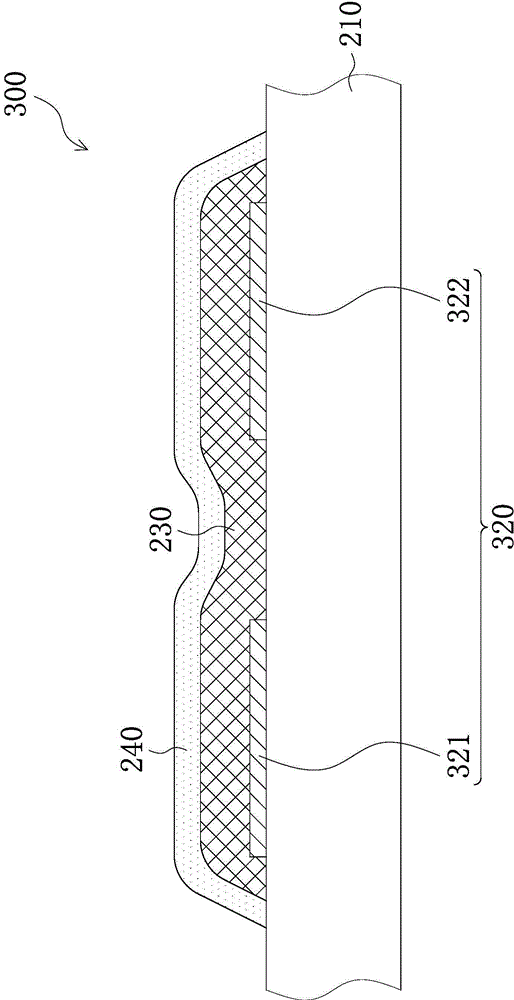

Organic light-emitting diode device used in lighting apparatus

InactiveCN103915572AImprove ladder coverageImprove yieldSolid-state devicesSemiconductor/solid-state device manufacturingOrganic semiconductorLight-emitting diode

An organic light-emitting diode device used in a lighting apparatus includes: a substrate; a patterned anode layer disposed on the substrate; an organic semiconductor layer disposed to cover an upper surface and sidewalls of the patterned anode layer and the substrate, wherein a thickness of the organic semiconductor layer is greater than three times of that of the patterned anode layer; and a cathode layer disposed to cover the organic semiconductor layer. According to the invention, a step coverage of the organic semiconductor layer is increased by designing a relative thickness ration of the anode layer and the organic semiconductor layer. In this way, the edge leakage problem can be prevented and a conventional bank structure in an organic light-emitting diode device can be omitted. This improves an element yield rate and increases a light-emitting area of the organic light-emitting diode device.

Owner:ULTIMATE IMAGE

Method for making wear-resistant dielectric layer

InactiveCN1825545AImprove ladder coverageSimple structureSemiconductor/solid-state device manufacturingWear resistantChemical vapor deposition

The invention firstly provides a substrate comprising plural connection pads, successively at least makes a plasma auxiliary chemical vapour deposition process to deposit a dielectric layer on the substrate surface, where the vapour deposition process is made in a high frequency-low frequency plasma alternating mode, and finally makes an anisotropic etching process to form plural openings in the dielectric layer, where these openings correspond to the connection pads and side wall of each opening is inclined outward.

Owner:TOUCH MICRO SYST TECH

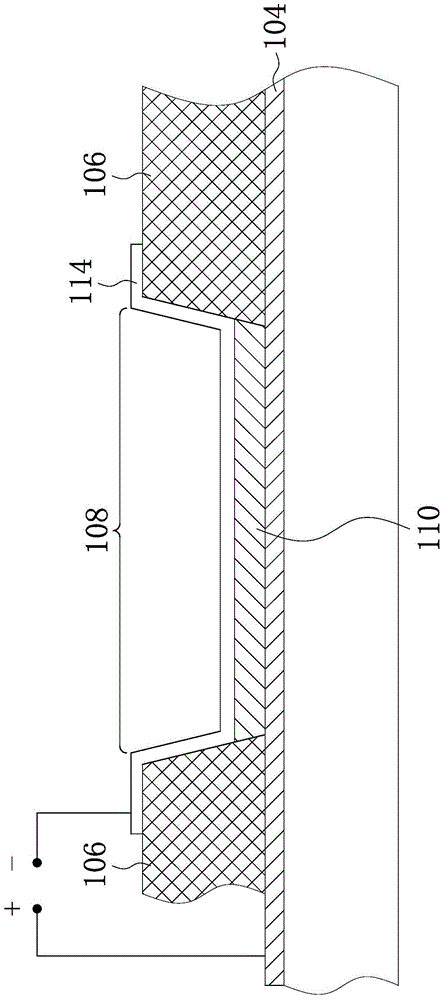

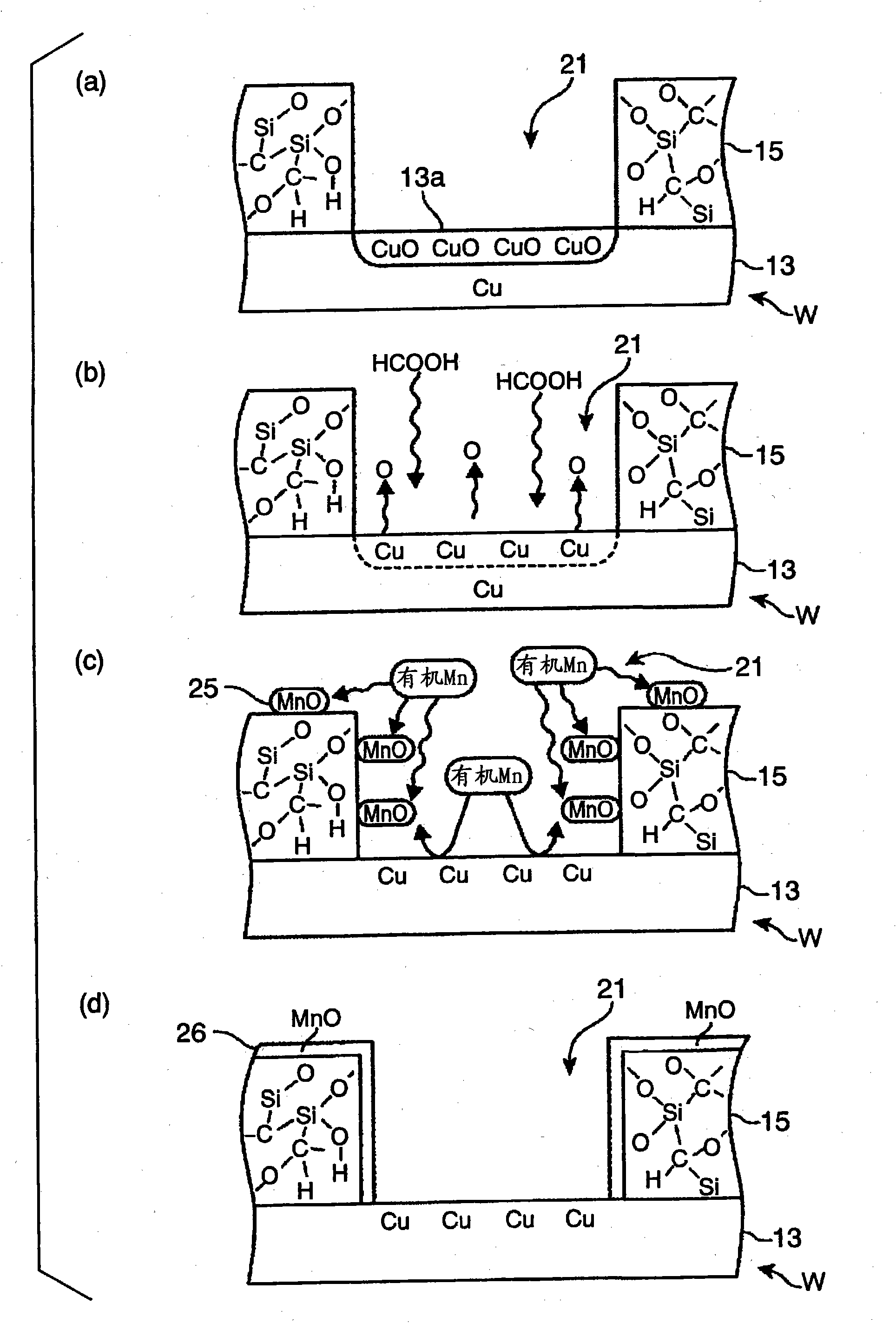

Semiconductor device manufacturing method, semiconductor device, electronic device, semiconductor manufacturing apparatus and storage medium

InactiveCN101897016ASuppress leakage currentWork fasterSemiconductor/solid-state device manufacturingChemical vapor deposition coatingSelf formingCopper-wiring

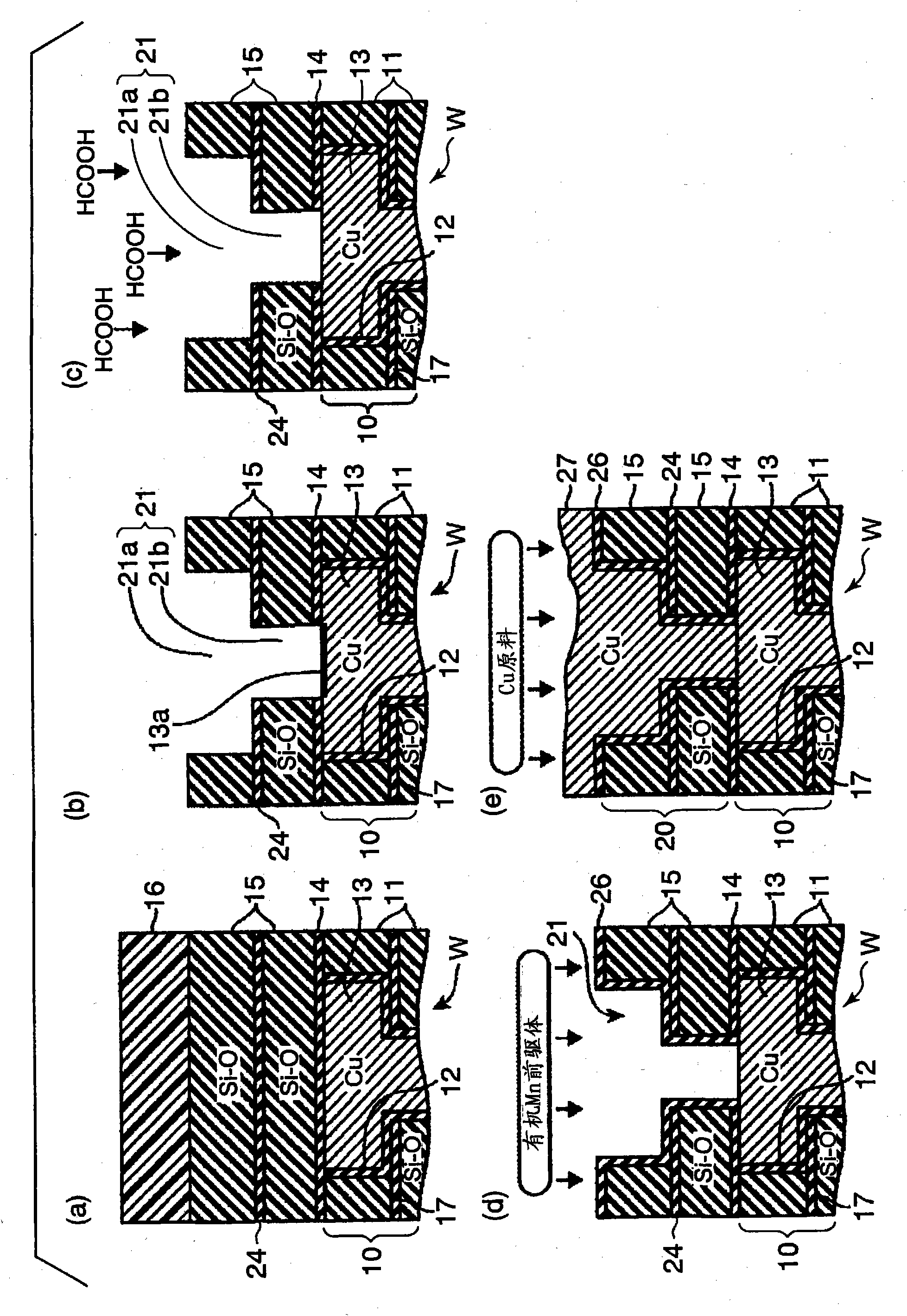

A barrier film having excellent step coverage is formed, and furthermore, increase of wiring resistance is suppressed, at the time of forming the barrier film on an exposed surface of an interlayer insulating film, which is on a substrate and has a recessed section formed thereon, and forming copper wiring electrically connected to metal wiring on a lower layer side in the recessed section. An oxide film on a surface of the copper wiring which is on the lower layer side and exposed from the bottom surface of the recessed section formed on the interlayer insulating film is reduced or etched and oxygen on the surface of the copper wiring is removed. Then, manganese oxide, i.e., a self-formed barrier layer, is selectively grown on an oxygen containing portion, such as the side walls of the recessed section and a surface of the interlayer insulating film by supplying an organic metal compound which contains manganese but no oxygen, while the manganese oxide is prevented from growing on the surface of the copper wiring. Then, the recessed section is filled with copper.

Owner:TOKYO ELECTRON LTD +1

Flash memory unit forming method

ActiveCN102569078AUniform thicknessImprove ladder coverageSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringChemical vapor deposition

A flash memory unit forming method comprises the steps as follows: a substrate is provided; a liner oxidation layer and an etching stop layer are formed sequentially on the surface of the substrate; at least two active areas are included in the substrate, and the adjacent active areas are isolated by a shallow trench isolation structure; the etching stop layer and the liner oxidation layer on the surface of the substrate are sequentially removed; a tunneling oxidation layer is formed on the surface of the substrate by a chemical vapor deposition method; and the tunneling oxidation layer is subjected to later stage oxidizing annealing treatment. The flash memory unit forming method provided by the invention avoids the double-hump effect and the reverse narrow channel effect, and the flash memory unit is better in period durability.

Owner:SEMICONDUCTOR MANUFACTURING INTERNATIONAL (BEIJING) CORP

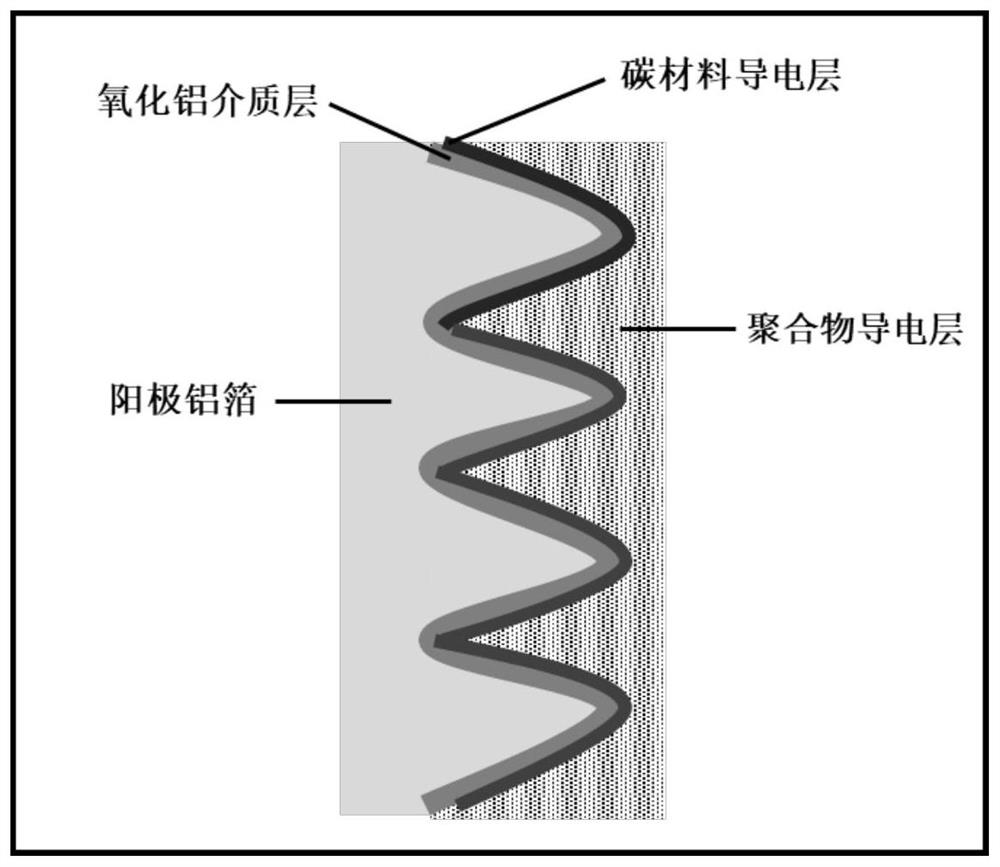

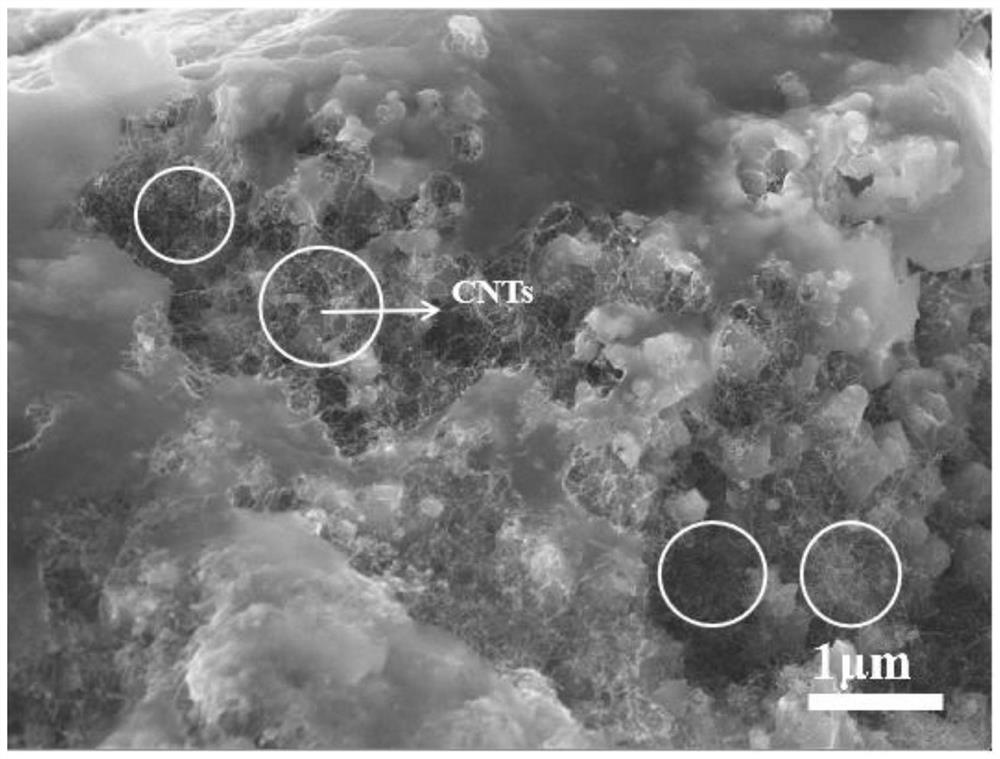

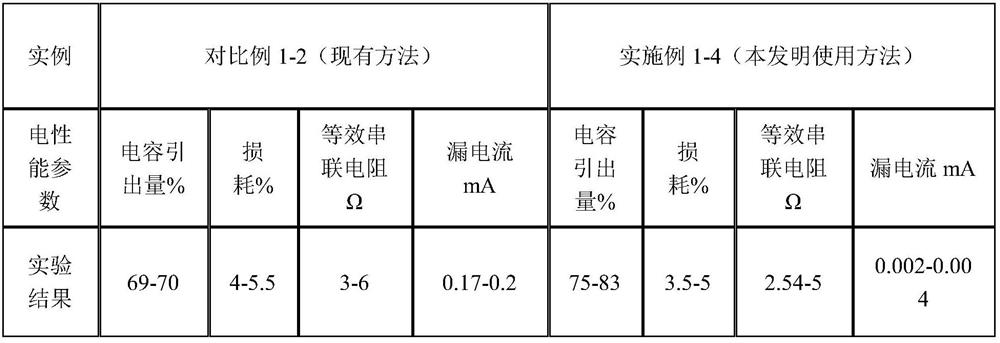

Method for preparing conductive polymer cathode in solid-state aluminum electrolytic capacitor

PendingCN113380550AImprove ladder coverageIncrease capacity extraction rateSolid electrolytic capacitorsCapacitor electrodesConductive polymerElectrochemistry

The invention discloses a method for preparing a conductive polymer cathode in a solid-state aluminum electrolytic capacitor, and belongs to the field of solid-state aluminum electrolytic capacitors. The method comprises the following steps: pre-depositing a conductive layer on the surface of an anode foil dielectric layer by adopting a chemical vapor deposition method; preparing a conductive polymer on the surface of the deposited conductive layer through an electrochemical method to form a composite conductive layer in a solid-state aluminum electrolytic capacitor; and carrying out cathode electrode extraction on the composite conductive layer to obtain the conductive polymer cathode. According to the invention, the adopted chemical vapor deposition technology avoids the problem that solution molecules are difficult to enter tiny holes in the surface of the anode aluminum foil in an impregnation method and a chemical polymerization method, and effectively avoid the damage of the solution to the dielectric layer.

Owner:XI AN JIAOTONG UNIV

Semiconductor element isolating structure and forming method thereof

ActiveCN101599454BImprove ladder coveragePrevent bridgingSemiconductor/solid-state device detailsSolid-state devicesEtchingStructural engineering

The invention discloses a semiconductor element isolating structure and a forming method thereof. The forming method of the semiconductor element isolating structure comprises the following steps: firstly, providing a substrate with at least one shallow-groove isolating structure; then, carrying out a metal silicification process to form a dent on the surface of the shallow-groove isolating structure; forming a covering layer to cover the substrate and fill the dent; etching the covering layer to remove the covering layer outside the dent; and finally, forming a contact window etching-stopping layer to cover the substrate and fill the dent. The covering layer is filled in the dent in advance so that the contact window etching-stopping layer covered on the substrate and filled in the dent can not generate gaps or holes.

Owner:UNITED MICROELECTRONICS CORP

Zirconium oxide film, deposition method and application thereof

InactiveCN112038214AImprove ladder coverageUneven solutionSemiconductor/solid-state device manufacturingPhysical chemistryMethyl palmoxirate

The invention relates to a zirconium oxide film, a deposition method and application thereof. The zirconium oxide film ZrO2 deposition method includes: depositing a zirconium oxide film by a chemicalvapor deposition method, and supplying a cyclopentyl methyl ether solvent before supplying a zirconium source during deposition. According to the invention, a cyclopentyl methyl ether solvent is usedas an additive to promote the flow of a zirconium source, so that the problem of non-uniform film caused by local excessive deposition can be avoided.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI +1

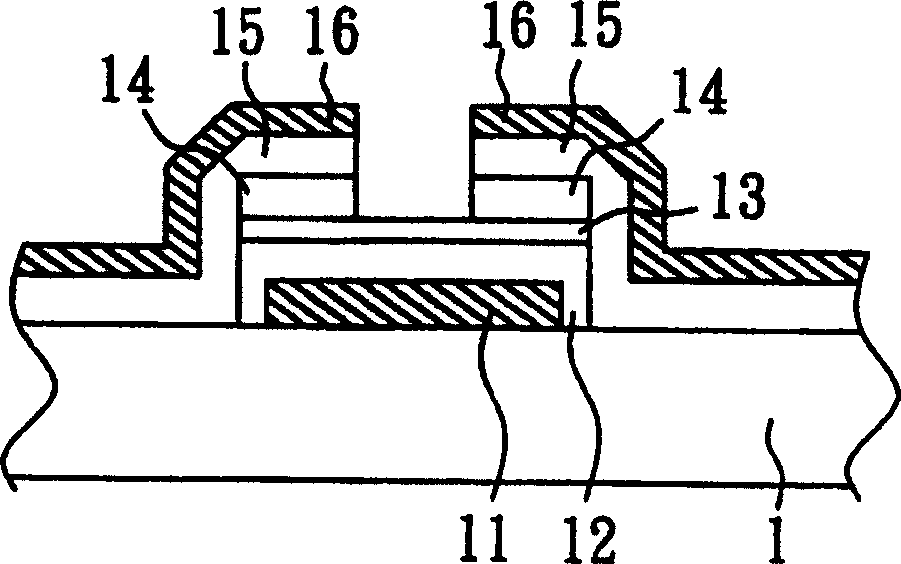

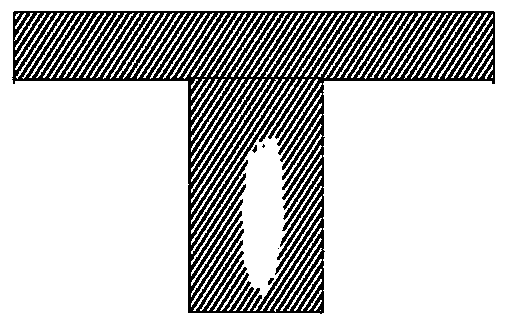

Semiconductor device and open structure of semiconductor device

ActiveCN100420009CImprove ladder coverageImprove reliabilitySemiconductor/solid-state device detailsSolid-state devicesEngineeringOpen structure

The present invention provides a semiconductor device and an open structure of the semiconductor device, in particular to an opening structure in a semiconductor device with improved step coverage. The opening structure comprises a dielectric layer overlying a substrate and having at least one via opening to expose the substrate. Wherein the via opening comprises a step region in the upper portion of the via opening and a concave profile region with respect to the dielectric layer in the lower portion of the via opening. The semiconductor device and the open structure of the semiconductor device of the present invention is capable of improving the percentage of coverage of the metal step and further improving the reliability of the device.

Owner:TAIWAN SEMICON MFG CO LTD

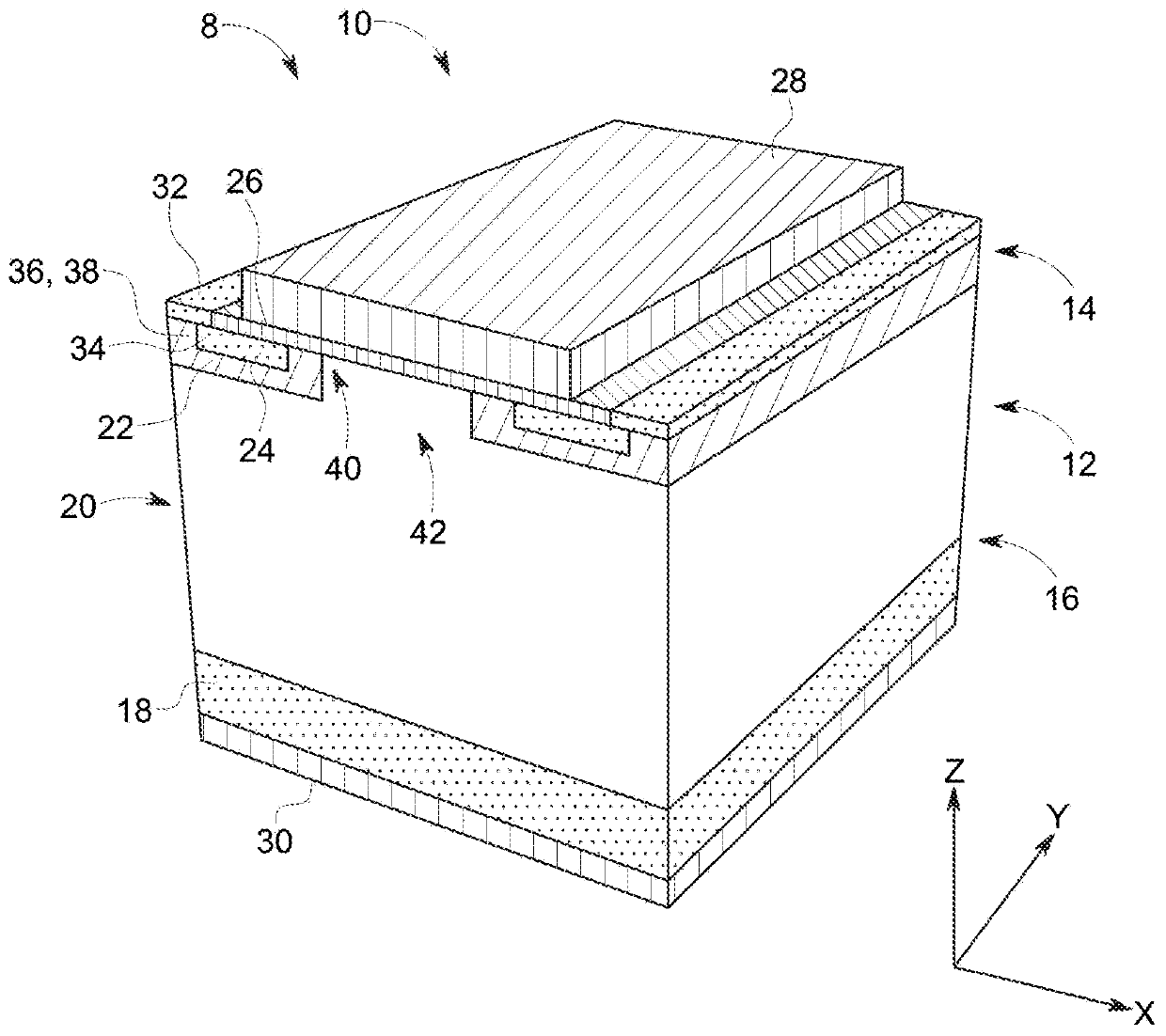

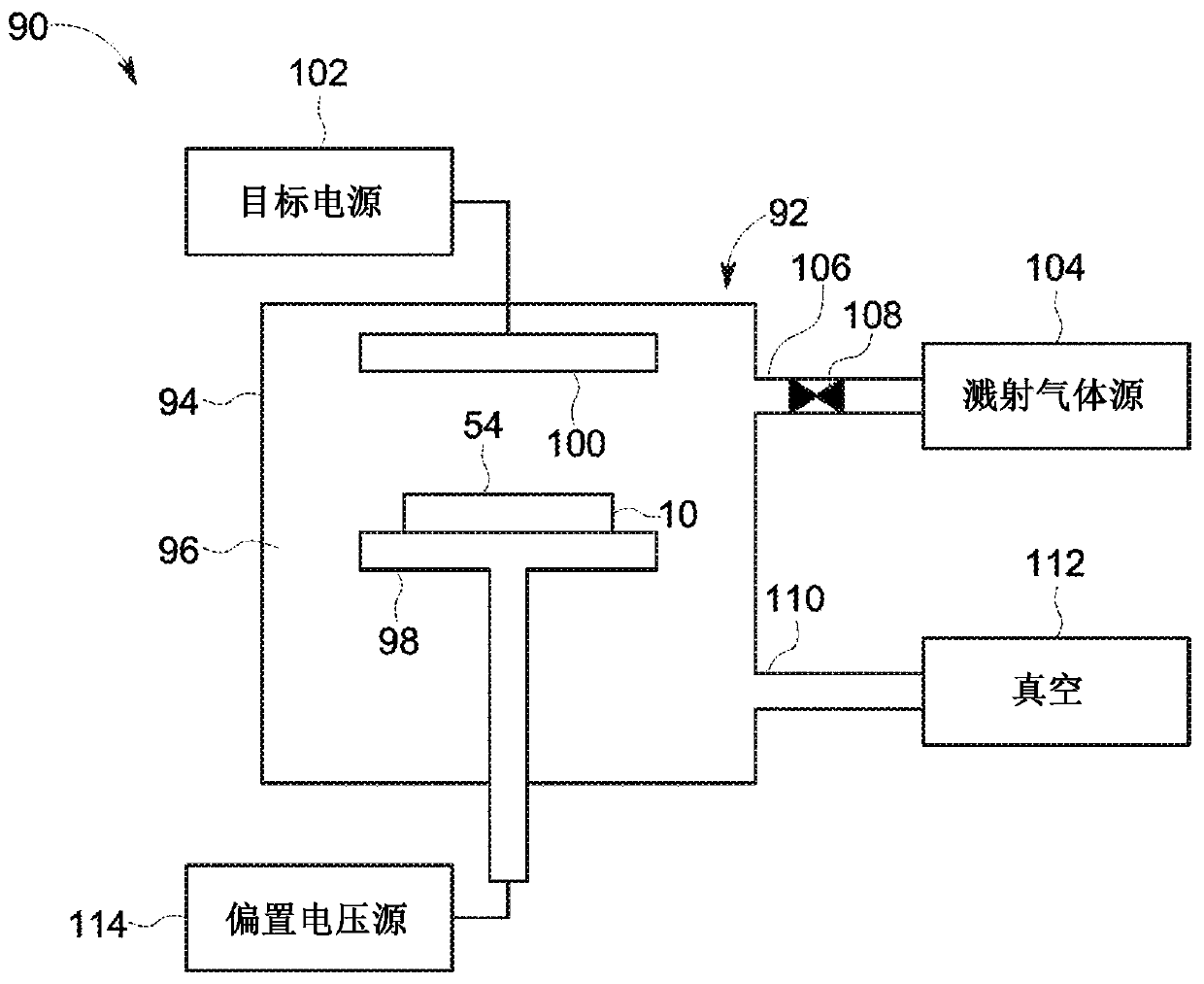

Sputtering system and method for forming a metal layer on a semiconductor device

PendingCN111052390AImprove ladder coverageImprove reliabilitySemiconductor/solid-state device detailsVacuum evaporation coatingDevice materialDielectric layer

A method for sputtering an aluminum layer on a surface of a semiconductor device is presented. The method includes three sputtering steps for depositing the aluminum layer, where each sputtering stepincludes at least one sputtering parameter that is different from a corresponding sputtering parameter of another sputtering step. The surface of the semiconductor device includes a dielectric layer having a plurality of openings formed through the dielectric layer.

Owner:GENERAL ELECTRIC CO

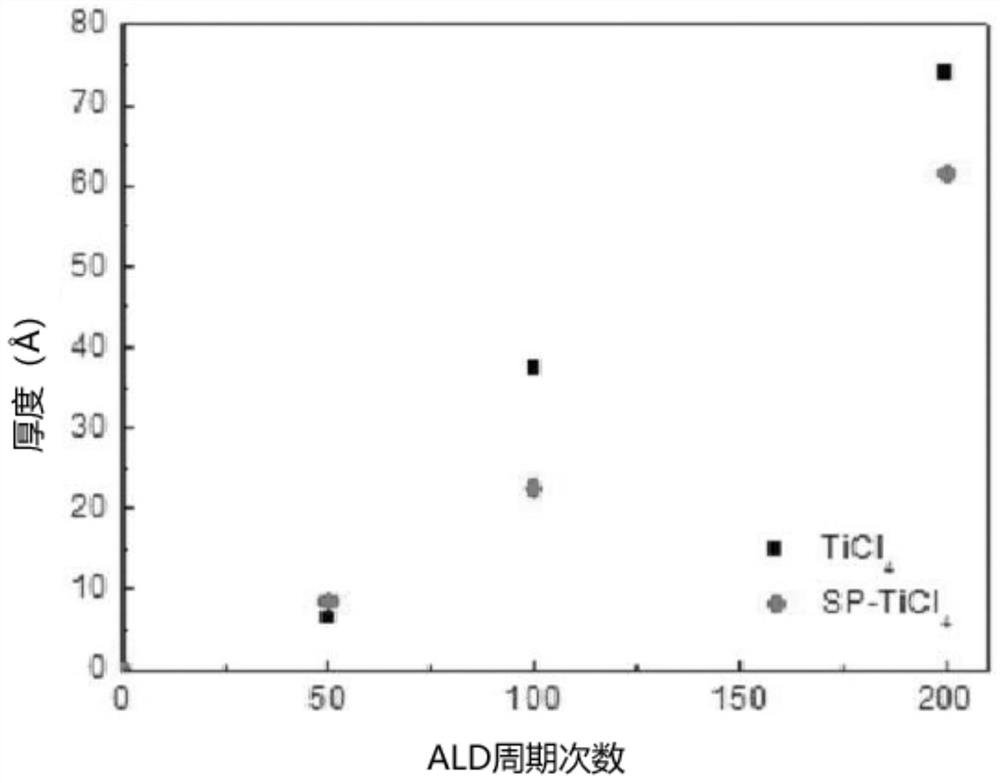

Semiconductor assembly and manufacturing method thereof

PendingCN112331618AReduce widthIncrease widthSemiconductor/solid-state device detailsSolid-state devicesProtection layerMechanical engineering

The invention provides a semiconductor assembly and a manufacturing method thereof. The manufacturing method comprises the following steps: forming a first sealing ring and a second sealing ring whichare separated from each other on a substrate; forming a protective layer on the substrate for covering the first sealing ring and the second sealing ring, wherein the portion, between the first sealing ring and the second sealing ring, of the protective layer is provided with a concave surface; removing the protective layer at the concave surface and a part of the protective layer on the first sealing ring, forming a gap wall on the side wall of the first sealing ring, and forming an opening in the protective layer, wherein the width of the opening is greater than that of the first sealing ring, and the opening enables the top surface of the first sealing ring and the clearance wall to be exposed.

Owner:WINBOND ELECTRONICS CORP

Method for making base-board of liquid crystal display

ActiveCN100490125CGood etch tilt angleImprove performanceSemiconductor/solid-state device manufacturingNon-linear opticsLiquid-crystal displayInsulation layer

This invention discloses a method for manufacturing a base plate of a LCD used in improving the etched tilt angles of a semiconductor layer and an insulation layer, which utilizes an etching gas containing FS compound to etch the insulation layer to form a fine etched tilted angle and the semiconductor layer can have a side etched result to increase the coverage of the ladder to the latter process, which can process film transistors in many layers of structures containing a block layer, a semiconductor layer and an insulation layer without peeling off the layers.

Owner:AU OPTRONICS CORP

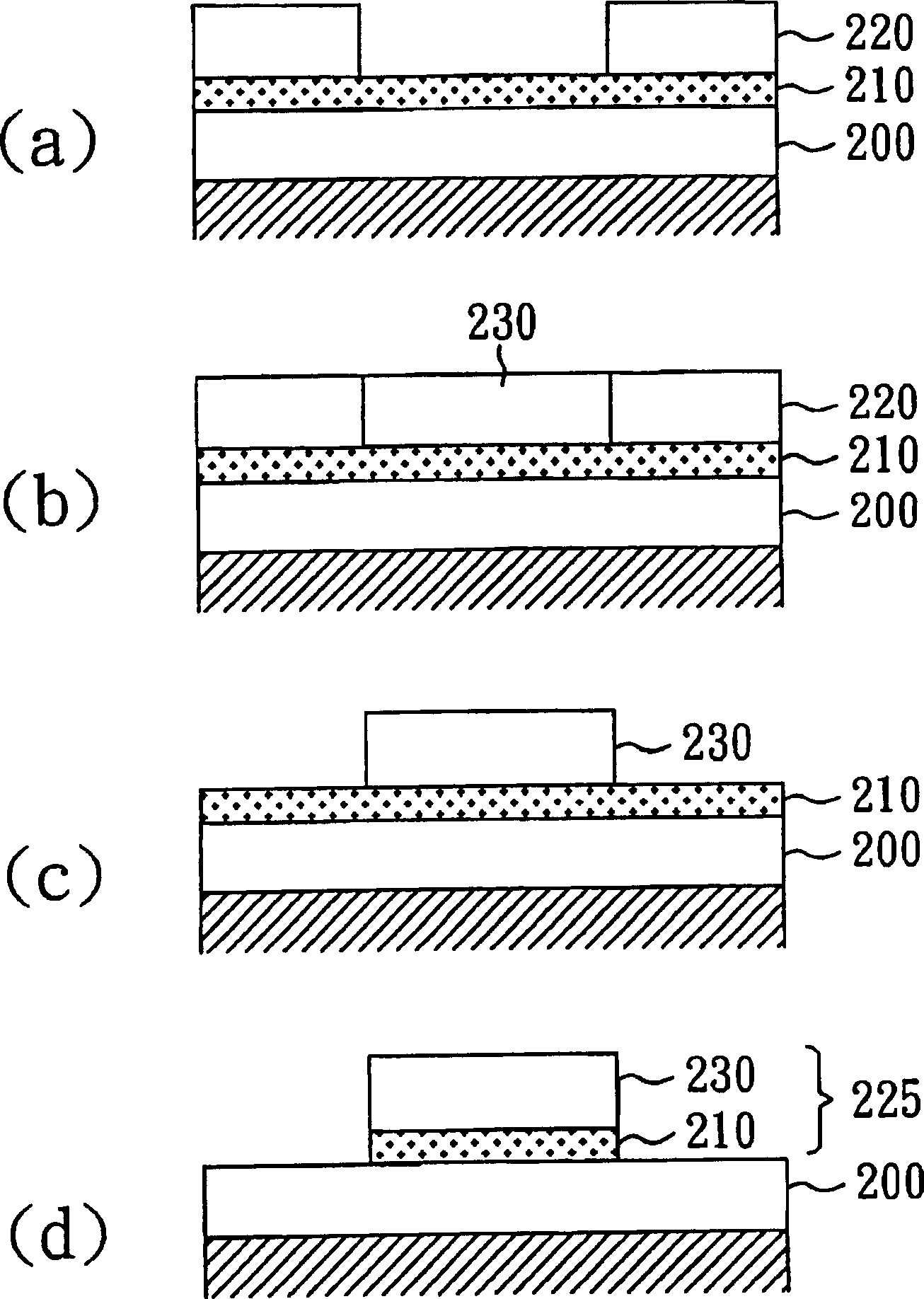

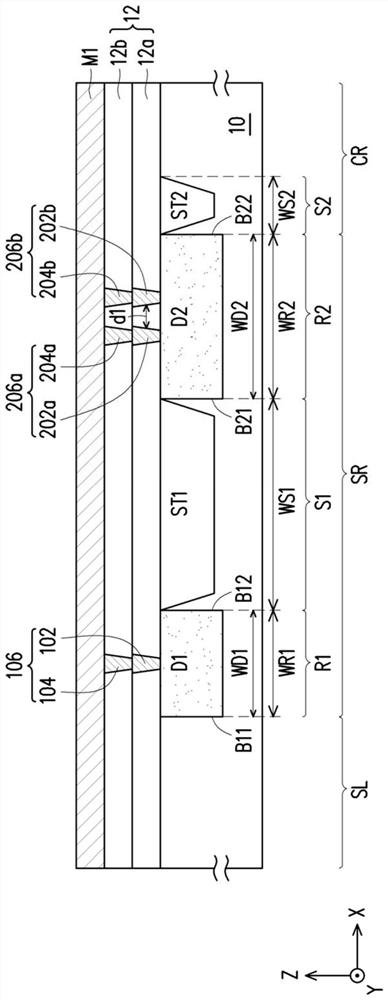

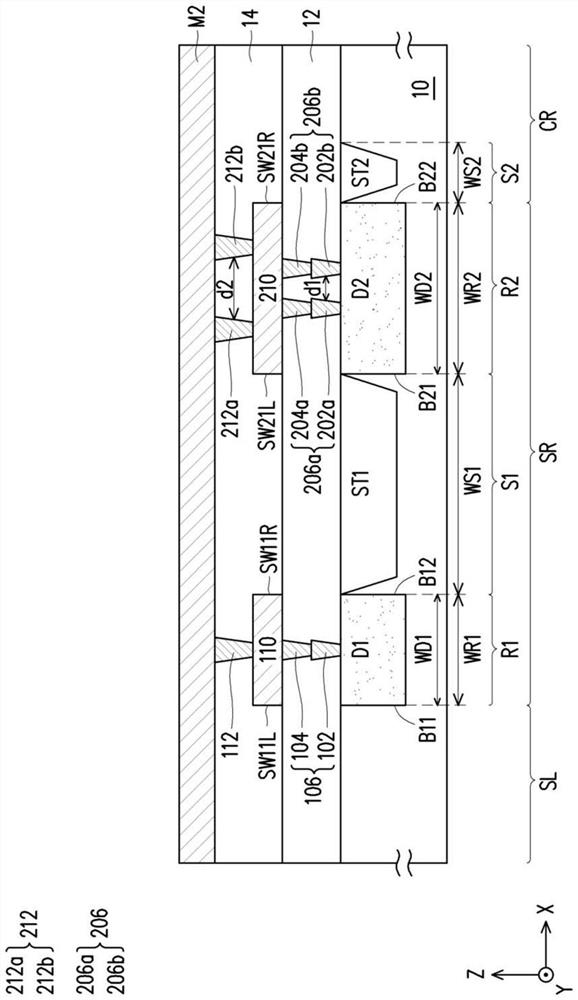

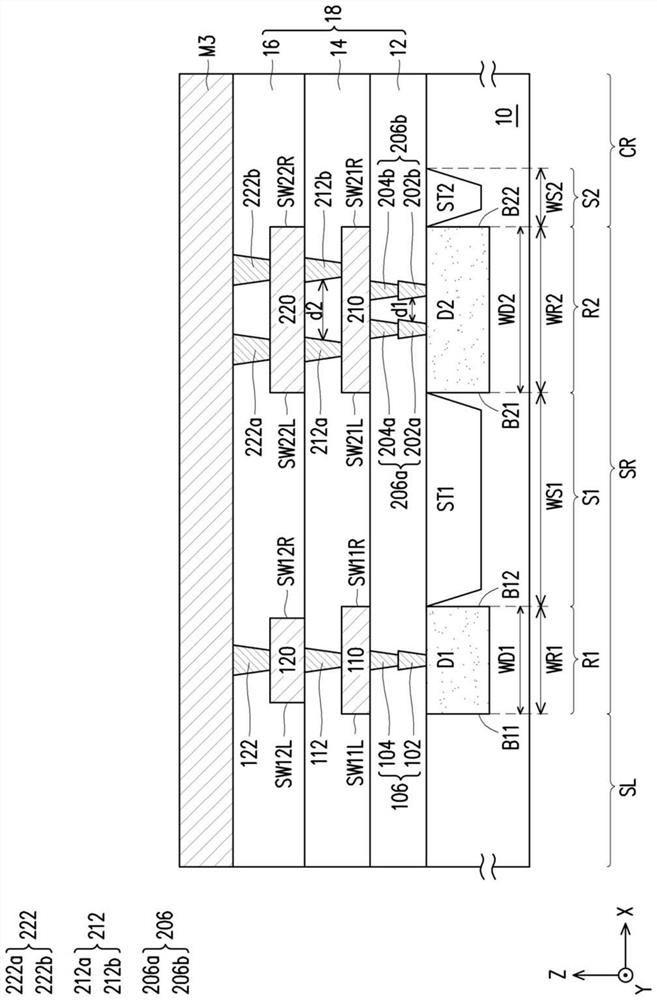

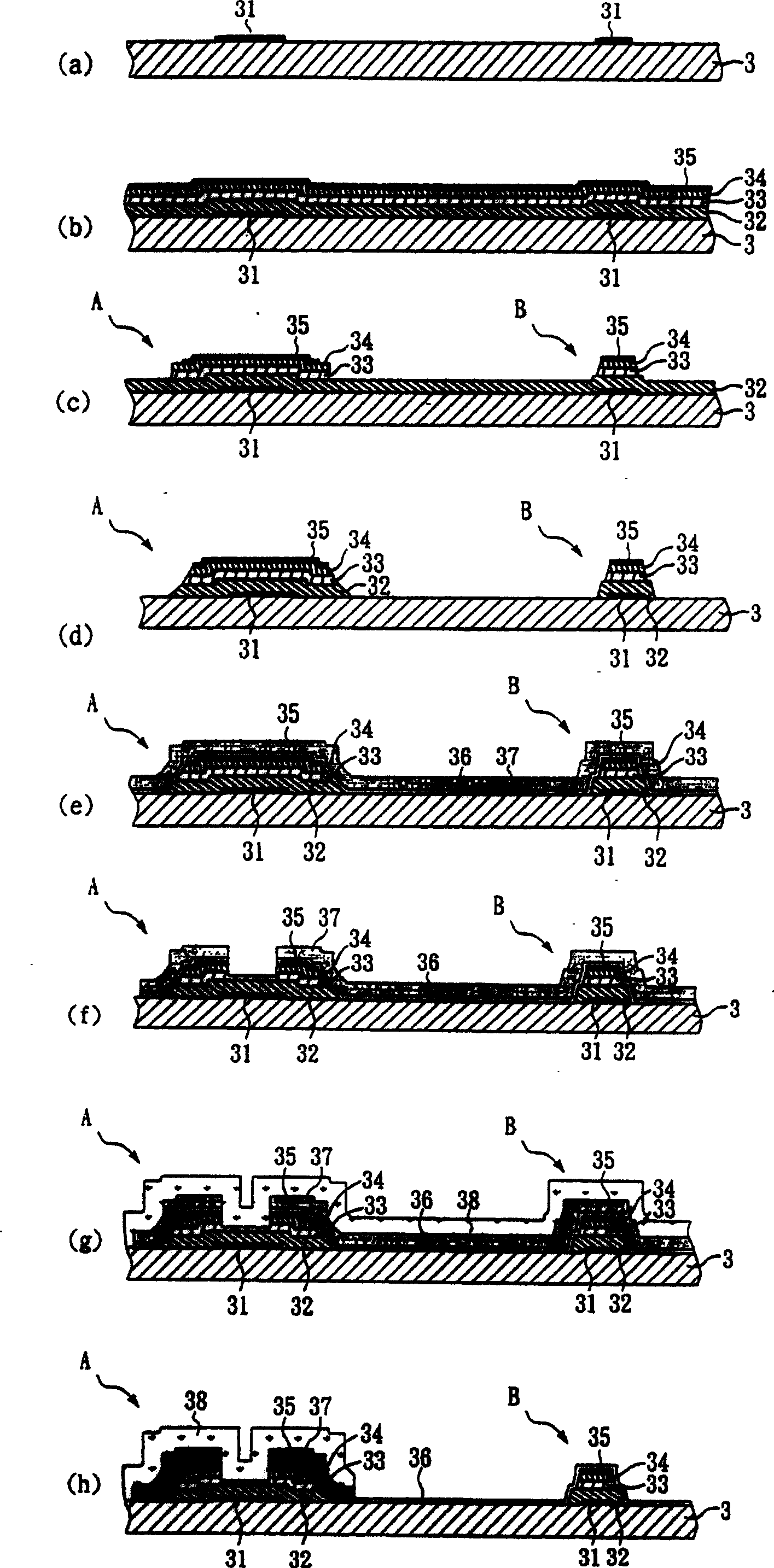

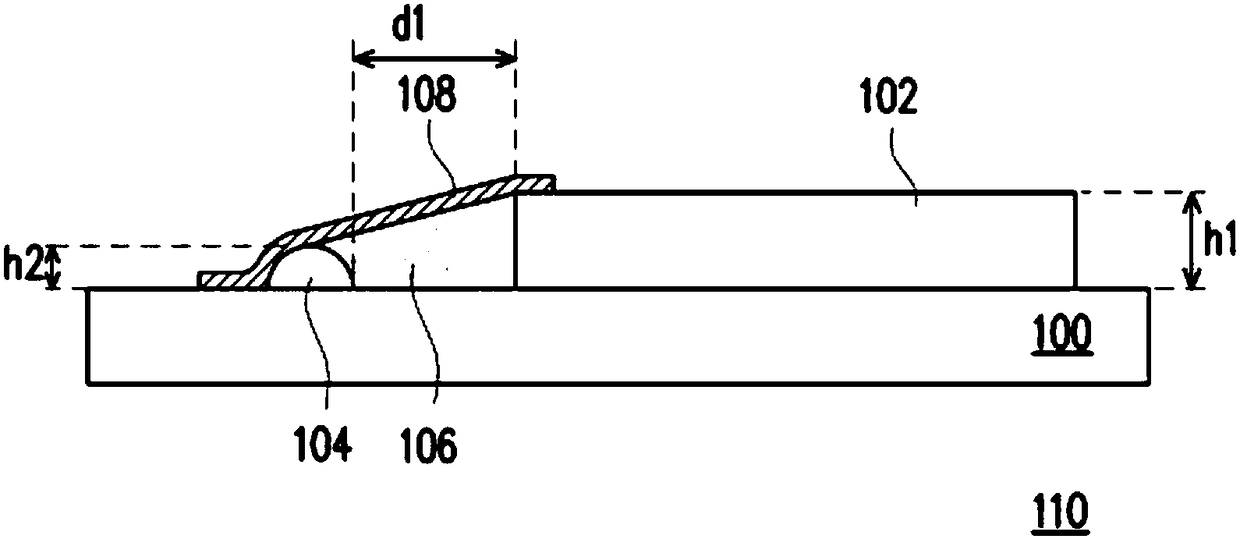

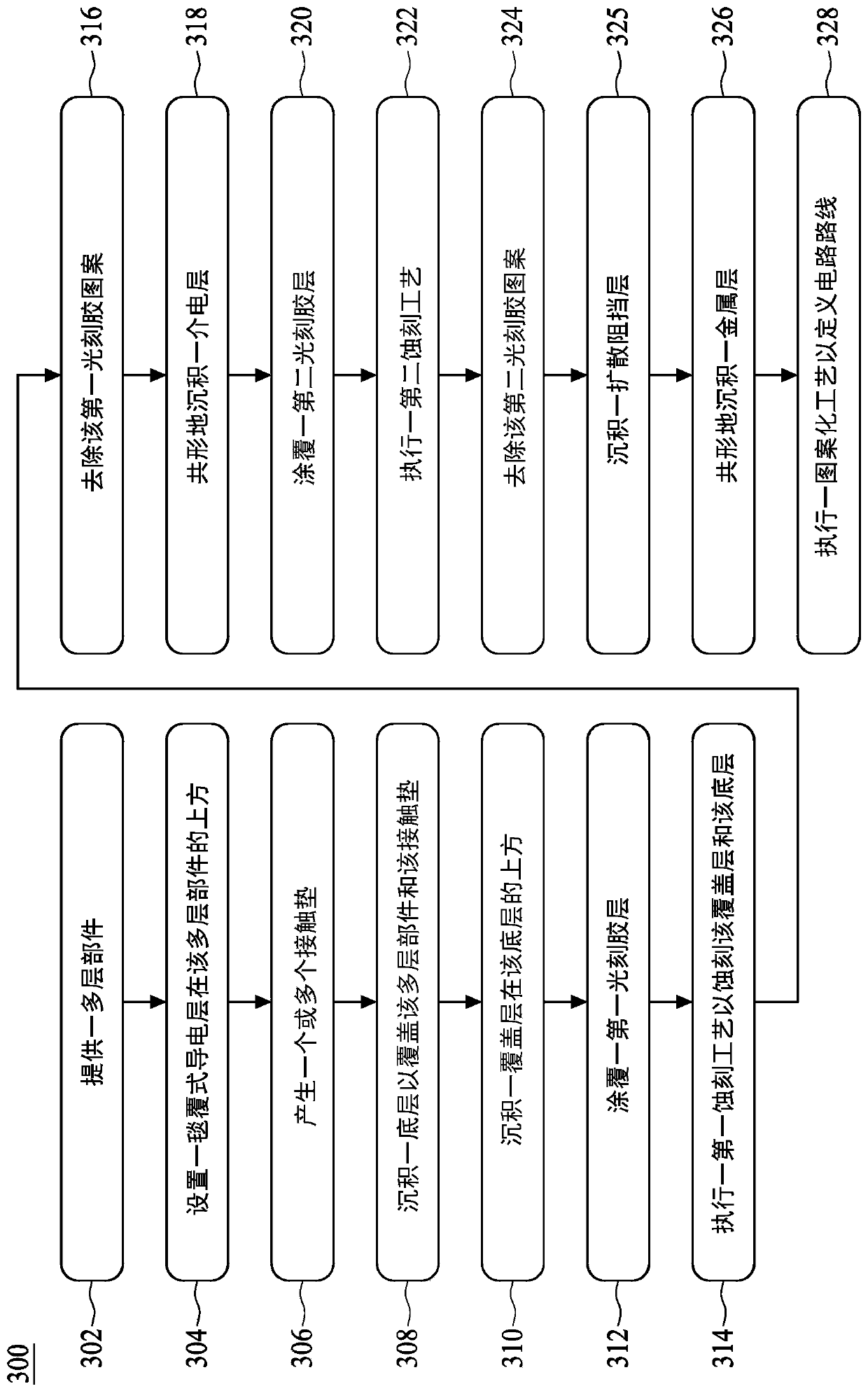

Pattern structure for electronic component and manufacturing method of pattern structure

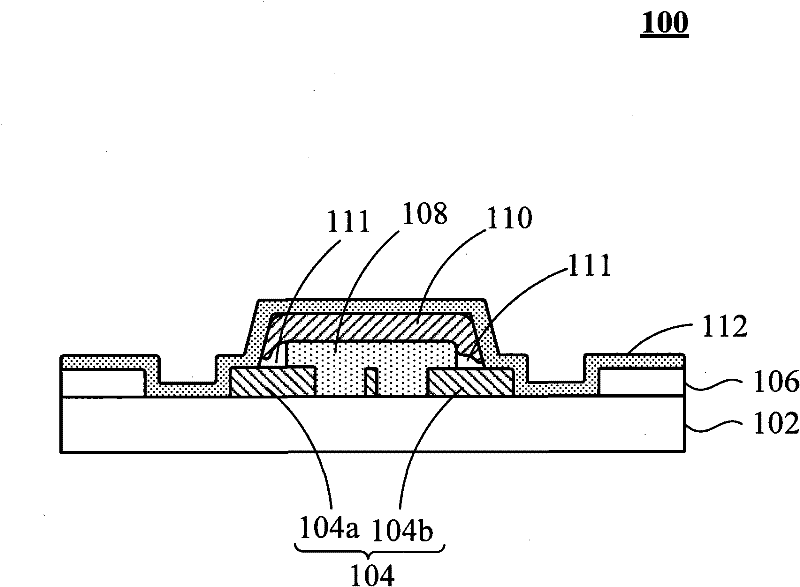

InactiveCN108122731ASmall slopeReduce height differenceSolid-state devicesSemiconductor/solid-state device manufacturingEngineeringElectronic component

The present invention relates to a pattern structure for an electronic component and a manufacturing method of the pattern structure. The pattern structure includes a pattern layer, a blocking structure, a cantilever structure, and a connection structure; the pattern layer is disposed on a substrate; the blocking structure is disposed on the substrate at one side of the pattern layer; the thickness of the blocking structure is smaller than the thickness of the pattern layer; the cantilever structure is connected between the pattern layer and the blocking structure; and the connection structureis connected between the pattern layer and the substrate at one side of the pattern layer, and is located on the cantilever structure and the blocking structure. The pattern structure provided by thetechnical schemes of the invention has better step coverage performance.

Owner:WINBOND ELECTRONICS CORP

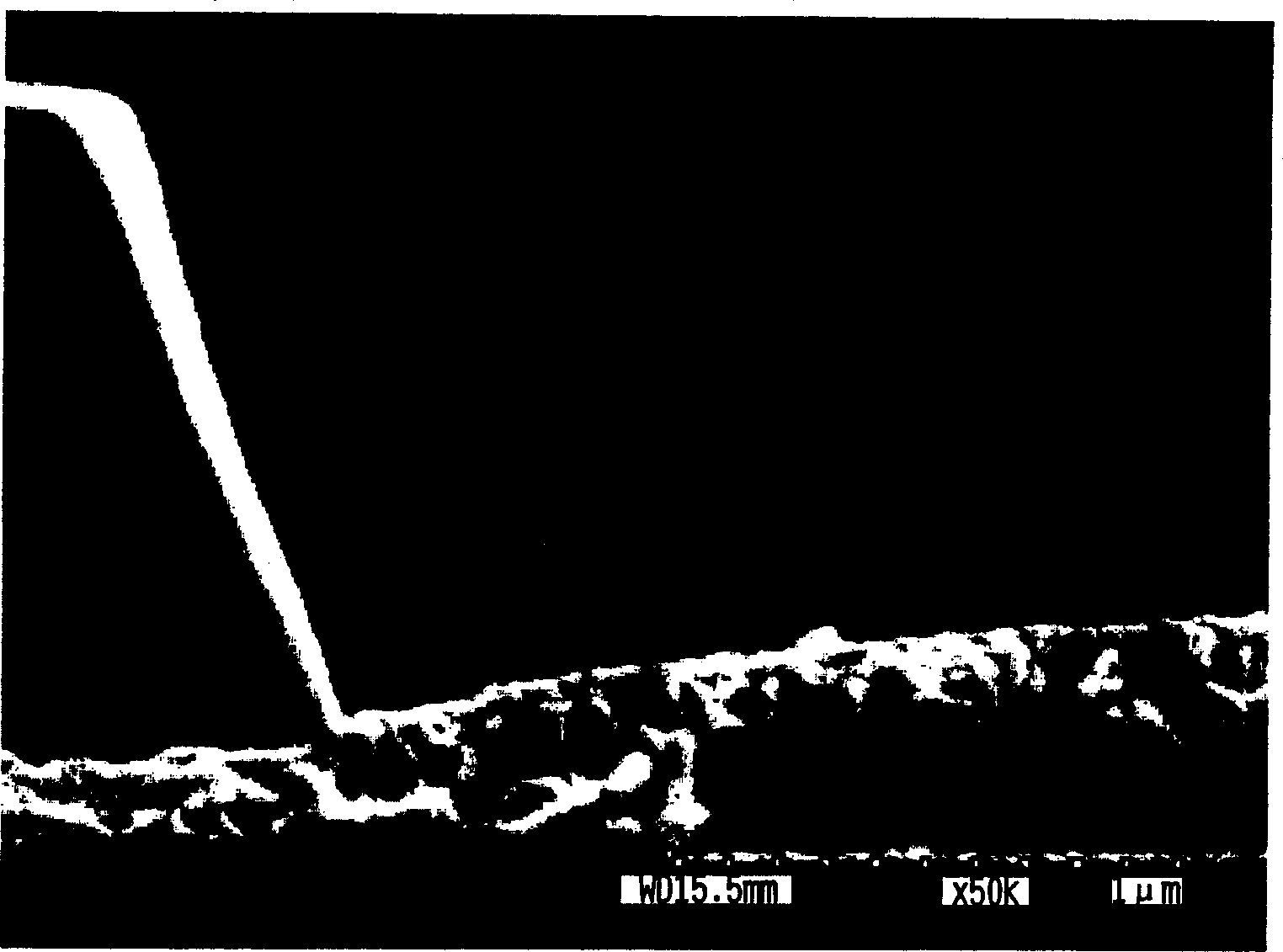

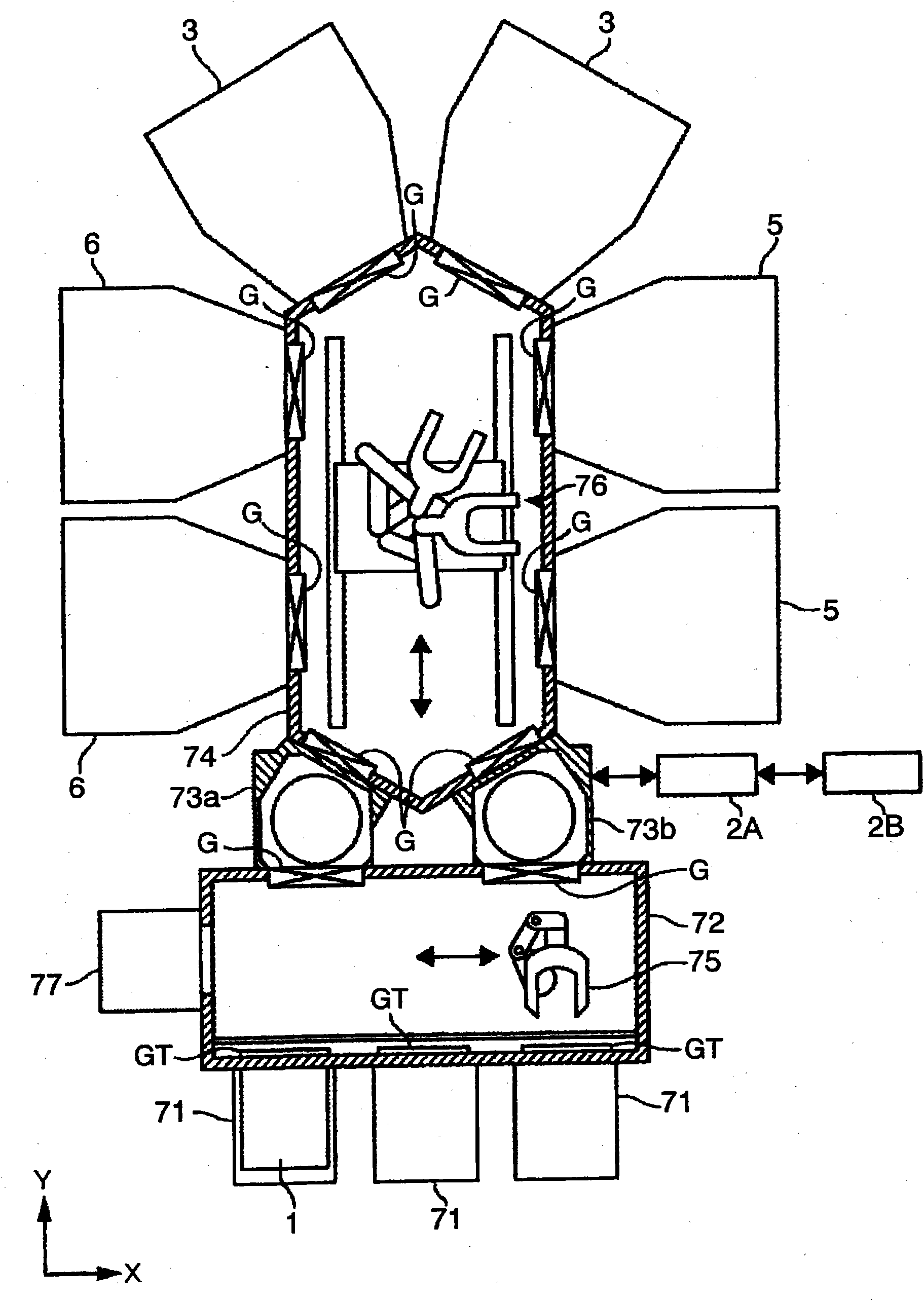

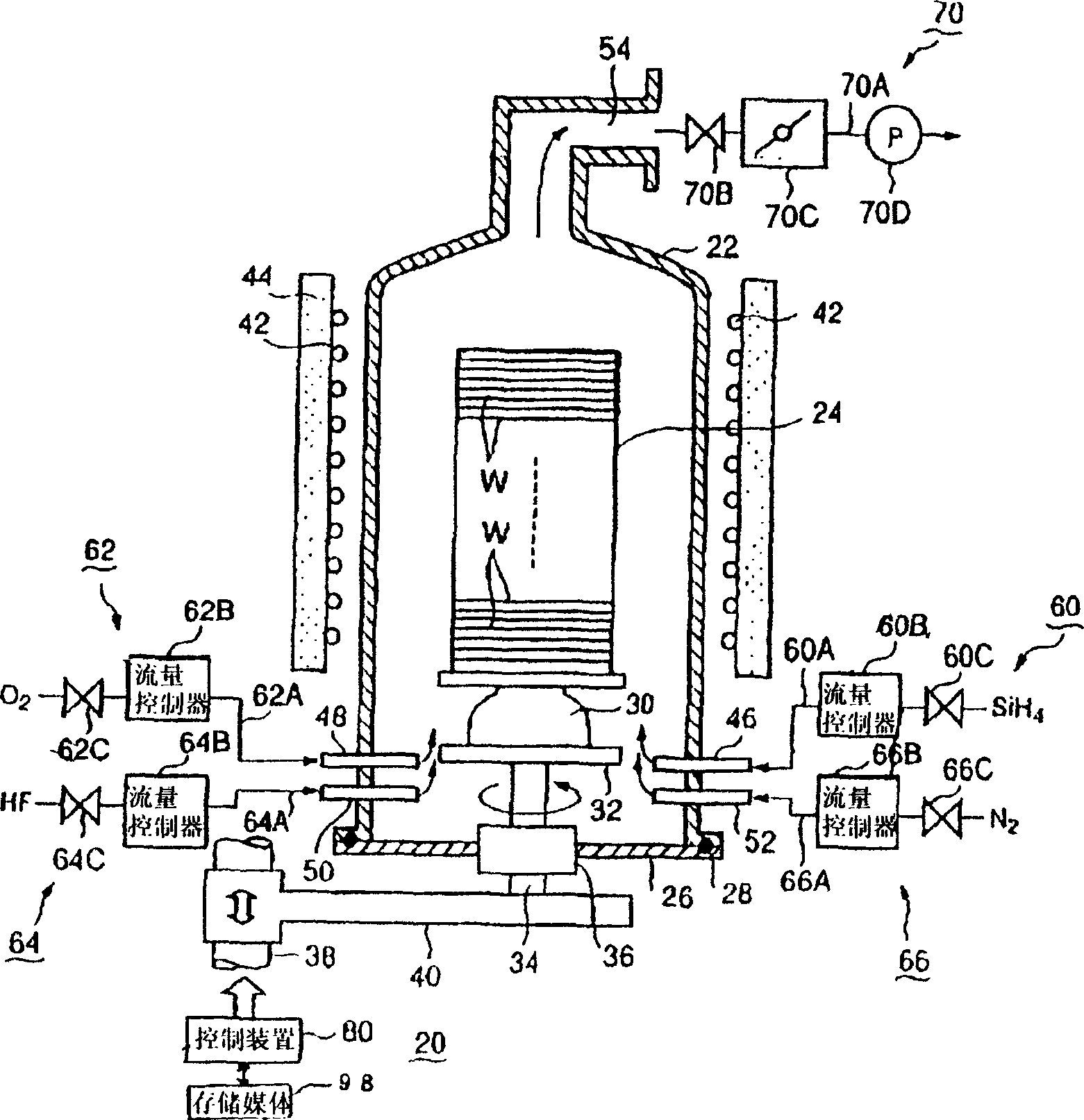

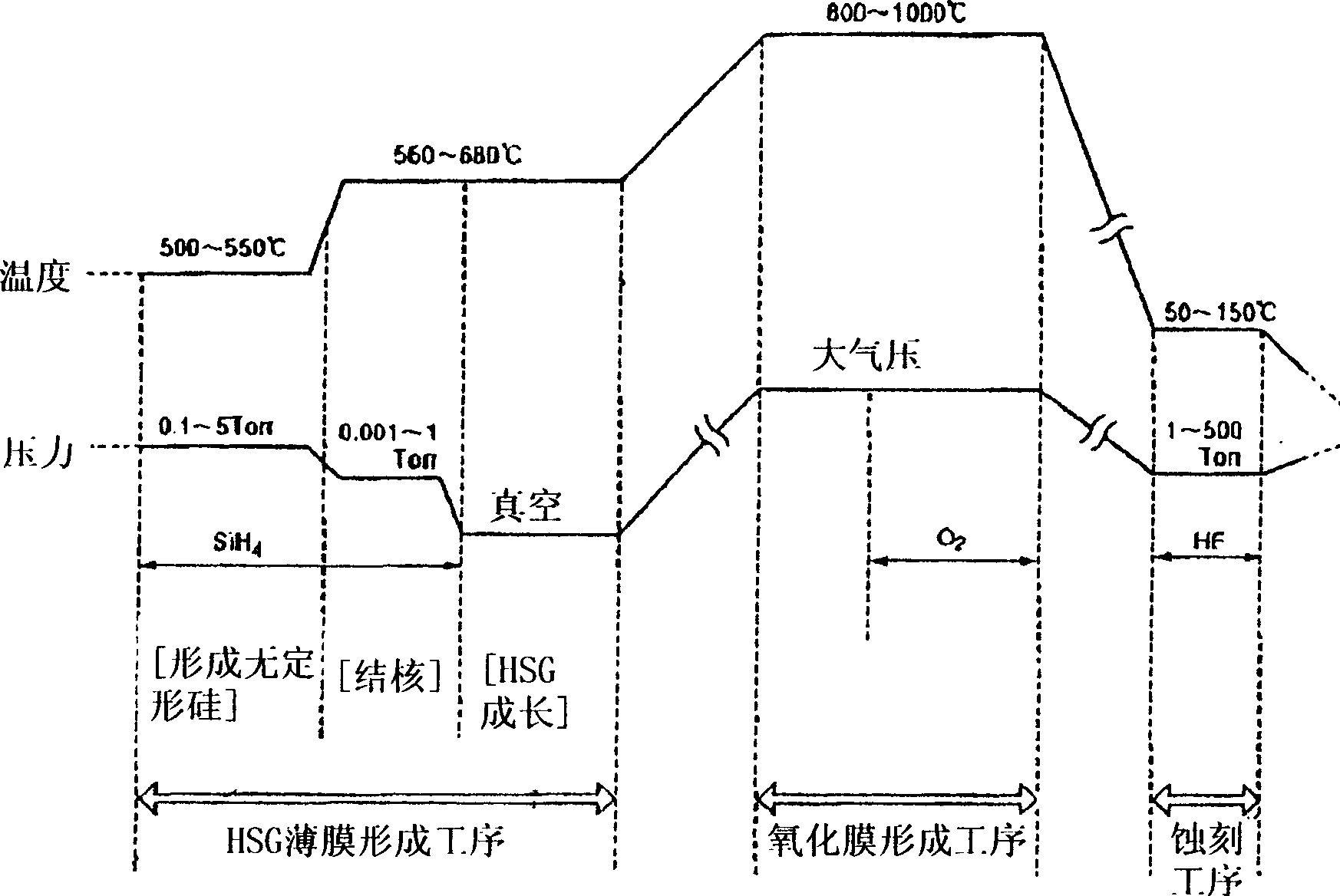

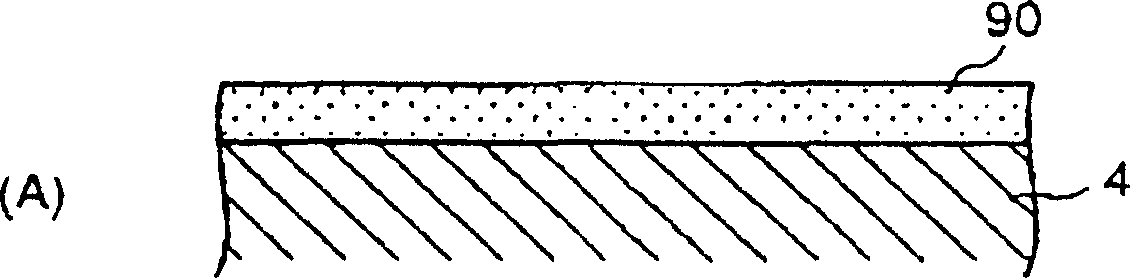

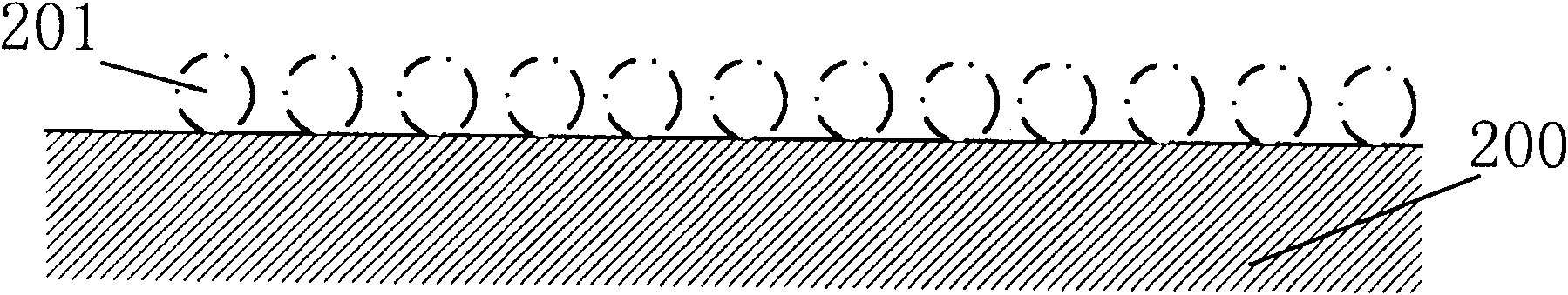

Film forming method, film forming device and storage medium

InactiveCN1734734ASmall design rule sizeDesign rule dimensions are strictSemiconductor/solid-state device manufacturingForming gasOptoelectronics

The present invention provides a film forming method for controlling holocrystalline hemispheric granule in small size by a combination etching treatment. The film forming method of a film formed on surface of the treated object W comprises a host crystal formed on the surface of the treated object by film forming gas, the host crystal grows, the HSG film forming process one the surface of the HSG film formed by holocrystalline hemispheric granule is formed; a hemispherical grained (HSG) film is oxidized to form an oxidized layer at the surface part of the HSG film, and then the oxidized layer is etched to be removed. Thus, the film forming method controls the holocrystalline hemispheric granule in small size by a combination etching treatment.

Owner:TOKYO ELECTRON LTD

Method for forming grid side wall layer

ActiveCN100576451CProtectImprove thickness uniformitySemiconductor/solid-state device manufacturingSemiconductor devicesOptoelectronicsMedia layer

The invention discloses a method of forming a grid wall layer, including the following steps that: a substrate with at least a grid is provided; the method of atomic layer deposit is utilized to form a complex medium layer in the substrate; a side wall layer is formed in the grid by etching the complex dielectric layer. The invention is not only favorable to improve the performance of the parts with lower heat budgeting, but also improves the uniformity of the performance of the parts with better uniformity of the formed grid side wall layer.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

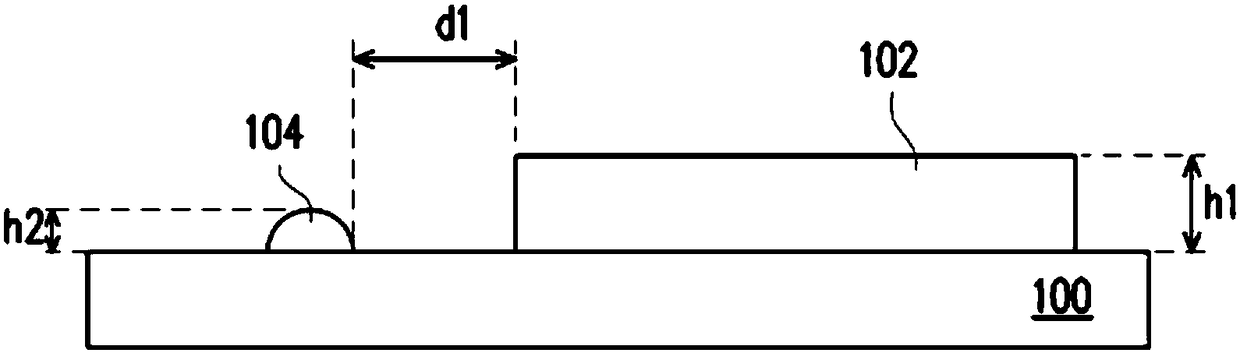

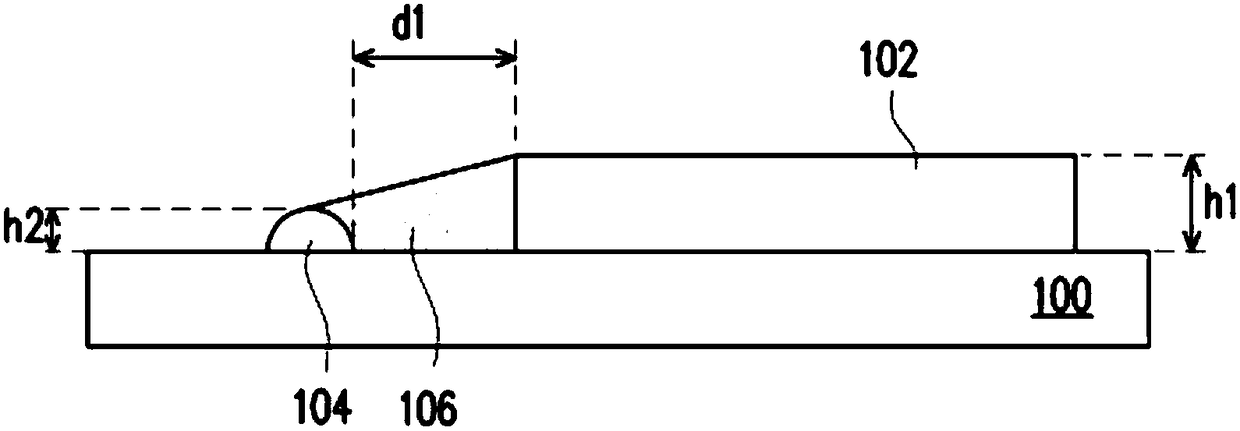

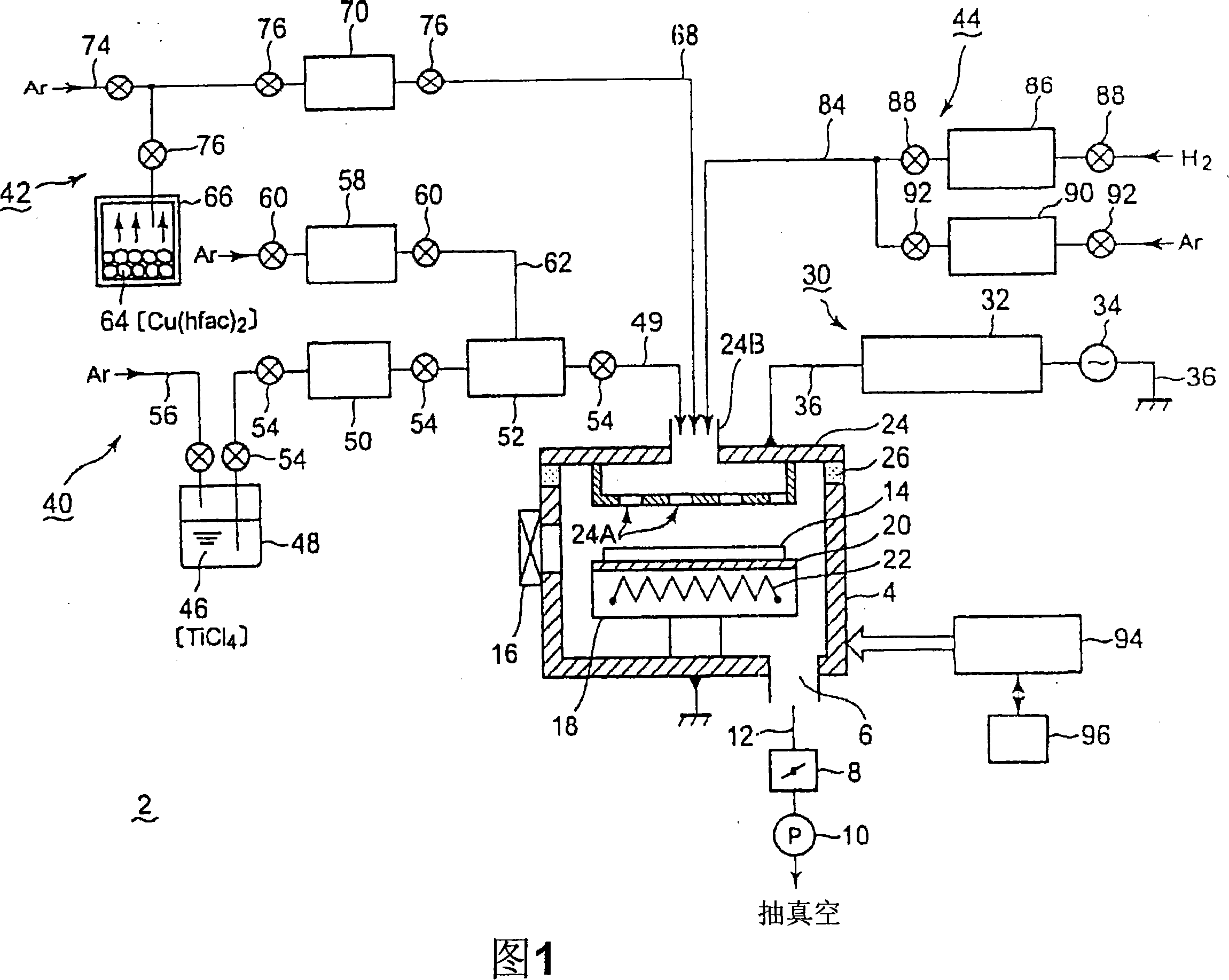

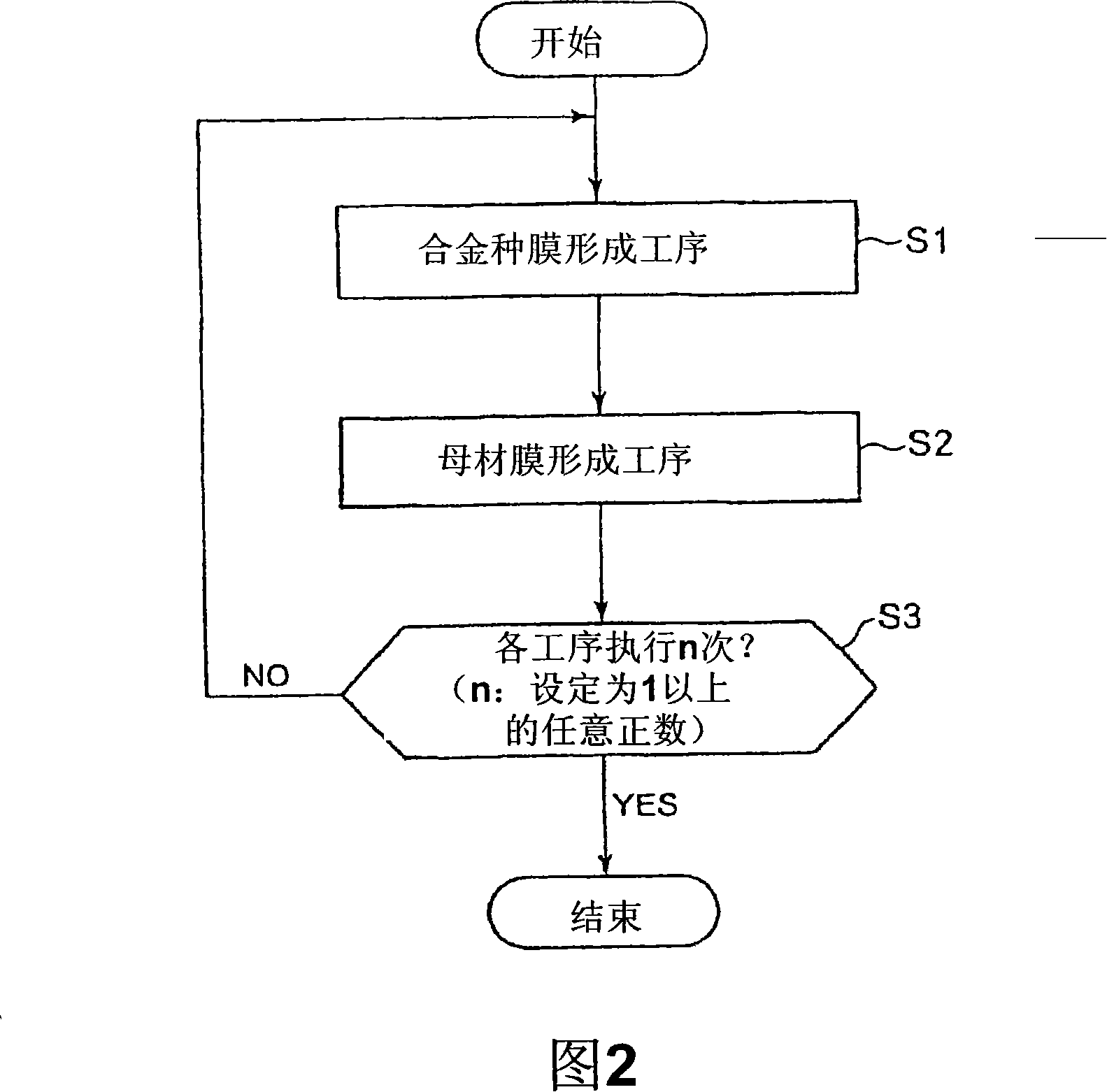

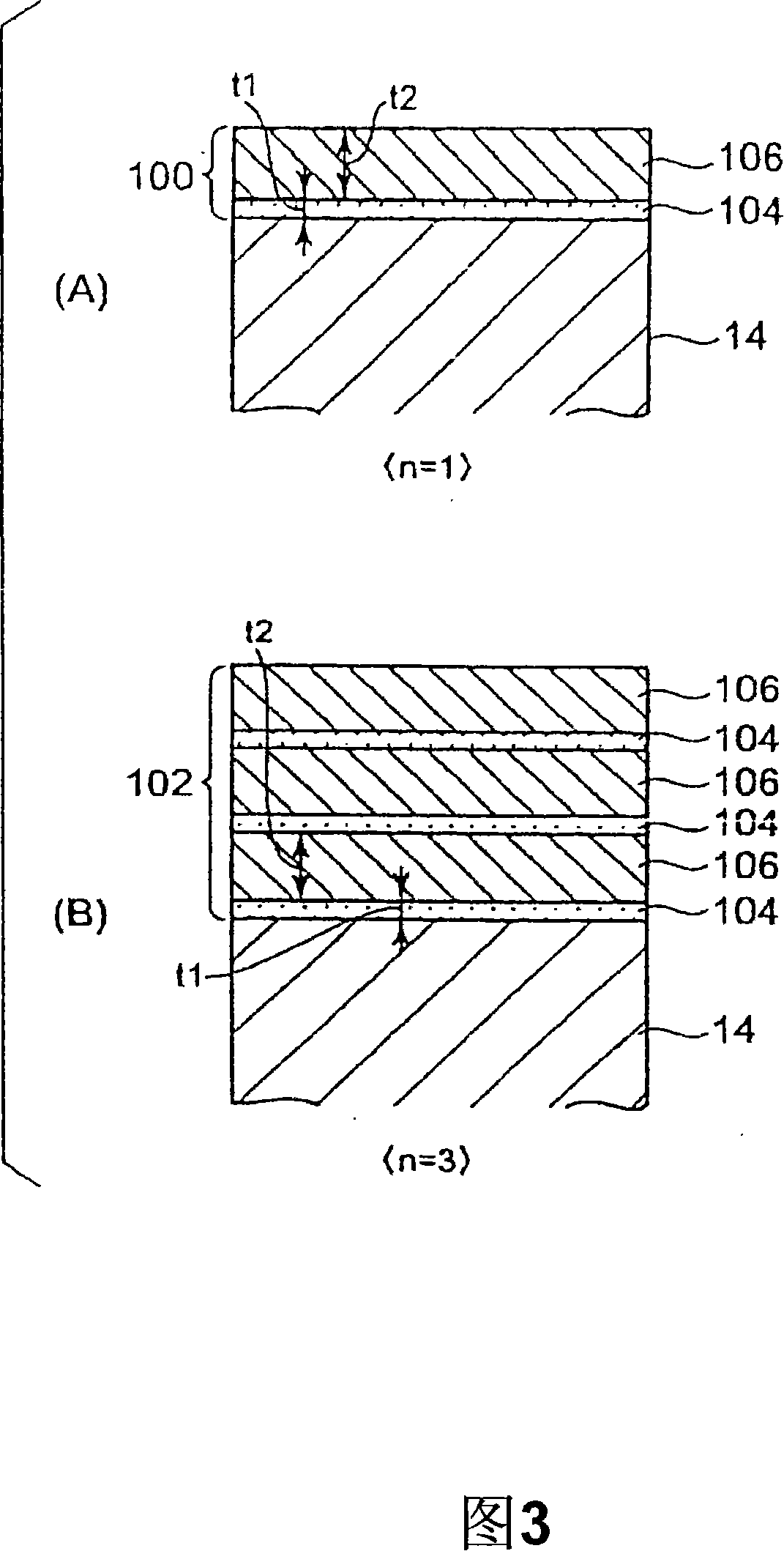

Layered thin film structure, layered thin film forming method, film forming system and storage medium

InactiveCN101115864AExcellent function and effectPrevent peelingChemical vapor deposition coatingThin material handlingMiniaturizationOptoelectronics

The present invention provides a multilayer structure of a thin film that has high adhesion to the substrate, can suppress the occurrence of film peeling, can sufficiently improve the step coverage even if the miniaturization is further developed, and can sufficiently diffuse elements of the alloy species. form method. In this method, multiple layers of thin films are deposited on the surface of the object to be processed in a vacuumable processing container (4) to form a laminated structure of thin films, and the following steps are alternately carried out more than once: A raw material gas of the first metal and a reducing gas, an alloy seed film forming step of forming an alloy seed film (104) composed of the first metal; and a raw material gas containing a second metal different from the above-mentioned first metal as a base material and a reducing gas to form a base material film (106) made of a second metal thicker than the alloy seed film.

Owner:TOKYO ELECTRON LTD

Method for filling contact holes in aluminum metal process

ActiveCN104253087BImprove ladder coverageFully filledSemiconductor/solid-state device manufacturingEtchingAluminum metal

The invention discloses a filling method of an aluminum metal process contact hole. The method comprises the following steps that (1) contact hole etching is carried out on a silicon base plate; (2) the filling of a first blocking layer is carried out; (3) the filling of a first metal aluminum layer is carried out on the surface of the first blocking layer; (4) the filling of a second metal aluminum layer is carried out in a contact hole; (5) the filling of a third metal aluminum layer is carried out on the surfaces of the first metal aluminum layer and the second metal aluminum layer; (6) a second blocking layer is formed on the third metal aluminum layer; (7) metal aluminum wire pattern etching is carried out. The method provided by the invention can be used for effectively carrying out metal aluminum filling, and the generation of holes is avoided.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

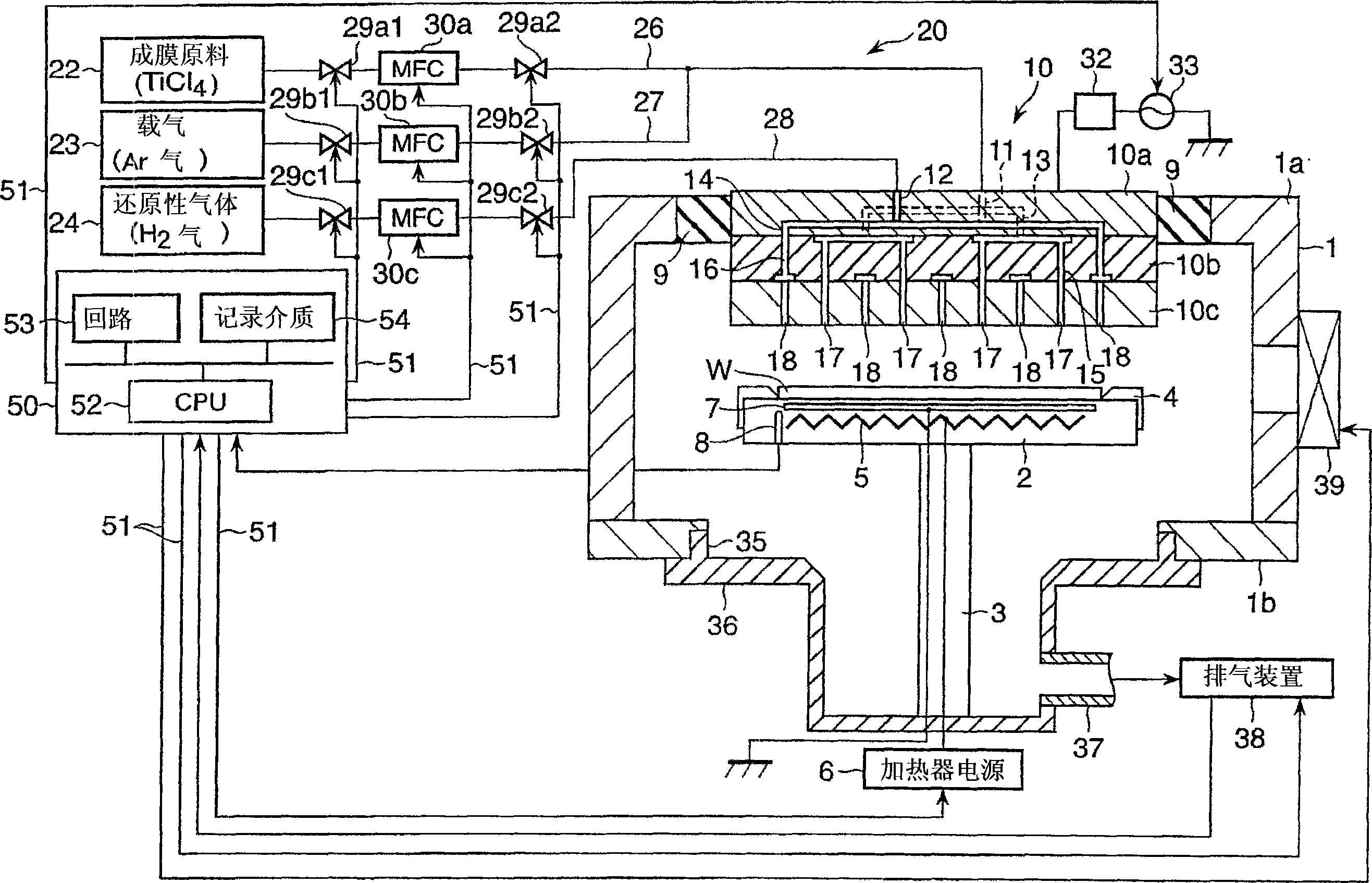

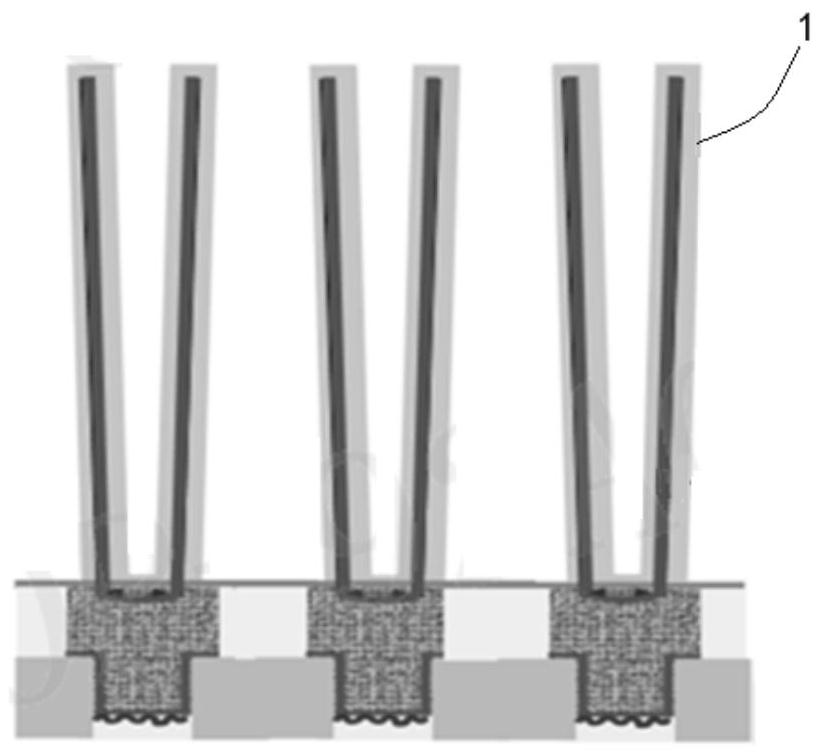

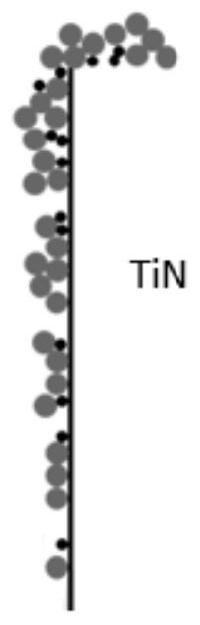

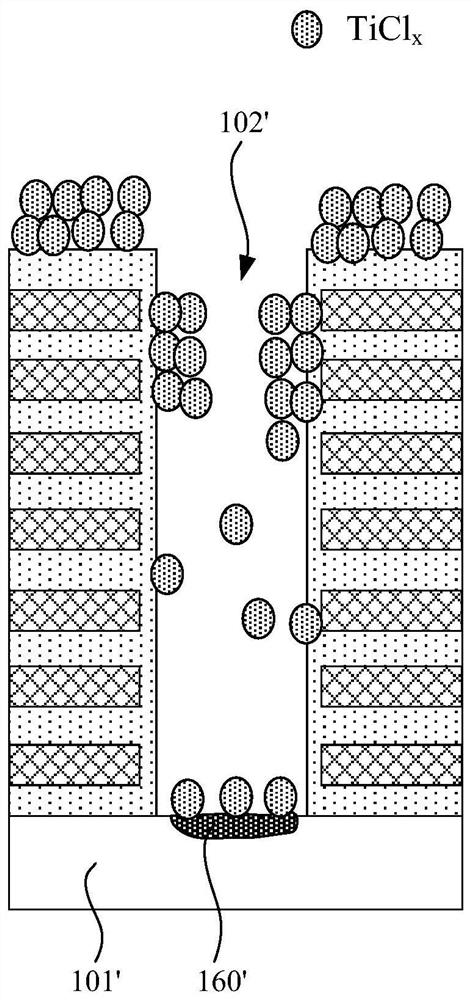

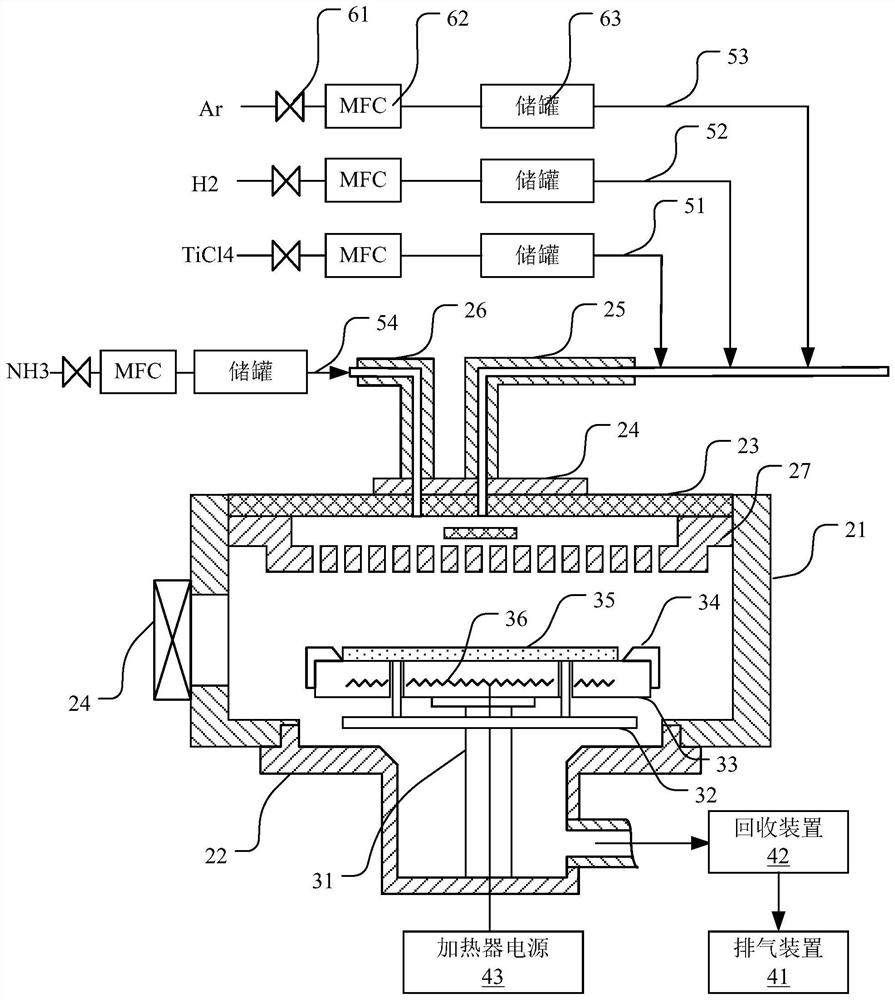

Manufacturing method of 3D storage device and chemical vapor deposition method of adhesive film

ActiveCN111235546BImprove ladder coverageReduce flow rateSemiconductor/solid-state device manufacturingChemical vapor deposition coatingSemiconductor structureReactive gas

The application discloses a manufacturing method of a 3D storage device and a chemical vapor deposition method of an adhesive film. The chemical vapor deposition method includes: placing a semiconductor structure with a deposition channel in a reaction chamber, at least the sidewall of the deposition channel is covered by an oxide layer; 4 The first reaction gas, containing H 2 The second reaction gas and the inert gas, the volume / mass of the first and second reaction gases are preset to a selected ratio; the tail gas is discharged out of the reaction chamber at a preset rate, the first reaction gas, the second reaction gas and the inert gas The reaction produces TiCl x , the second reactant gas with TiCl x The reaction produces a Ti film covering the inner surface of the deposition channel as at least part of the adherent film, and the tail gas includes unreacted TiCl 4 with TiCl x , when the volume / mass ratio of the first reactant gas to the second reactant gas is preset at a selected ratio, the inert gas slows down the TiCl 4 with TiCl x The discharge rate of TiCl reaches the bottom and sidewall of the deposition channel x evenly distributed.

Owner:YANGTZE MEMORY TECH CO LTD

LED chip with stepped current blocking structure and manufacturing method thereof

ActiveCN102751410BImprove electro-optical conversion efficiencyIncrease brightnessSemiconductor devicesPower flowEngineering

The invention provides an LED (Light Emitting Diode) chip provided with a stepped current blocking structure and a fabricating method thereof. The fabricating method comprises the steps of: providing at least one LED epitaxial wafer comprising a substrate and a light emitting epitaxial structure on the LED epitaxial wafer; fabricating the stepped current blocking structure on the surface of the LED epitaxial wafer vertical to a region of a first electrode correspondingly prefabricated; and fabricating transparent conductive layers on the surfaces of the LED epitaxial wafer and the stepped current blocking structure, and then fabricating a first electrode, a second electrode and a protective layer correspondingly. According to the LED chip provided with a stepped current blocking structure and the fabricating method of the LED chip provided with the stepped current blocking structure provided by the invention, the gradient at the edge of the stepped current blocking structure is slowed so that the contact area of the transparent conductive layer and the stepped current blocking structure is increased, the situation that the transparent conductive layer (ITO) on the side wall (at the step) at the edge of the current blocking structure becomes thinner and even breaks can be avoided, the step covering capacity of the transparent conductive layer is improved, the current spreading capacity of the transparent conductive layer is further improved, the electro-optical conversion efficiency of the LED chip is increased, and the brightness of the LED chip is enhanced.

Owner:宁波安芯美半导体有限公司

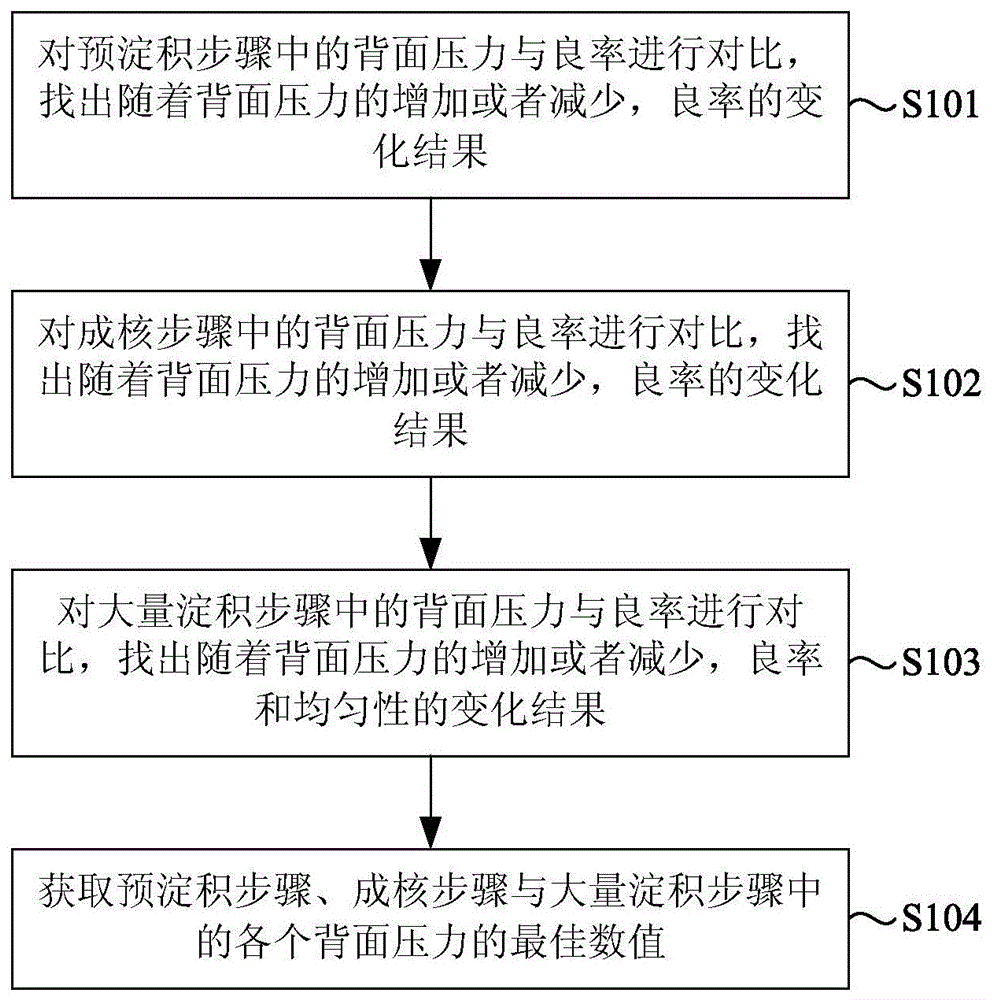

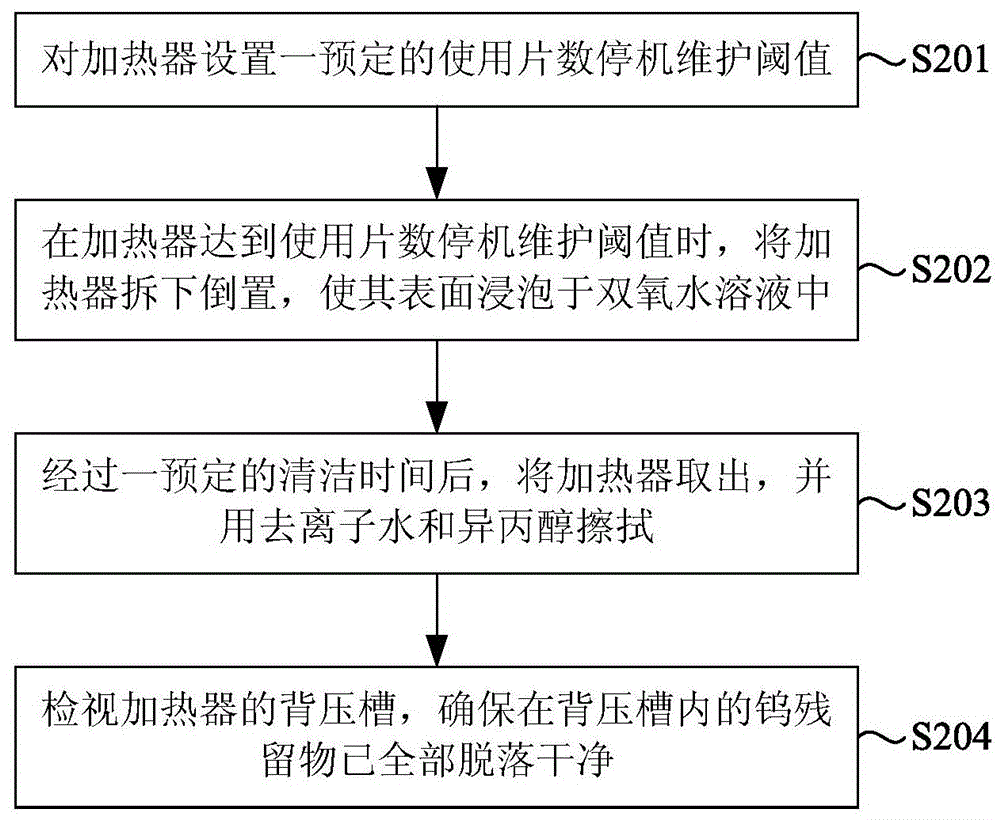

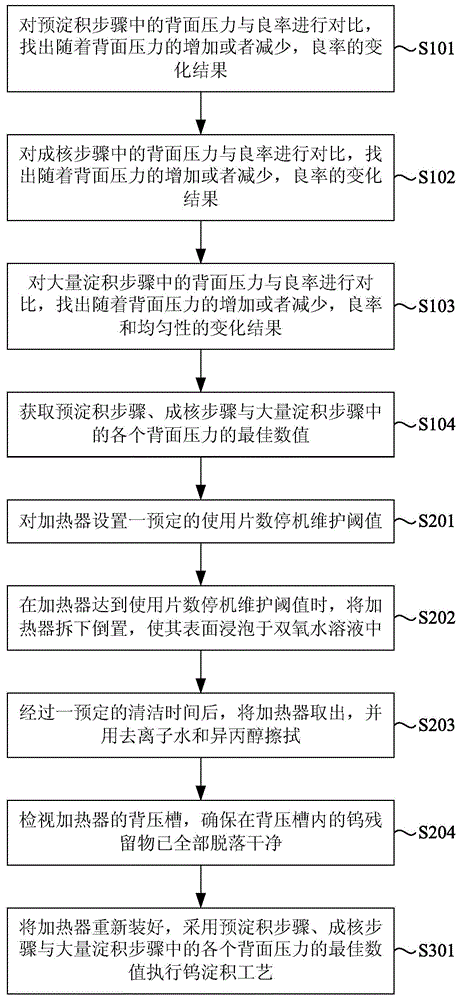

Optimization Method of Back Pressure in Tungsten Deposition Process

ActiveCN104157607BBest back pressure optimization conditionsReduce alarm frequencySolid-state devicesSemiconductor/solid-state device manufacturingEngineeringDeposition process

Owner:ADVANCED SEMICON MFG CO LTD

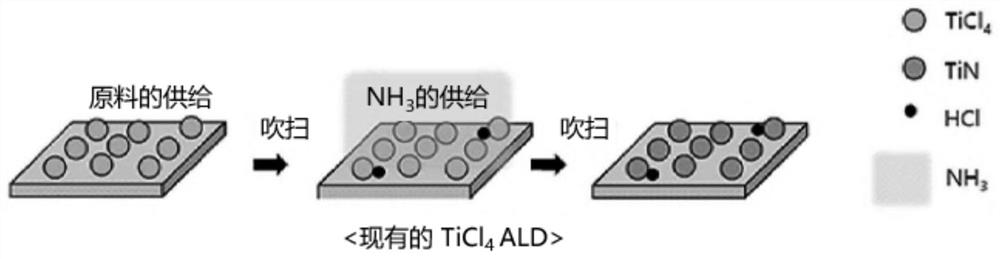

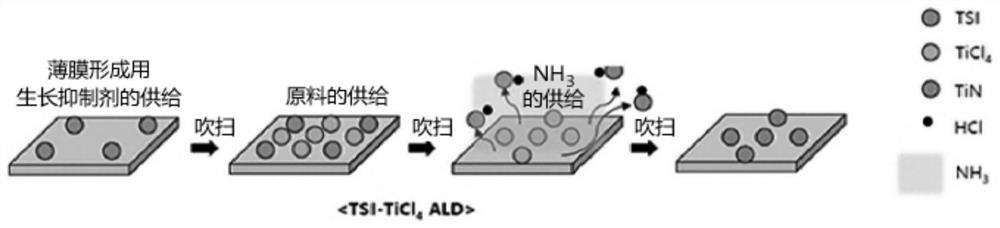

Method for producing thin film

PendingCN112553599AReduced growth rateImprove thickness uniformitySolid-state devicesSemiconductor/solid-state device manufacturingHalogenPhysical chemistry

The present invention relates to a method for producing a thin film, the method comprising: a step (i) for adsorbing a growth inhibitor for forming a thin film represented by chemical formula 1 onto the surface of a substrate; and ii) adsorbing a Ti-based thin film precursor onto the surface of the substrate to which the growth inhibitor for thin film formation has been adsorbed. According to thepresent invention, by suppressing side reactions, reducing the growth rate of a thin film, and removing process by-products in the thin film, the step coverage rate and the thickness uniformity of thethin film are greatly improved even when the thin film is formed on a substrate having a complex structure. Chemical formula 1: AnBmXo, where A is carbon or silicon, B is hydrogen or an alkyl group having 1 to 3 carbon atoms, X is halogen, n is an integer of 1 to 15, o is an integer of 1 or more, and m is 0 to 2n+1.

Owner:SOULBRAIN CO LTD

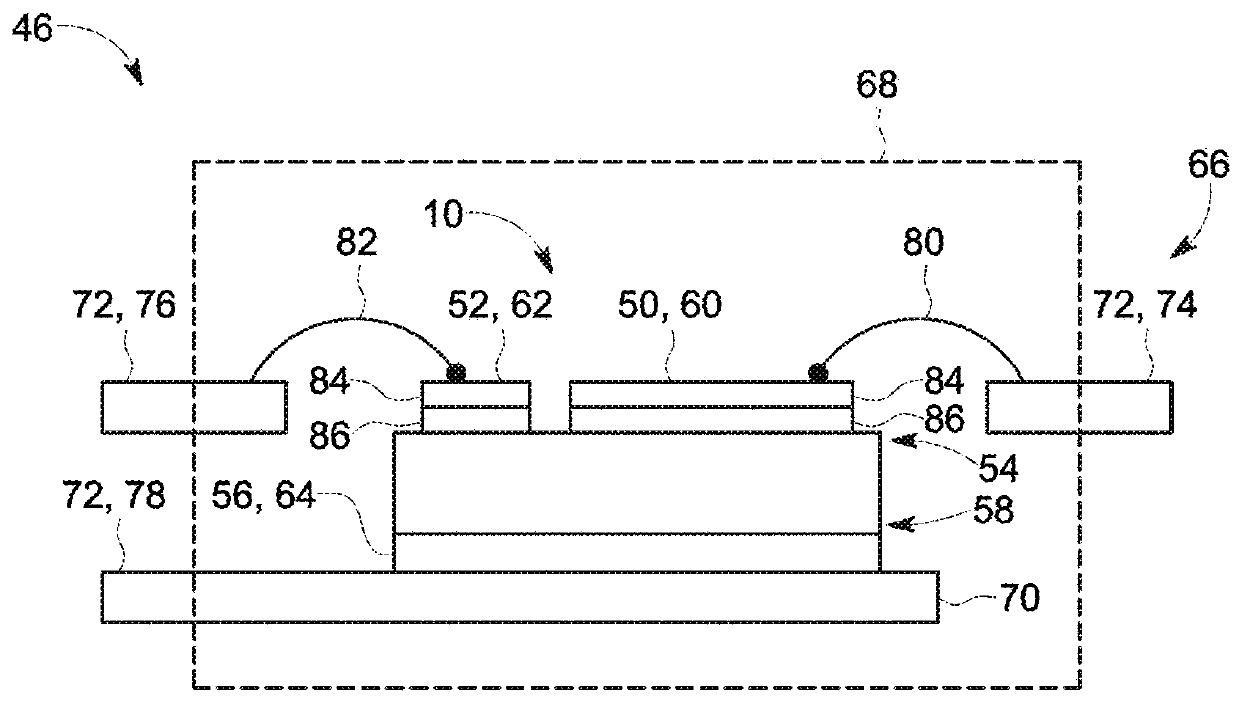

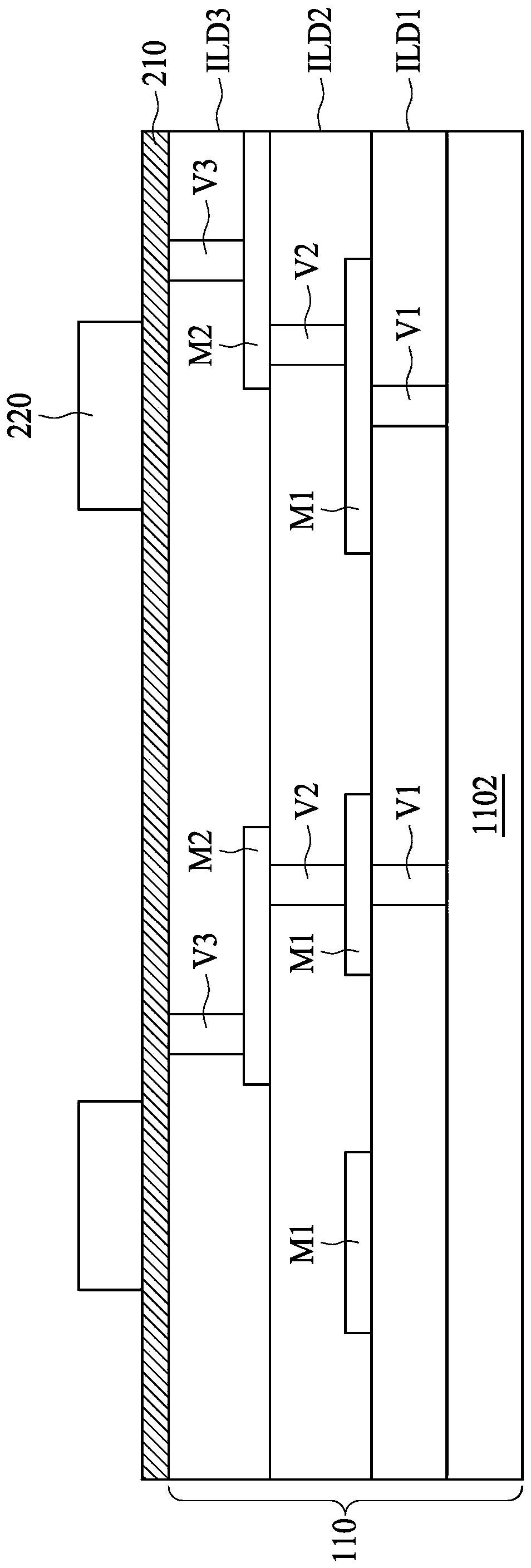

Electronic device and method of manufacturing the same

InactiveCN111261579AImprove ladder coverageAvoid the problem of poor ladder coverageSemiconductor/solid-state device detailsSolid-state devicesContact padEngineering

The present disclosure provides an electronic device and a method of manufacturing the same. The electronic device includes a multilayer component, at least one contact pad, a passivation layer, a dielectric layer, and a metallic layer. The contact pad is disposed on the multilayer component, the passivation layer covers the multilayer component and the contact pad, and the dielectric layer is disposed on the passivation layer. The metallic layer penetrates through the dielectric layer and the passivation layer and is connected to the contact pad, and the metallic layer discretely tapers at positions of decreasing distance from the contact pad.

Owner:NAN YA TECH

Method for making wear-resistant dielectric layer

InactiveCN100437936CImprove ladder coverageSimple structureSemiconductor/solid-state device manufacturingWear resistantGas phase

The invention firstly provides a substrate comprising plural connection pads, successively at least makes a plasma auxiliary chemical vapour deposition process to deposit a dielectric layer on the substrate surface, where the vapour deposition process is made in a high frequency-low frequency plasma alternating mode, and finally makes an anisotropic etching process to form plural openings in the dielectric layer, where these openings correspond to the connection pads and side wall of each opening is inclined outward.

Owner:TOUCH MICRO SYST TECH

Organometallic compounds and thin film using same

ActiveCN111655702AIncrease relative volatilityGood chemical stabilityGroup 5/15 element organic compoundsSemiconductor/solid-state device manufacturingEquivalent oxide thicknessHeat stability

Owner:艾慕化学株式会社

Flash memory unit forming method

ActiveCN102569078BUniform thicknessImprove ladder coverageSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringChemical vapor deposition

Owner:SEMICONDUCTOR MANUFACTURING INTERNATIONAL (BEIJING) CORP