Neural network tensor processor

A neural network and processor technology, applied in the field of artificial intelligence chips, can solve the problems of unfavorable computing efficiency, improvement, and not being widely used, and achieve the effect of improving computing efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

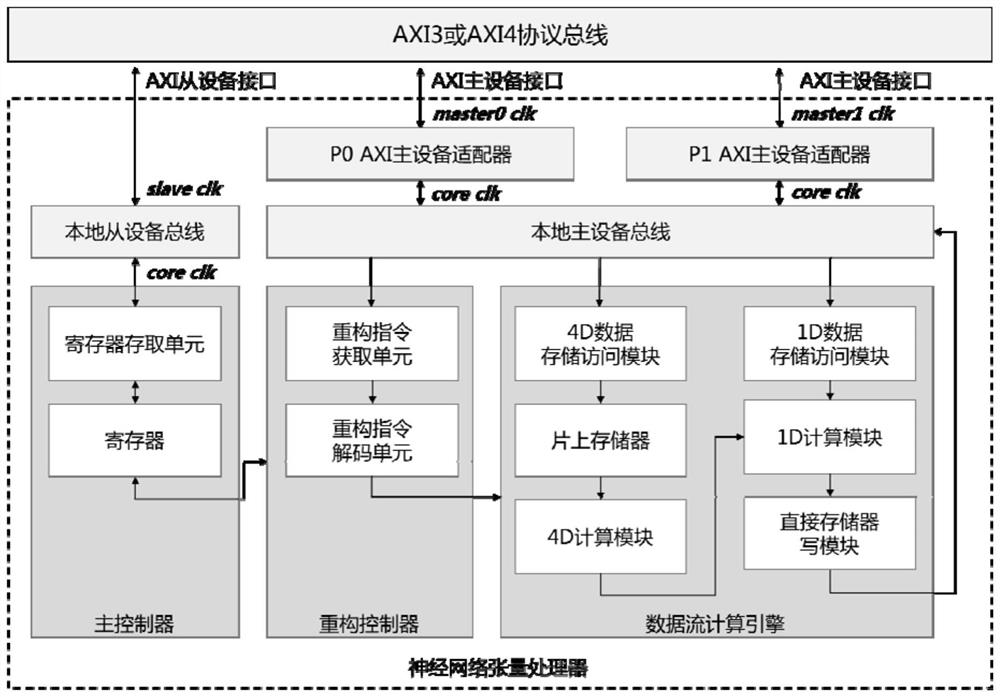

[0046] Such as figure 1 As shown, the technical solution of this embodiment is to provide a hardware architecture of a neural network tensor processor, figure 1 shown. It mainly consists of three parts: Host Controller, Reconfiguration Controller, and Data-flow Computing Engine.

[0047] In order to improve the flexibility of system integration, the tensor processor adopts the asynchronous clock scheme between the system core and the AXI bus interface. The system uses four completely independent asynchronous clocks to realize the isolation between the tensor processor core and the external system. Among them, the AXI slave device interface uses one AXI slave device bus clock (slave clk), the AXI master device interface uses two AXI master device bus clocks (master0 clk and master1 clk), and the tensor processor core uses the core clock (coreclk).

[0048] The main function of the main controller is to provide traditional software control and status interface to the external ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More