Self-reference storage structure and storage and calculation integrated circuit

A storage structure and self-referencing technology, applied in the field of memory, can solve the problems of low magnetic tunnel junction tunneling magneto-resistance, disadvantageous circuit integration, and low read margin.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

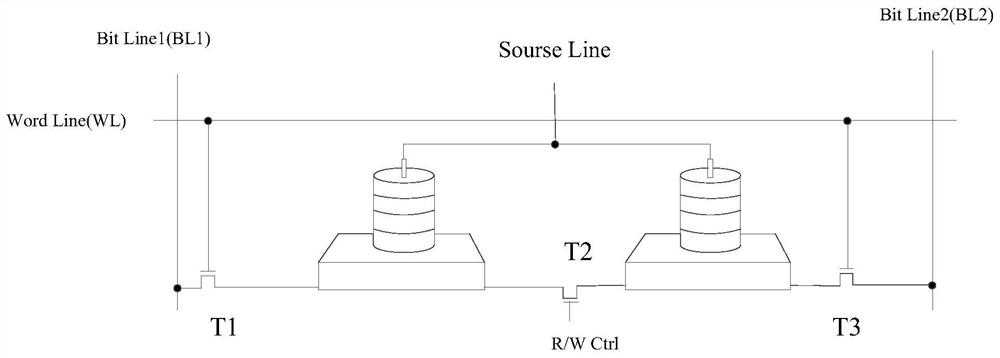

[0058] Embodiments of the present invention provide a self-referencing storage structure, such as figure 1 As shown, it includes: three transistors, including: a first transistor T1, a second transistor T2, and a third transistor T3; two magnetic tunnel junctions, including: a first magnetic tunnel junction MTJ0, a second magnetic tunnel junction MTJ1; a first The magnetic tunnel junction MTJ0 is connected in series between the first transistor T1 and the second transistor T2; the word line WL; the second magnetic tunnel MTJ1 junction is connected in series between the second transistor T2 and the third transistor T3; the first gate of the first transistor T1 Both the pole and the third gate of the third transistor T3 are connected to the word line WL; when the first transistor T1, the second transistor T2, and the third transistor T3 are turned on, the writing of one-bit binary information is realized.

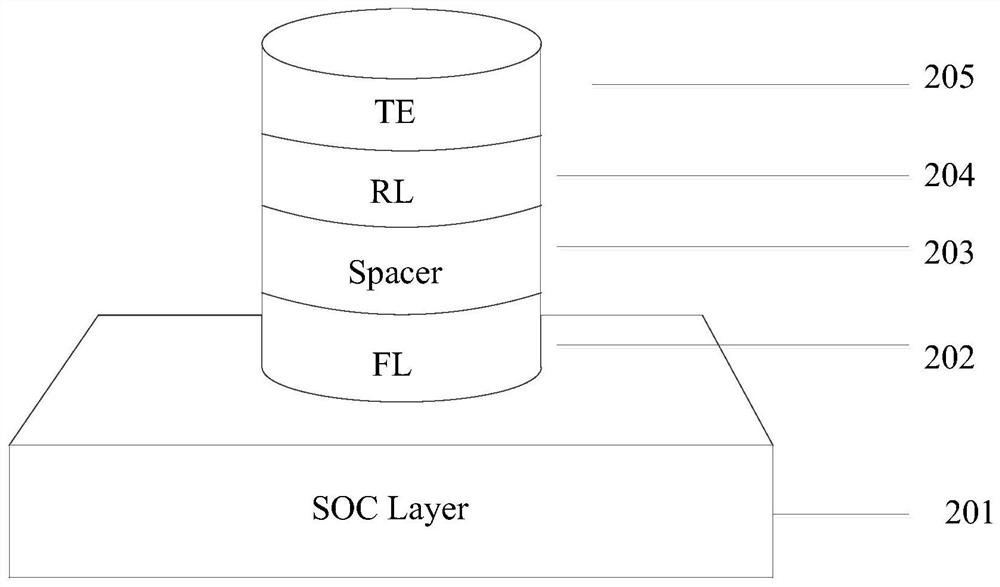

[0059] Among them, such as figure 2 As shown, the first magnetic tunne...

Embodiment 2

[0089] An embodiment of the present invention provides an integrated storage and calculation circuit, such as Figure 6 As shown, it includes: a storage unit 601 , an asymmetric sense amplifier 602 and a voltage generating circuit 603 .

[0090] The storage unit 601 includes a plurality of parallel self-reference storage structures, and the storage unit generates a voltage difference between an induced voltage and a reference voltage under the action of a current.

[0091] The asymmetric sense amplifier 602 includes two transistors of different sizes.

[0092] The voltage generating circuit 603 is connected between the storage unit 601 and the asymmetric sense amplifier 602, and is used for inputting the voltage difference between the induced voltage and the reference voltage into the asymmetric sense amplifier 602, so as to realize a high read margin Data reading and logical operation functions.

[0093] Take gating a set of self-referencing storage structures as an example...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More