Many-core definable distributed shared storage structure

A shared storage and distributed technology, which is applied in the direction of general stored program computer, architecture with multiple processing units, memory address/allocation/relocation, etc., can solve the problem of not supporting ping-pong operation, reduced processor performance, and distance parallel access Blocking and other issues to achieve the effect of improving access bandwidth and data throughput, and improving performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment approach

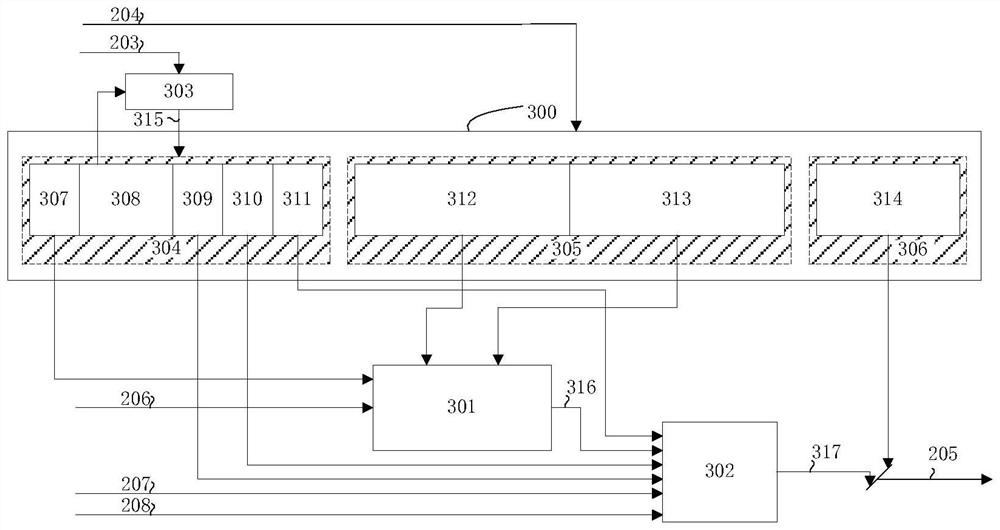

[0061] (1) In many-core processors, multiple processor cores and memory modules are integrated to construct a two-dimensional grid architecture. Each processor core corresponds to a routing unit, and the processor core can be a microprocessor or a DSP acceleration engine that completes specific functions. Each processor core corresponds to a network interface unit. The network interface unit realizes the format conversion of the data packets transmitted between the processor core and the routing unit. The network interface unit integrates a routing table inside, and it directly queries the destination coordinates according to the address sent by the processor core. , after the destination coordinate is added to the packet header of the data packet, the data packet can reach the memory module to be accessed through the routing unit under the guidance of the destination coordinate.

[0062] (2) In many-core processors, multiple processor cores and memory modules are integrated t...

Embodiment

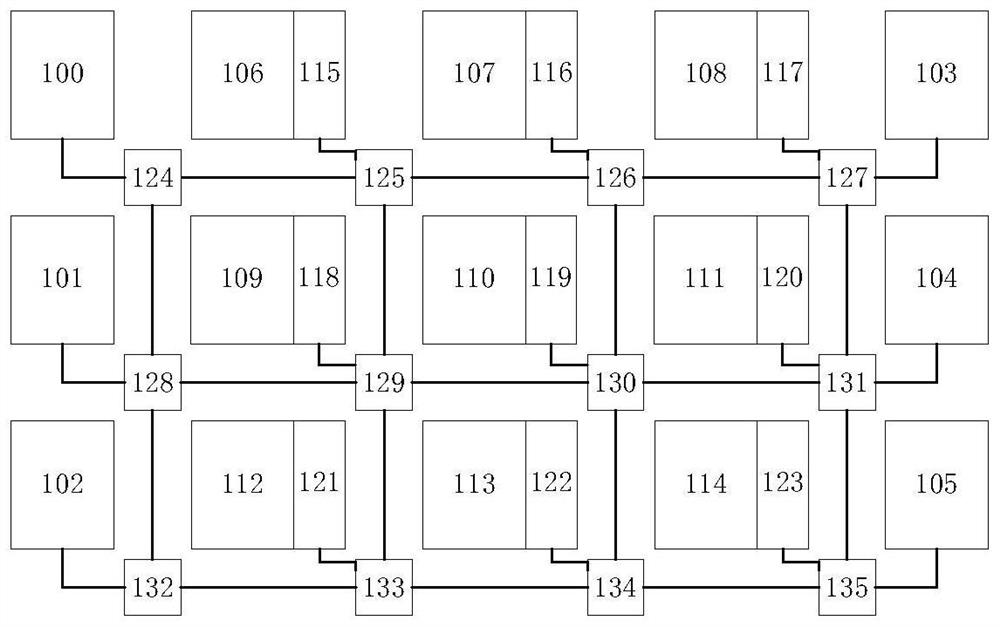

[0069] figure 1 It is the overall structure diagram of the many-core processor.

[0070] exist figure 1 Among them, there are 6 memory modules, numbered 100-105; 9 processor cores, numbered 106-114; 9 network interface units, numbered 115-123; 12 routing units, numbered 124 ~135.

[0071] The memory module labeled 100 is connected to the routing unit labeled 124 through a bidirectional data line.

[0072] The memory module labeled 101 is connected to the routing unit labeled 128 through a bidirectional data line.

[0073] The memory module labeled 102 is connected to the routing unit labeled 132 through a bidirectional data line.

[0074] The memory module labeled 103 is connected to the routing unit labeled 127 through a bidirectional data line.

[0075] The memory module labeled 104 is connected to the routing unit labeled 131 through a bidirectional data line.

[0076] The memory module labeled 105 is connected to the routing unit labeled 135 through a bidirectional d...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More