Circuit verification method and device, electronic equipment and storage medium

A verification method and circuit technology, applied in CAD circuit design, special data processing applications, etc., can solve the problems of low verification efficiency, waste of energy and time, and achieve the effect of avoiding energy and time and improving efficiency.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

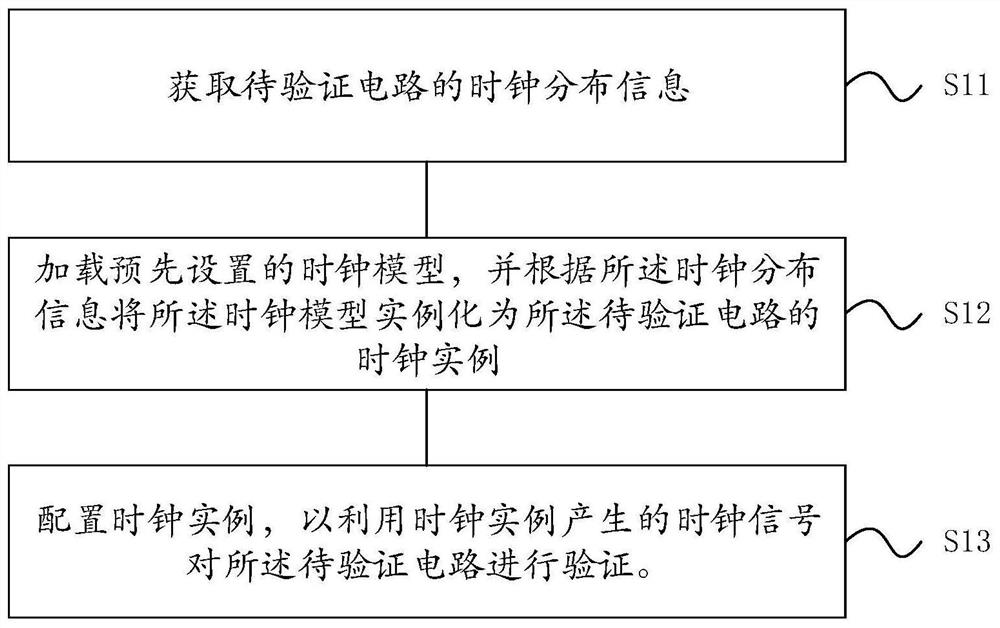

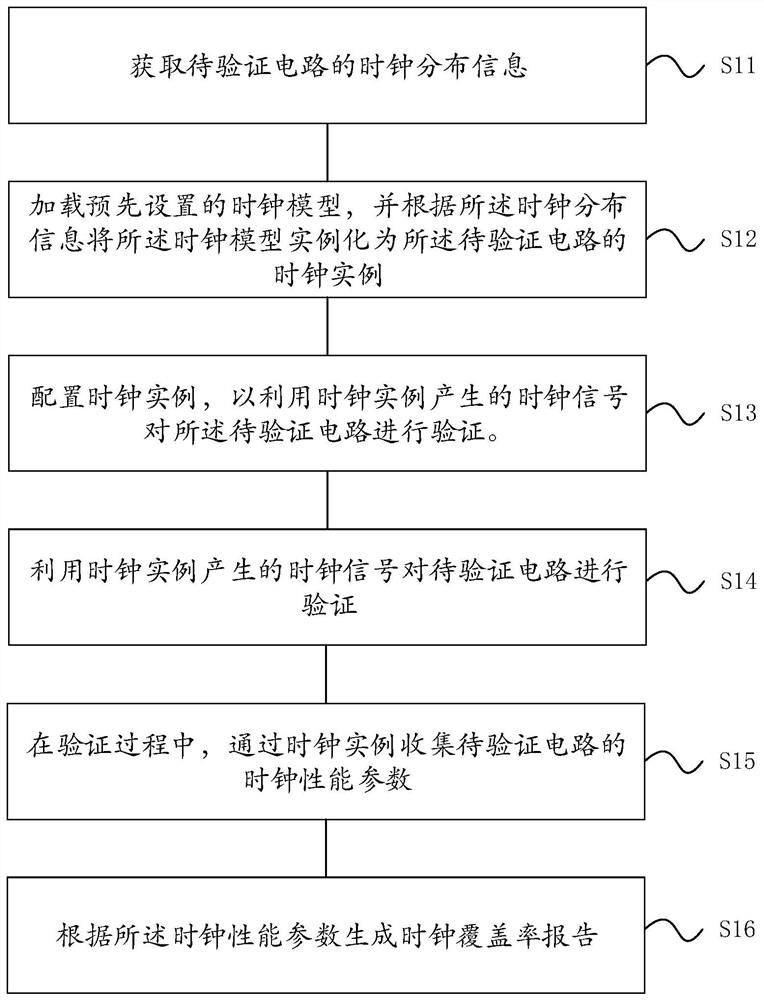

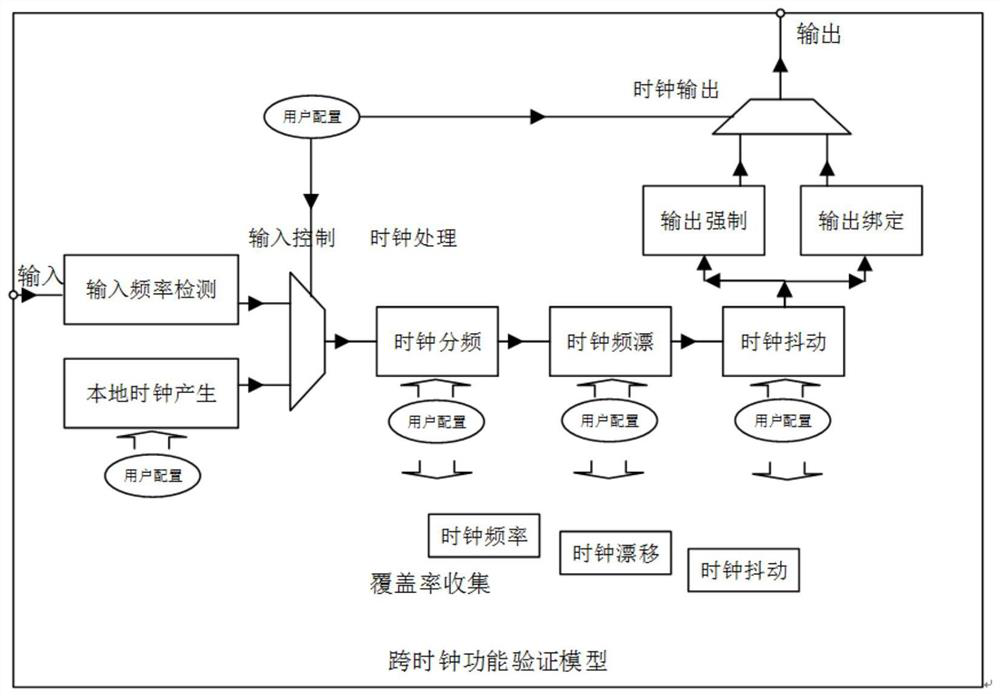

[0035] Embodiments of the present application will be described in detail below in conjunction with the accompanying drawings.

[0036] It should be clear that the described embodiments are only some of the embodiments of the present application, not all of the embodiments. Based on the embodiments in this application, all other embodiments obtained by persons of ordinary skill in the art without creative efforts fall within the protection scope of this application.

[0037] The clock of a large chip is very complex, and the interaction between different clock domains is also very frequent. Because the clocks in different clock domains are independent of each other, the timing relationship in combination is very complex. Generally, designers can only consider limited combination possibilities. According to these possibilities, appropriate cross-clock domain design schemes are selected. Once there is an omission, the design scheme Whether it still works is a risk. This poses ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More