Convolution operation acceleration method for carrying out weight splitting according to bit precision

A convolution operation and bit precision technology, applied in the field of convolution operation acceleration, can solve the problem of limited multiplication reduction, and achieve the effect of increasing the upper limit of parallelism, high algorithm parallelism, and reducing data access time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

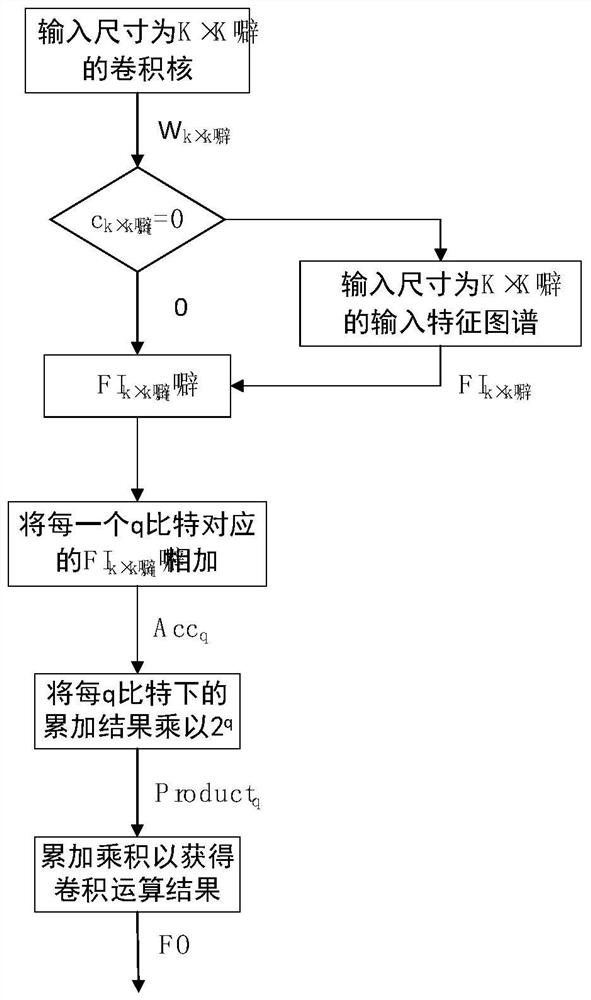

Method used

Image

Examples

Embodiment

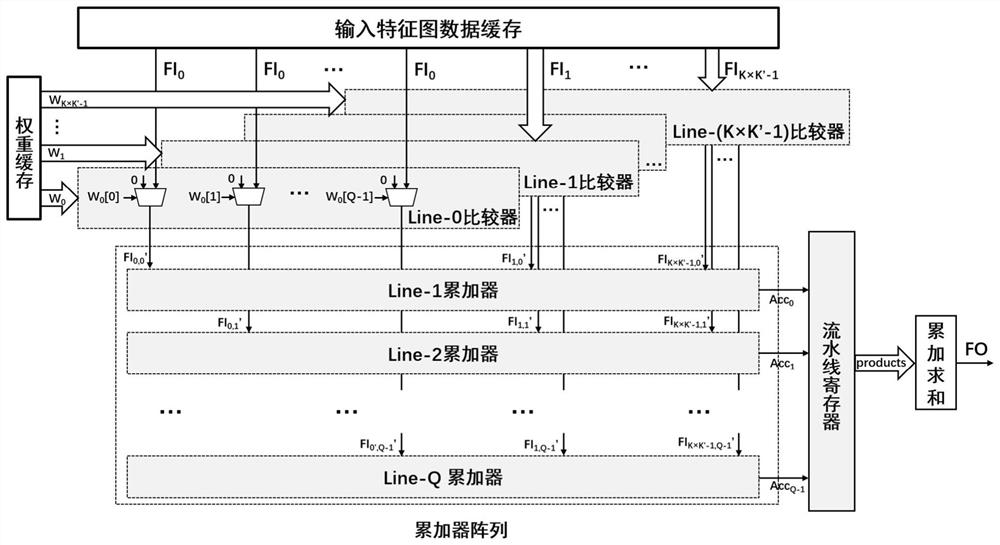

[0096] Taking the 8-bit quantized 3×3 convolution kernel as an example, in this test, the hardware structure of MF-Conv can be specifically expressed as:

[0097] (A), 9 groups of comparator arrays, wherein each group is composed of 8 1-bit comparators;

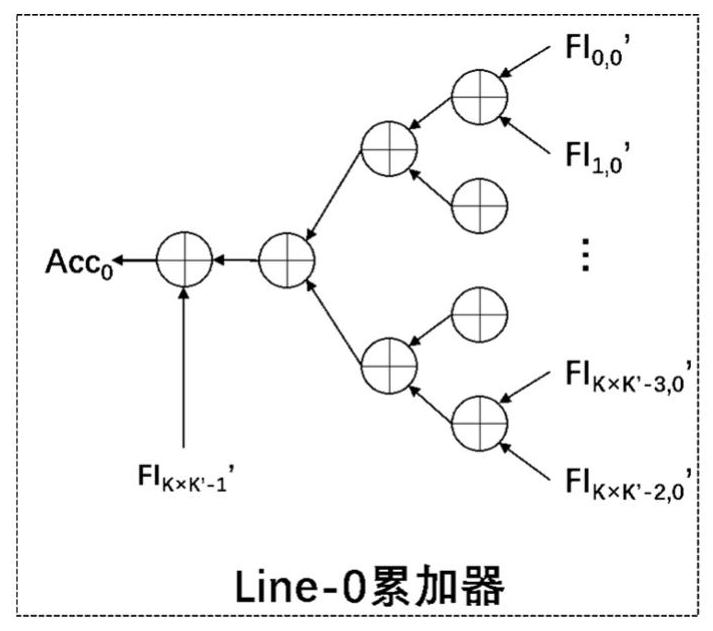

[0098] (B), an accumulator array, is made up of 8 accumulators, wherein each accumulator is made up of 8 adders;

[0099] (C), pipeline register;

[0100] (D), accumulating summation logic block, is made of 7 adders;

[0101] According to the division method of the present invention, the critical path of the circuit is truncated by the pipeline register between the accumulator array and the accumulation and summation logic block, so that the circuit obtains a higher clock frequency, thereby improving the efficiency of convolution calculation. Compared with the existing convolution calculation acceleration method, the present invention completely avoids the multiplication calculation, and further improves the upper limit of ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More