Data storage and reading method of high-speed data acquisition and storage system

A high-speed data acquisition and storage system technology, applied in memory systems, electrical digital data processing, instruments, etc., can solve problems such as inability to meet data acquisition system requirements, data flushing of interface buffers, bandwidth reduction, etc., to avoid secondary Copy, improve transmission efficiency, improve the effect of transmission efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

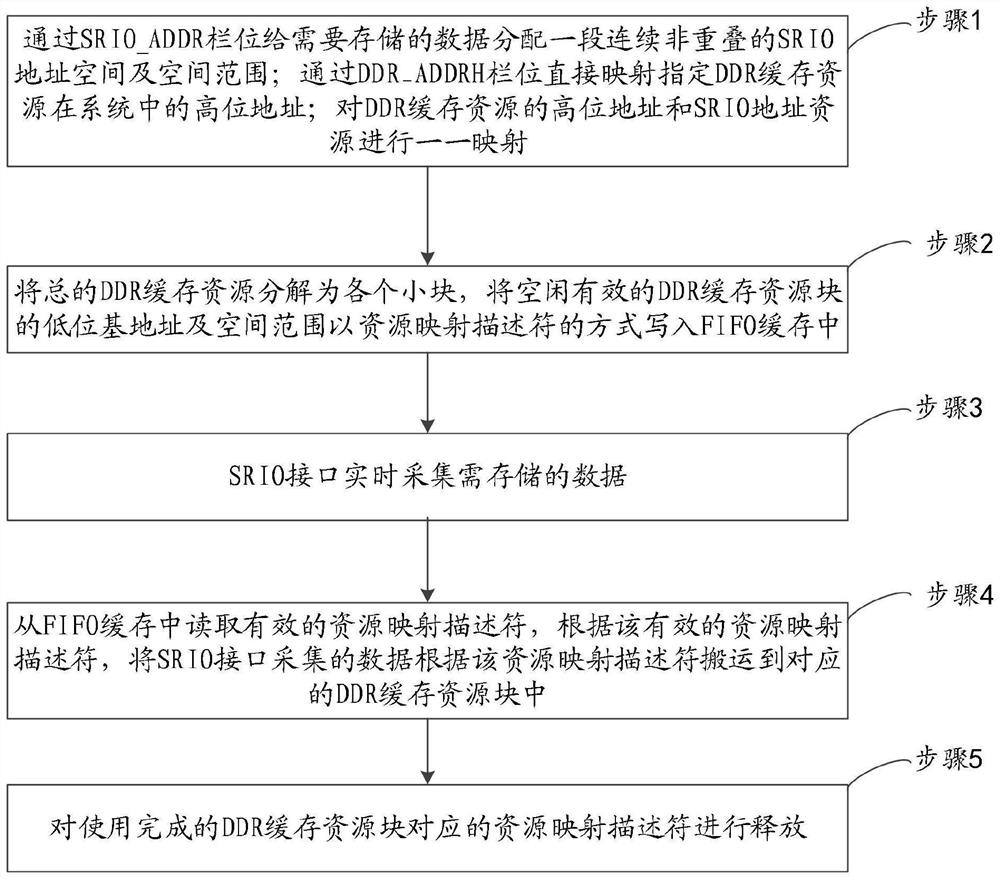

[0047] Embodiment 1 provided by the present invention is an embodiment of a data storage method of a high-speed data acquisition and storage system provided by the present invention, and the embodiment of the method includes:

[0048] Step 1, assign a continuous non-overlapping SRIO address space and space range to the data to be stored through the SRIO_ADDR field; directly map the high address of the designated DDR cache resource in the system through the DDR_ADDRH field; the high address of the DDR cache resource and SRIO address resources are mapped one by one.

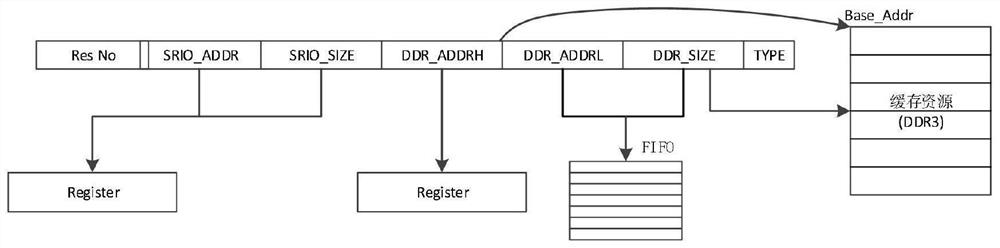

[0049] Step 2, decomposing the total DDR cache resource into each small block, and writing the low-order base address and space range of the free and effective DDR cache resource block into the FIFO cache in the form of a resource mapping descriptor;

[0050] Specifically, in step 2, the resource mapping descriptor corresponding to the low base address and space range of the free and effective DDR cache resource bl...

Embodiment 2

[0068] Embodiment 2 provided by the present invention is an embodiment of a data reading method of a high-speed data collection and storage system provided by the present invention, and the data reading method is based on the data storage method of a high-speed data collection and storage system provided by the present invention Embodiment, after the above data storage method also includes:

[0069] Step 6, read the completed resource mapping descriptor from the Complete Queue module;

[0070] Specifically, in step 6, the completed cache resource mapping descriptor in the FIFO cache is read by reading the fullness status of the Complete Queue module or by means of an interrupt.

[0071] Step 7, extract the SIRO address from the SRIO interface packet and compare it with the completed resource mapping descriptor, determine the corresponding resource mapping descriptor, and store the corresponding DDR cache resource block according to the corresponding resource mapping descriptor...

Embodiment 3

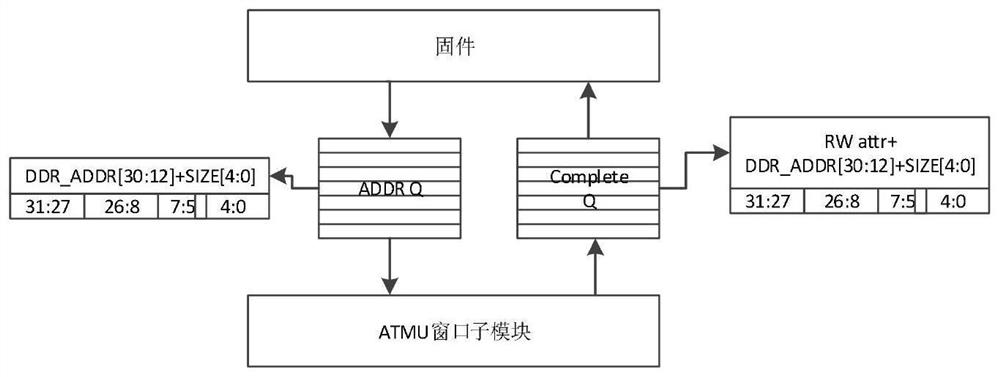

[0074] Embodiment 3 provided by the present invention is a specific application embodiment of a data storage and reading method for a high-speed data acquisition and storage system provided by the present invention, such as image 3 Shown is a schematic structural diagram of a data storage and reading device provided by an embodiment of the present invention, which consists of image 3 It can be seen that the device for data storage and reading is composed of ATMU module, ADDR Queue module, Complete Queue module and firmware.

[0075] The ATMU module mainly completes the conversion function of the SRIO interface address space to the internal DDR address space, and realizes the direct mapping of the data address space.

[0076] The firmware module mainly runs the software code on the processor to realize the management and scheduling of DDR3 external memory storage resources, and configure the SRIO interface through the AXI Lite configuration bus.

[0077] The ADDR Queue modul...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More