Three-dimensional memory and preparation method thereof

A memory, three-dimensional technology, applied in the direction of electric solid-state devices, semiconductor devices, electrical components, etc., can solve the problems of gate layer breakdown, gate layer short circuit, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

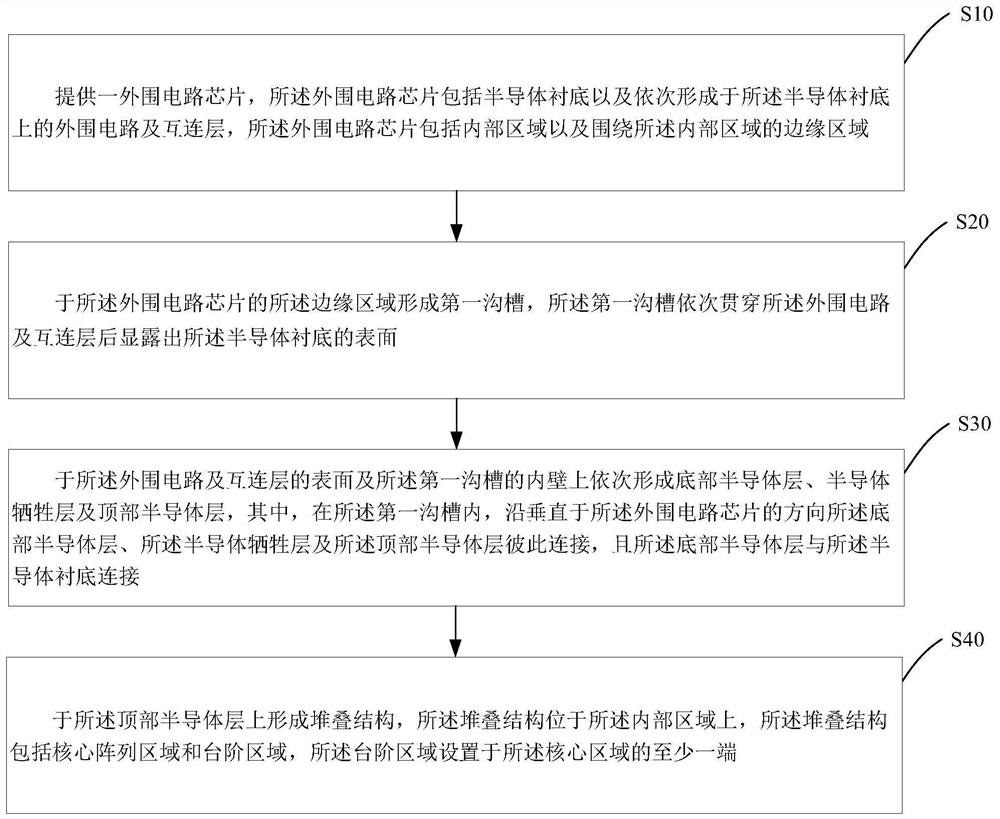

[0164] figure 1 The preparation flow chart of the three-dimensional memory of the embodiment of the present invention is shown, and the three-dimensional memory is based on the Under Core Arby, the PUC) architecture, that is, the peripheral circuit chip is located below the stacked structure. See figure 1 The three-dimensional memory preparation method comprises:

[0165] Step S10 provides an peripheral circuit chip, the peripheral circuit chip including a semiconductor substrate and an peripheral circuit and an interconnect layer sequentially formed on the semiconductor substrate, the peripheral circuit chip including an internal region and surrounding the internal region. Edge area;

[0166] Step S20 is formed in the edge region of the peripheral circuit chip, which is sequentially through the peripheral circuit and the interconnect layer revealed the surface of the semiconductor substrate;

[0167] Step S30, in the surface of the peripheral circuit and the interconnect layer...

Embodiment 2

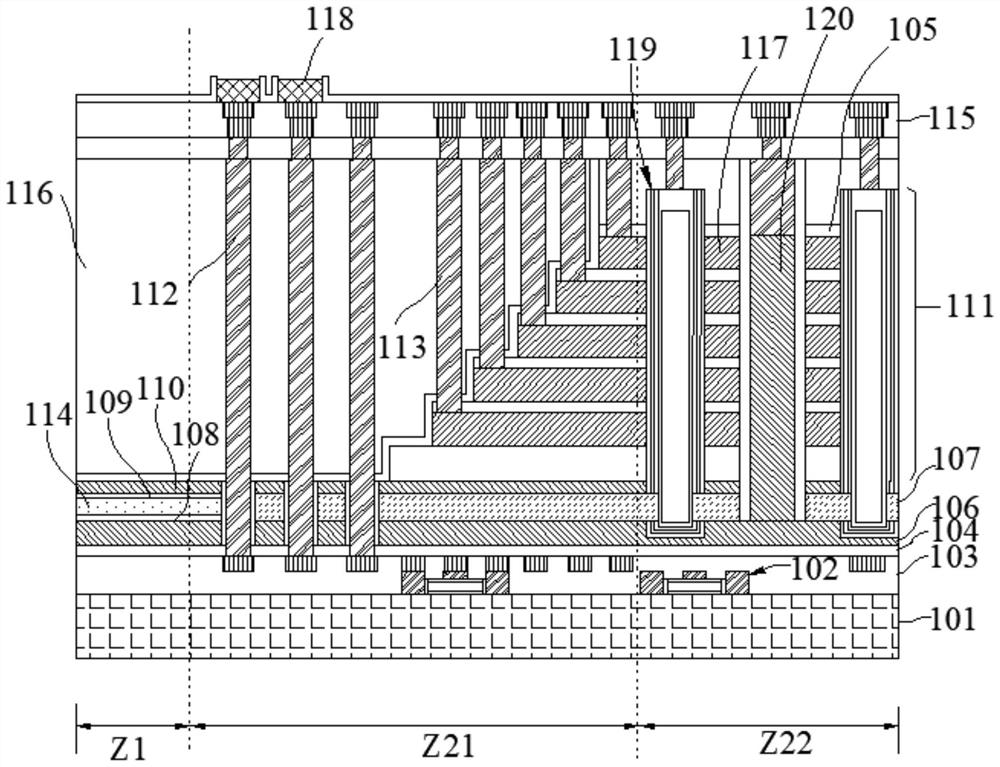

[0196] See Figure 16-19 The present invention also provides a three-dimensional memory prepared by the preparation method in the first embodiment, and the three-dimensional memory comprises at least a peripheral circuit chip, and a bottom semiconductor layer 206 formed on the peripheral circuit chip, an intermediate semiconductor layer, a top semiconductor layer. 210 and gate laminated structure 221.

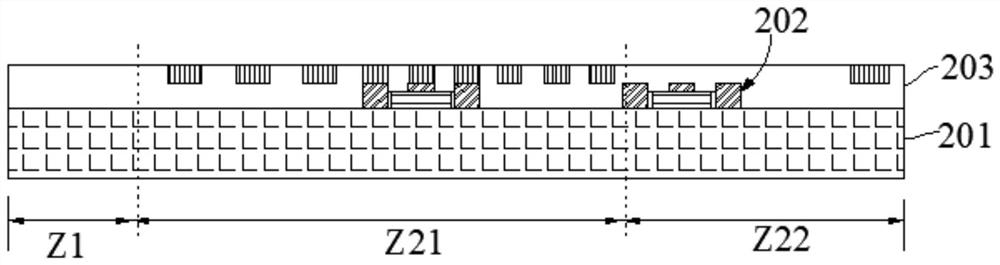

[0197] See Figure 16 In the present embodiment, the peripheral circuit chip includes a semiconductor substrate 201 and an peripheral circuit and an interconnect layer 203 in the semiconductor substrate 201, and the peripheral circuit and the interconnect layer 203 are further included. The peripheral circuit and peripheral interconnection layer formed on the semiconductor substrate 201; the peripheral circuit chip includes an internal region (including the core array region Z22 and step area Z21, which will be described later) and an edge region Z1 surrounding the internal region Z...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More