Electrostatic discharge protection clamping circuit of silicon-on-insulator circuit

An electrostatic discharge protection, silicon-on-insulator technology, applied in circuit devices, emergency protection circuit devices, emergency protection circuit devices for limiting overcurrent/overvoltage, etc., can solve problems such as no equipment, and improve electrostatic discharge protection. performance effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

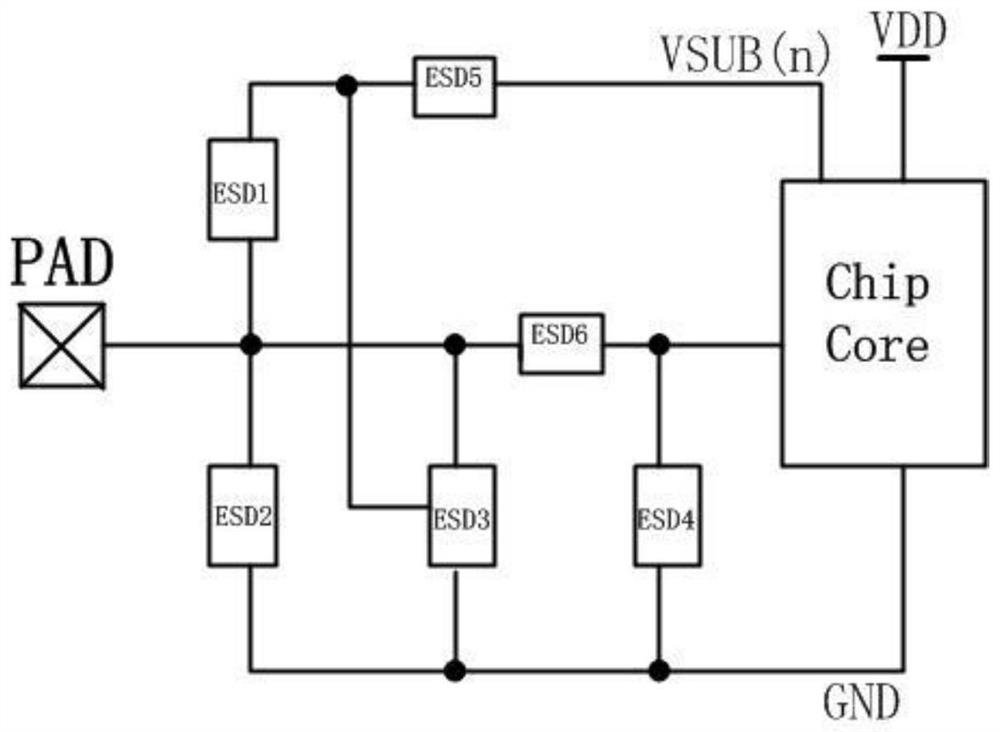

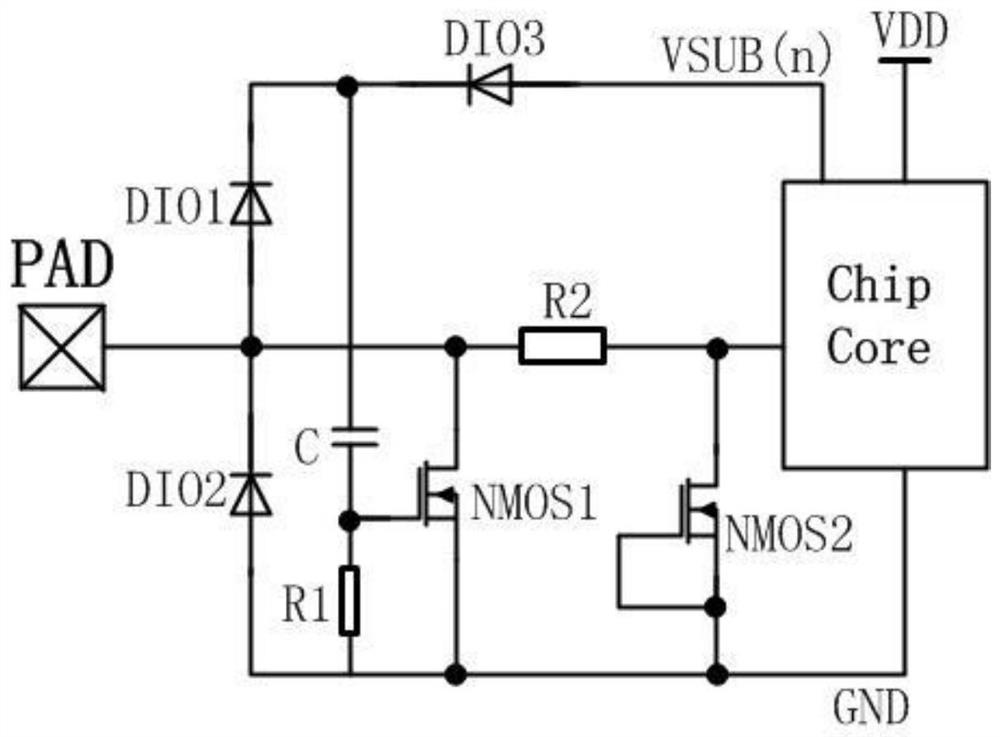

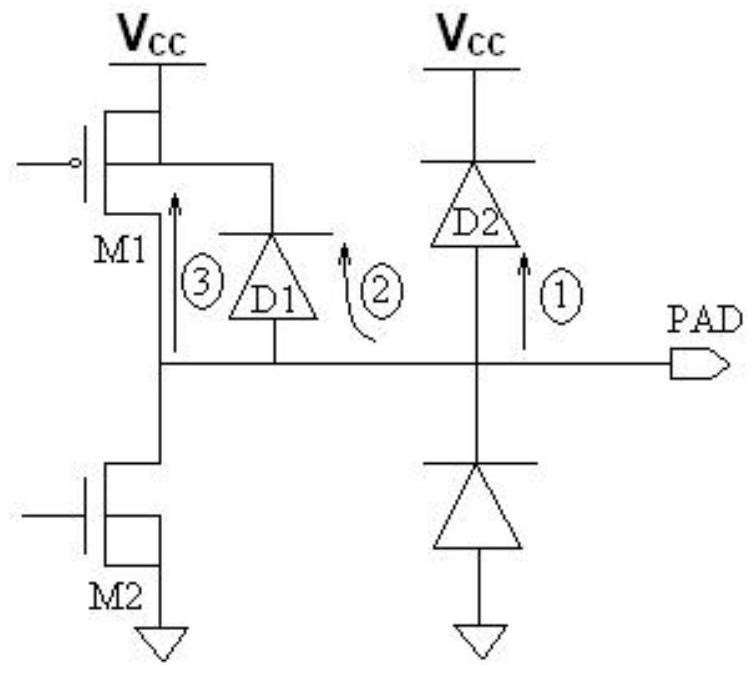

[0031] The embodiment of the present application provides a silicon-on-insulator circuit electrostatic discharge protection clamping circuit, aiming at the requirement that neither the control port nor the data port have a discharge path with the power supply, and the power supply port and the OUT port only allow two or more MOS transistors to be connected in series. , and there is no port circuit equipped with its own pseudo power supply in the circuit, so as to improve the ESD protection capability of such special-demand circuits.

[0032] In order to better understand the above technical solutions, the above technical solutions will be described in detail below in conjunction with the accompanying drawings and specific implementation methods. It should be understood that the embodiments of the present invention and the specific features in the embodiments are detailed descriptions of the technical solutions of the present application. , rather than limiting the technical sol...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com