An Aided Chip Design Method for Reducing Simulation Time

An auxiliary chip and design method technology, applied in computer-aided design, CAD circuit design, calculation, etc., can solve the problems of long simulation time, difficult schematic and layout adjustment, etc., to reduce simulation time, speed up, and reduce cost. effect of time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0025] The specific embodiments of the present invention will be described in further detail below in conjunction with the accompanying drawings, so as to make the technical solutions of the present invention easier to understand and grasp, so as to make a clearer definition of the protection scope of the present invention.

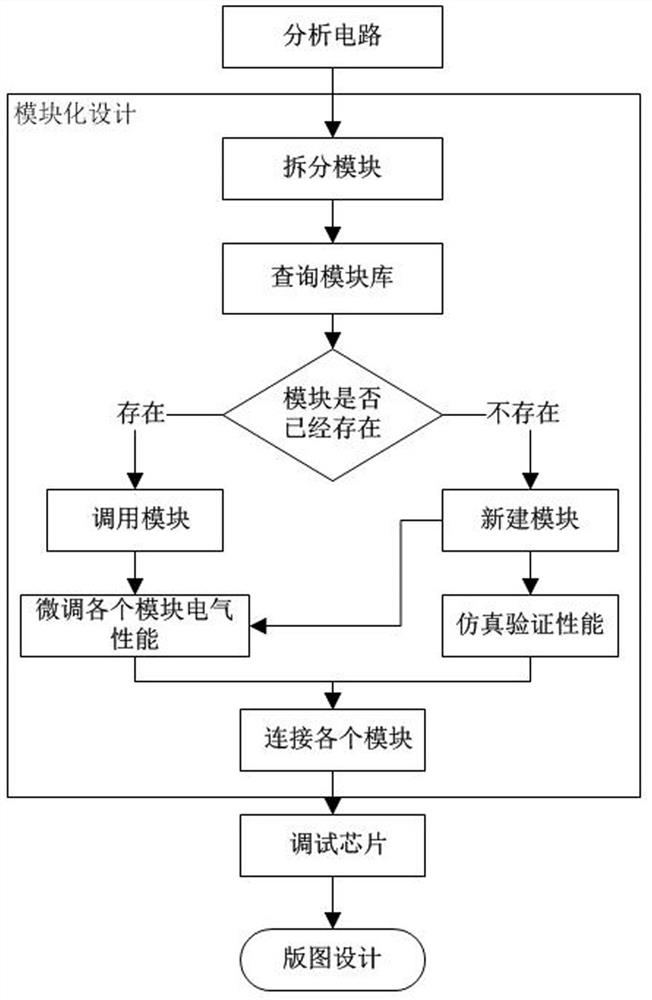

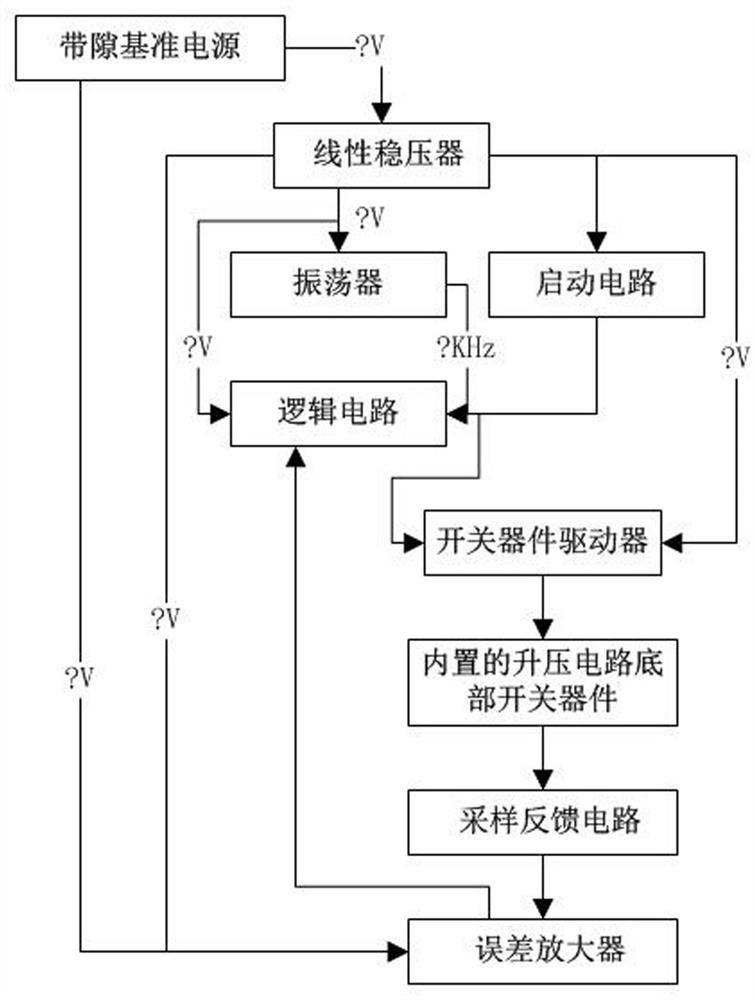

[0026] Aiming at the existing deficiencies, the designer of the present invention innovatively proposes an auxiliary chip design method based on the long-term experience in chip design such as analog integrated circuits, so as to optimize the chip design process. The main energy is to design some circuit modules with special functions required by the chip to speed up the chip design.

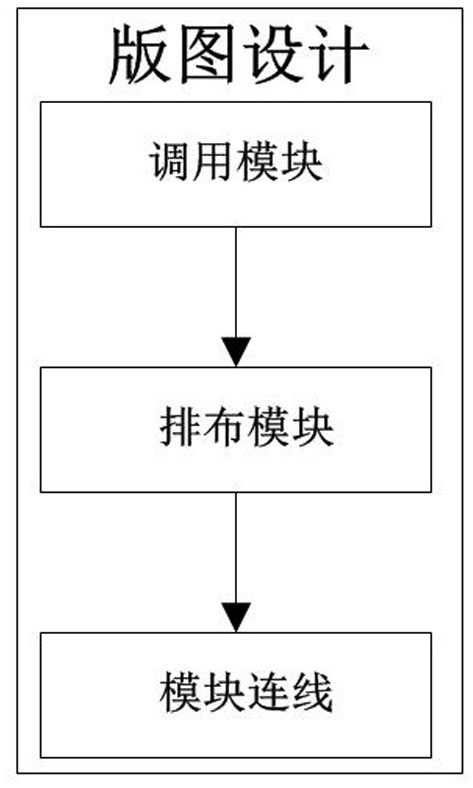

[0027] like figure 2 It can be seen from the schematic flow chart shown that the technical overview of the auxiliary chip design of the present invention mainly includes the following steps: S1. Establish a standard component library, classify various ready-made and verifi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More