Digital signal time delay method based on FPGA and high-precision time delay chip

A digital signal and delay chip technology, applied in the field of electronics, can solve the problems of not being able to reach large-scale physics, and the resolution is only at the nanosecond level, and achieve the effect of simple and reliable hardware circuits, improving delay resolution, and reducing errors

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

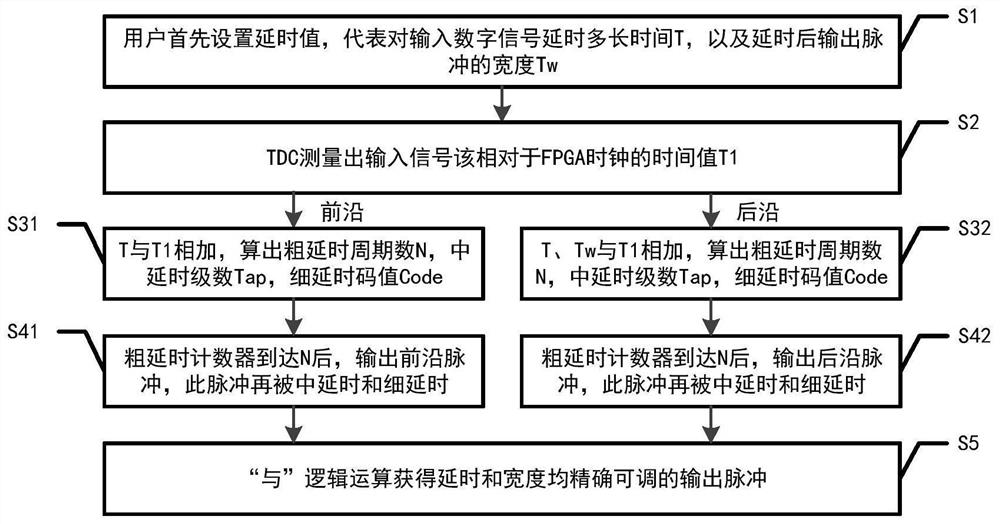

[0028] In this embodiment, a digital signal delay method of coarse delay+medium delay+fine delay is improved, such as image 3 The illustrated embodiment includes the following steps:

[0029] S1: The user sets the delay time T of the input signal and the width Tw of the output pulse after the delay according to the requirements; the parameters T and Tw satisfy the following relationship: Tn -1), T+Twn -1), wherein, n is the number of digits of the coarse counter, and Tclk is the coarse delay clock cycle, and it is not difficult to find out that the maximum value setting of T and Tw is related to the setting of the number of digits of the coarse counter by the above formula;

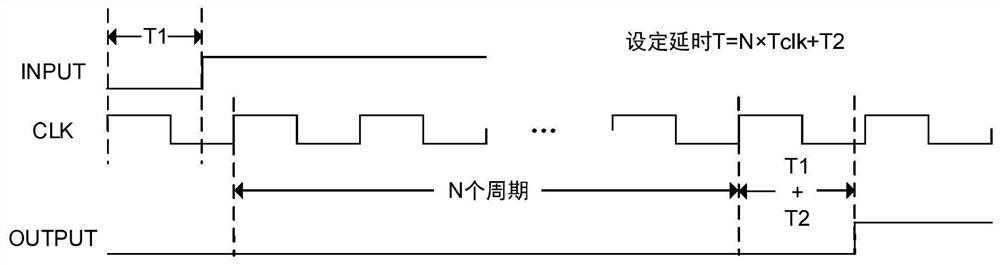

[0030] S2: Use TDC to measure the time value T1 of the input signal relative to the FPGA clock, such as Figure 4 As shown, the present embodiment obtains the time value of the input signal relative to the FPGA clock by the TDC built in the FPGA, in addition, it can also be measured with a dedicated TDC ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More