Method and device for controlling delay jitter at receiving end

A control method and technology of a control device, applied in the field of communication, can solve the problems of reducing the usage scenarios of 100G/400G DSP chips, the influence of delay jitter on optical communication quality cannot be ignored, system reliability and performance impact, etc., so as to reduce the delay Jitter, reduce impact, ensure the effect of stability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0036] In order to make the purpose, technical solution and advantages of the present invention more clear, the embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings. It should be noted that, in the case of no conflict, the embodiments in the present application and the features in the embodiments can be combined arbitrarily with each other.

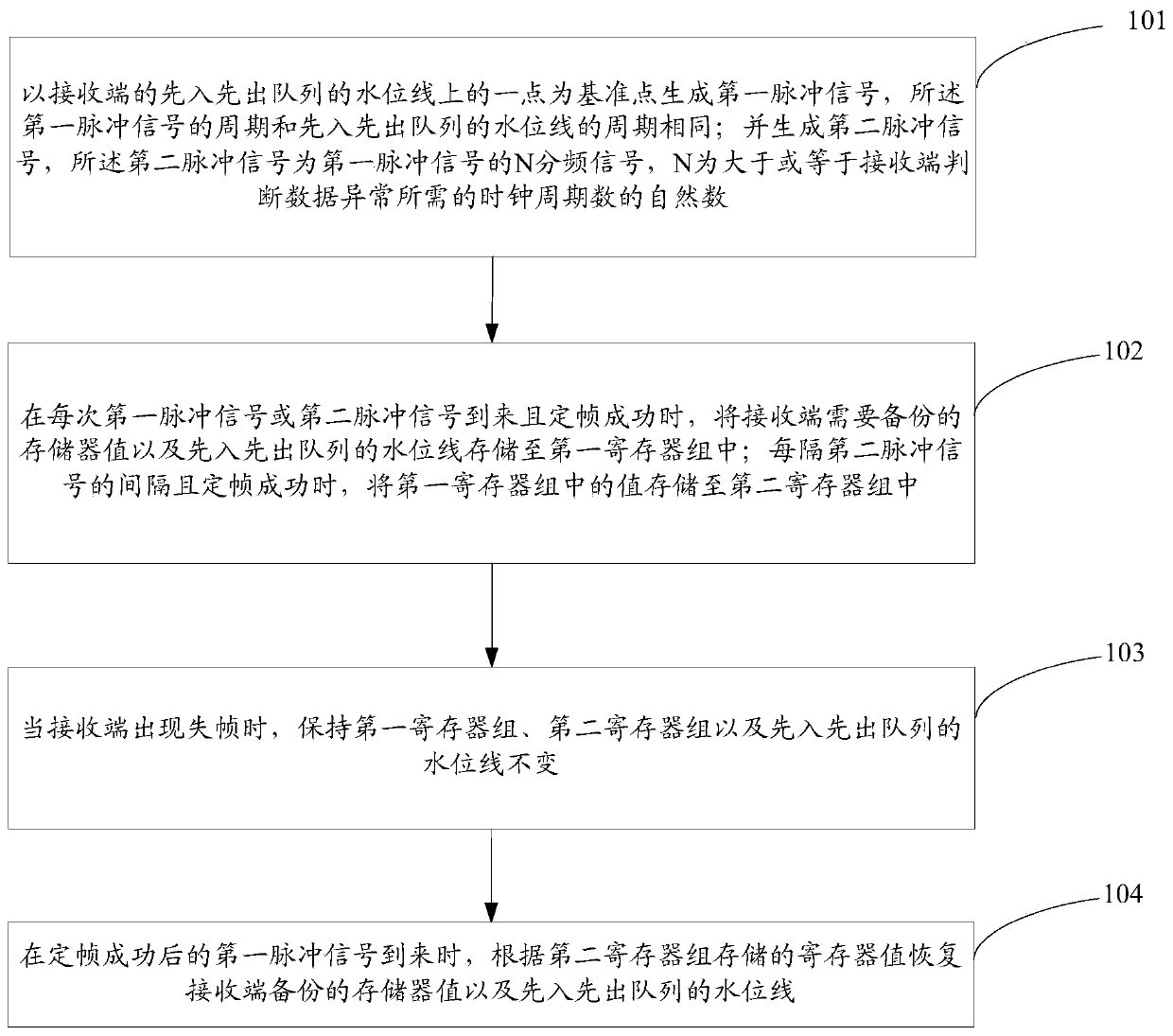

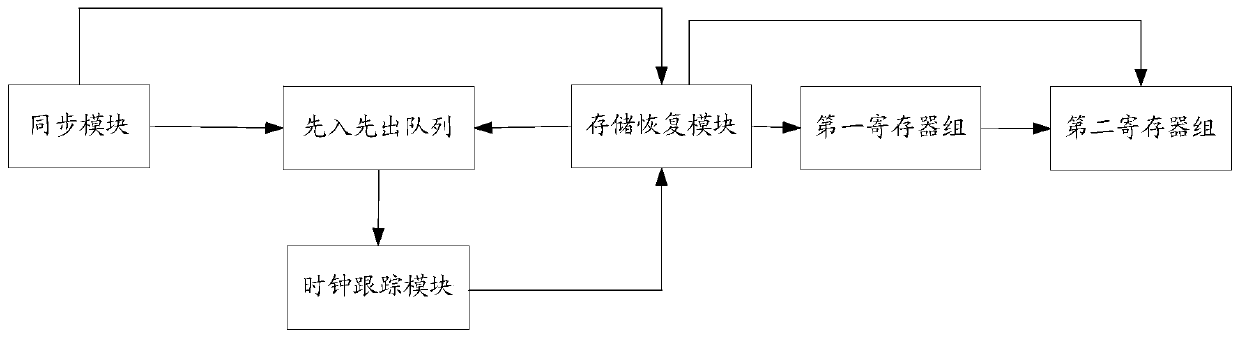

[0037] like figure 1 As shown, a method for controlling delay jitter at a receiving end according to the present invention includes the following steps:

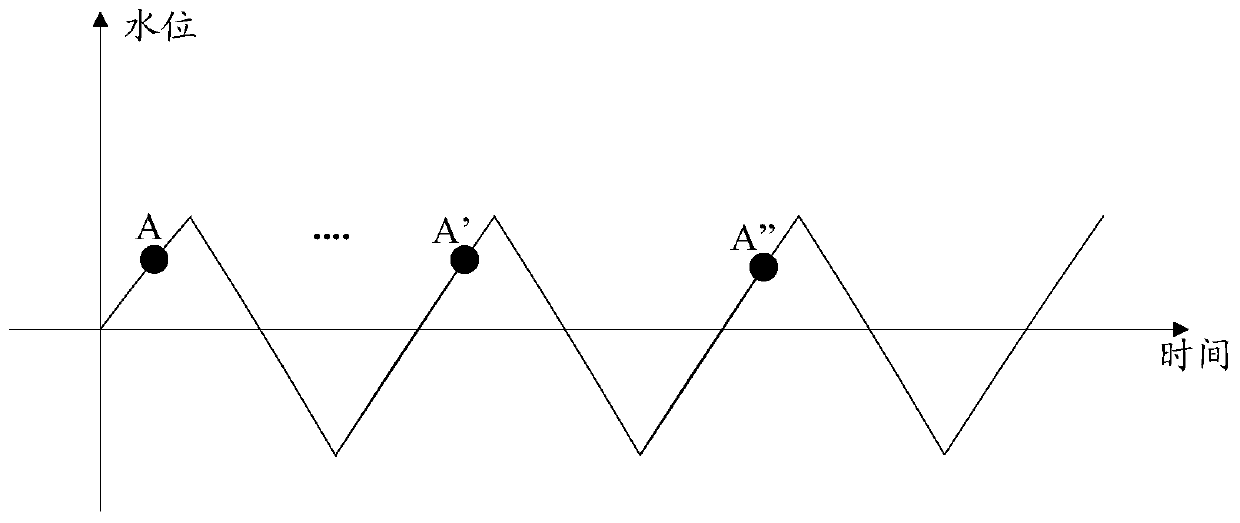

[0038] Step 101: Taking a point on the water level of the first-in-first-out queue at the receiving end as a reference point to generate a first pulse signal, the period of the first pulse signal is the same as the period of the water level of the first-in-first-out queue; generate a second pulse signal , the second pulse signal is an N frequency-divided signal of the first pulse signal, and N is a natural number greater t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More