FPGA receiving engine design based on SRIO

An engine, receiving state technology, applied in the field of signal processing, can solve problems such as complex design and inability to support real-time changes in the writing sequence

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0029] The technical solution of the present invention will be specifically described below in conjunction with the accompanying drawings.

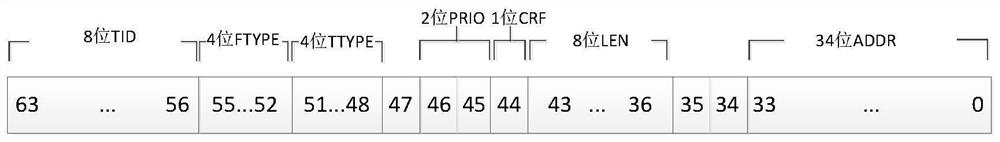

[0030] Because the SRIO transactions used by the CPU and DSP are generally NWRITE transactions and NWRITE_R transactions, the most commonly used is the transmission in units of double words, so only these two transactions are considered, and the transmission in units of words, halfwords, and bytes is not considered. .

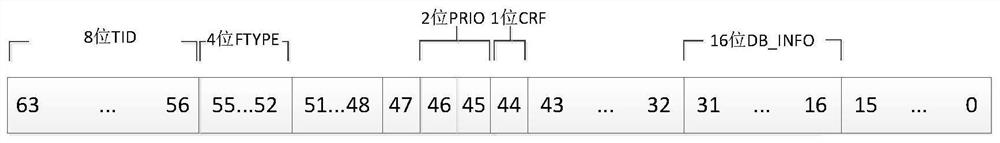

[0031] In order to achieve high-efficiency reception, the present invention designs a mechanism for using DOORBELL transactions to terminate write operations. After the external master device initiates a series of SWRITE transactions or NWRITE transactions to the FPGA, it needs to initiate a DOORBELL transaction to terminate the write operation. Between FPGA and FPGA, set a special doorbell word 0x0033 as the doorbell identification for FPGA to recognize the notification of write operation termination.

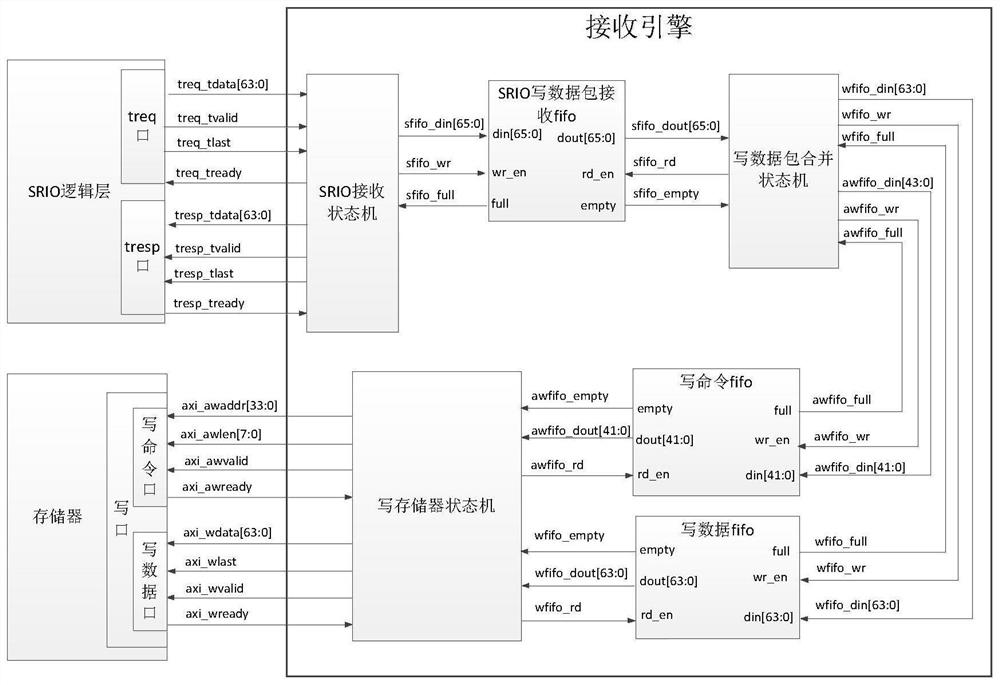

[0032] The archit...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More