Verification module with FPGA embedded in SoPC chip

A technology for verifying modules and chips, applied in the field of verification modules, can solve problems such as virtual verification difficulties, and achieve the effect of solving functional verification problems and verification difficulties

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0024] The technical solutions of the present invention will be further described in detail below in conjunction with the accompanying drawings and specific embodiments.

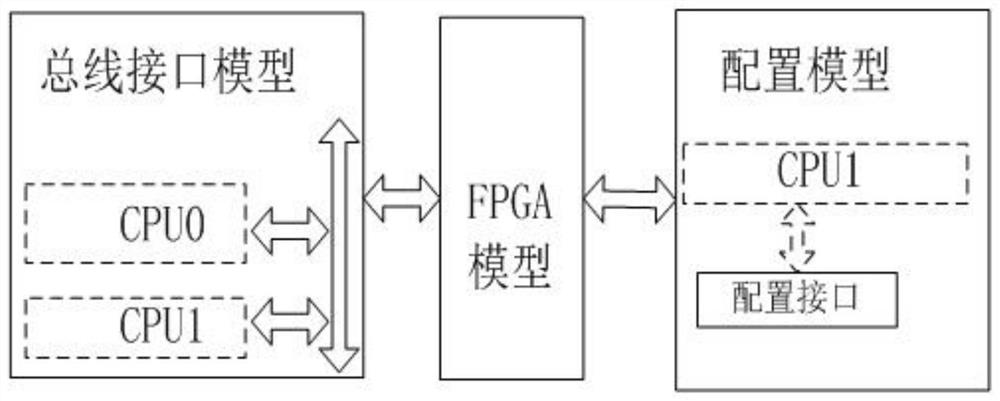

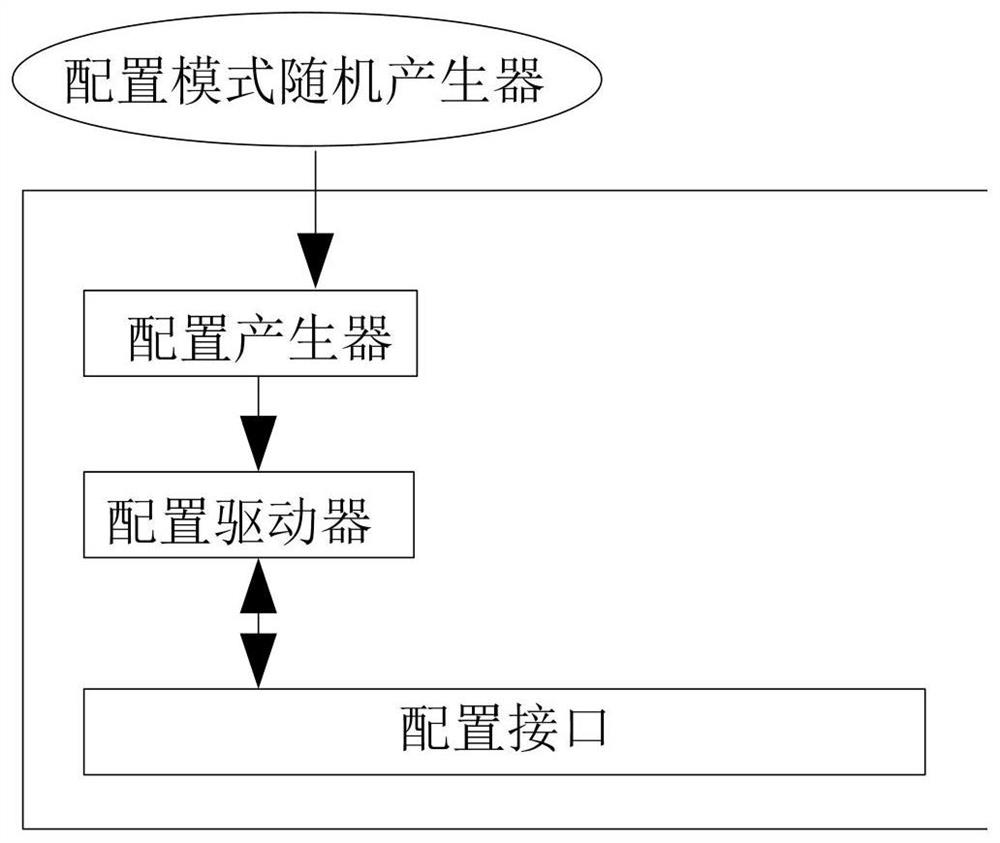

[0025] see figure 1 , the verification module of the specific embodiment of the present invention comprises bus interface model, configuration model, FPGA model, and bus interface model simulates dual-core (CPU0, CPU1) to complete the interconnection communication with FPGA model, and configuration model simulates CPU1 bus interface operation and completes FPGA model Injection of configuration flow data.

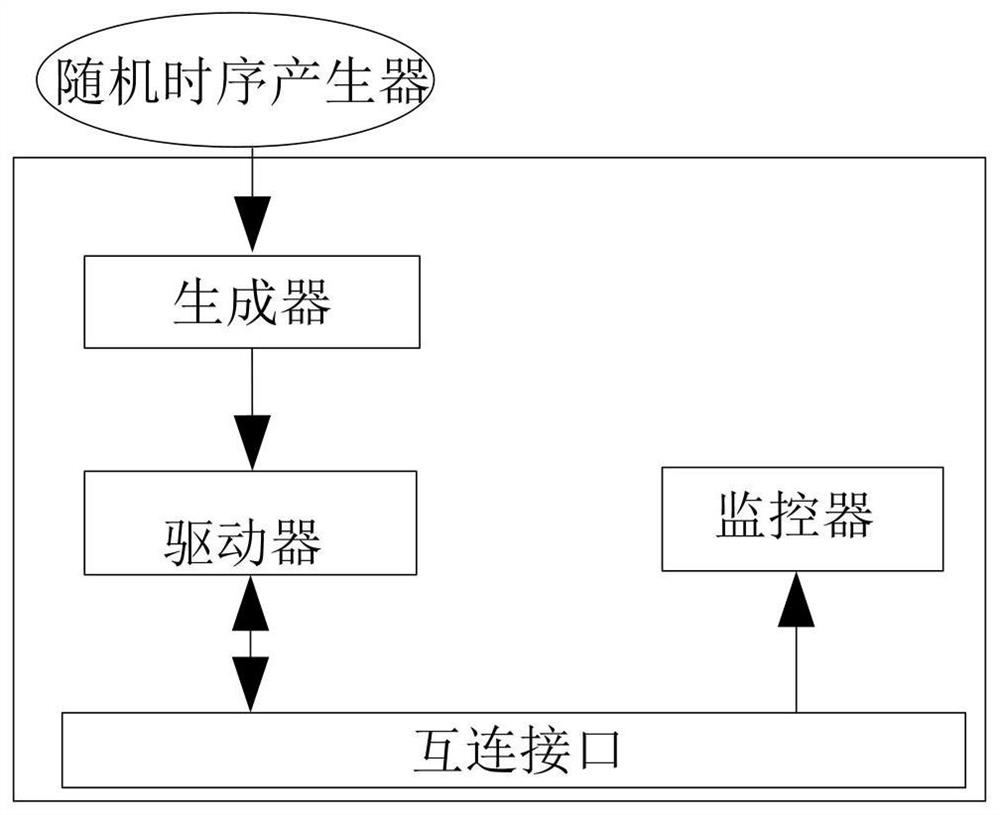

[0026] For the FPGA model integrated on the dual-core SoC, it is a third-party model, and its bus interface model interacting with the CPU is as follows: figure 1 As shown, the bus interface model simulation supports the access of CPU0 and CPU1, and the clock domains of CPU0 and CPU1 are often different. In order to ensure that the CPU bus access on the FPGA side is often used, the bus interface model oft...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More