Layout wiring method based on multiple masks

A wiring method and mask technology, which can be used in instrumentation, computing, electrical and digital data processing, etc., and can solve problems such as huge workload and cost.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

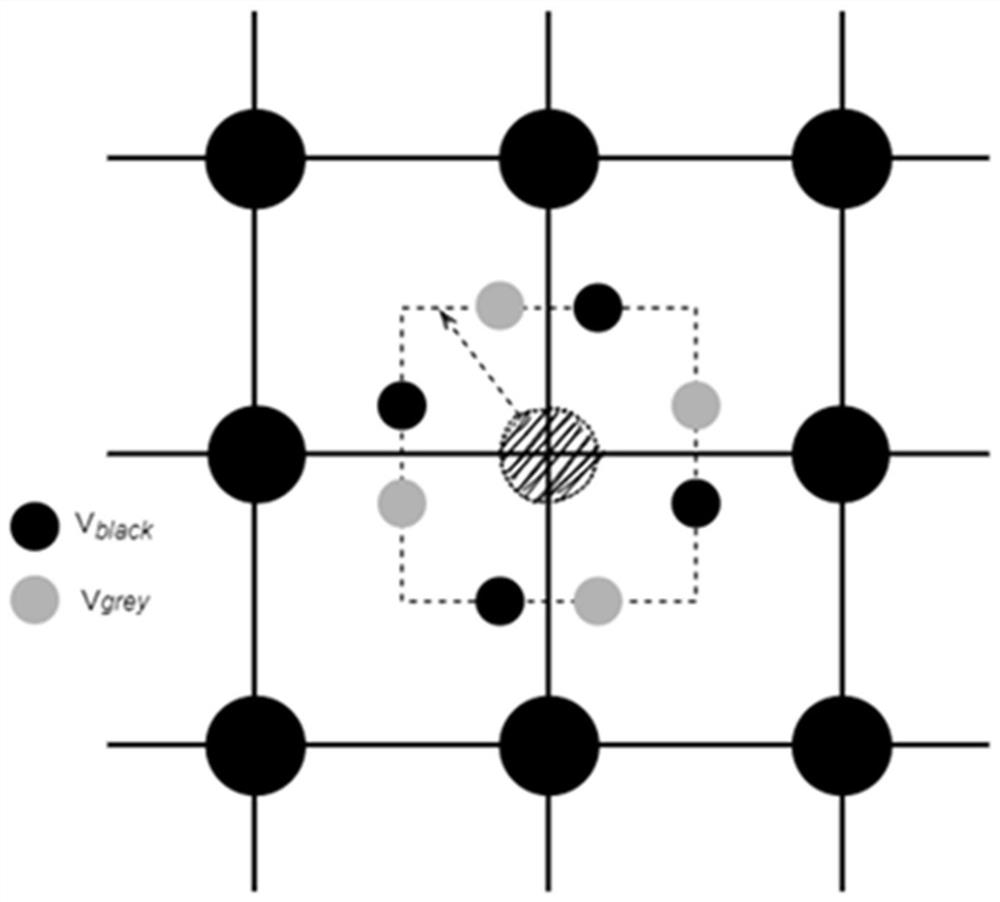

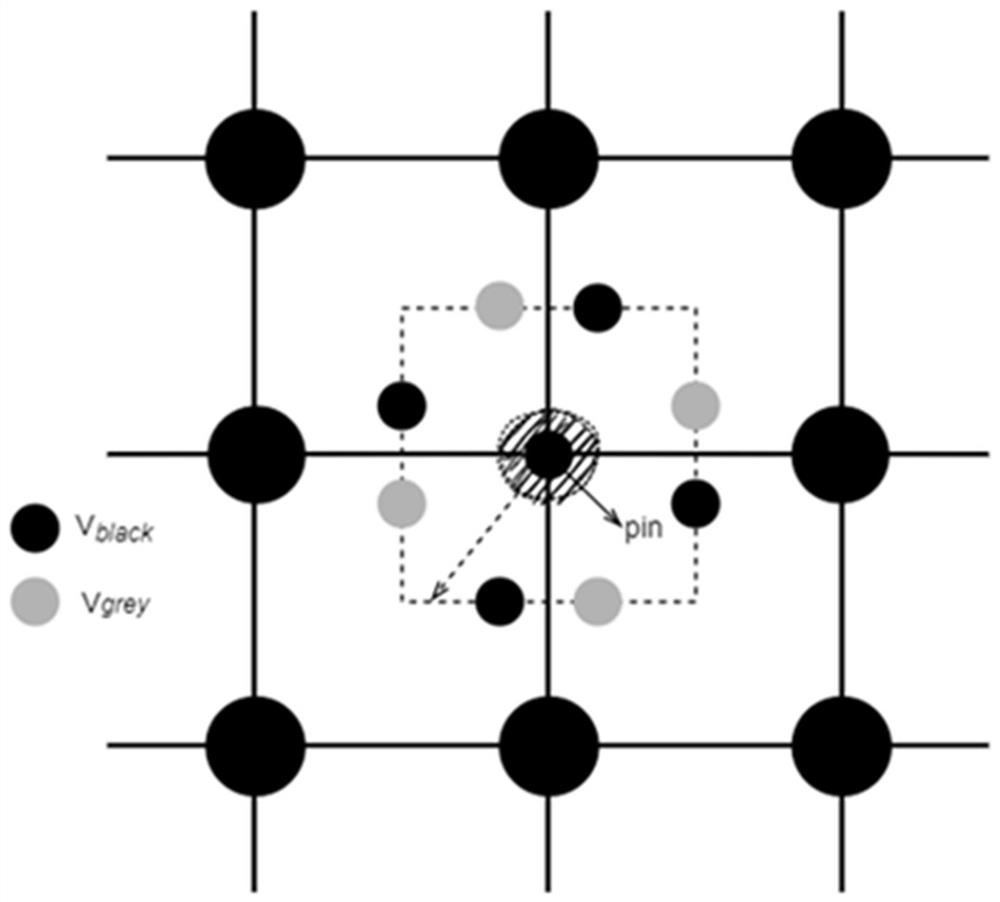

[0054]figure 1 In accordance with the multi-mask version of the multi-mask version of the multi-mask version, the reference will be referenced below.figure 1 The multi-mask-based layout method of the present invention is described in detail.

[0055]First, in step 101, the wiring resource is initialized.

[0056]In the embodiment of the present invention, the initialization of the wiring resources, including, process data (Design Rule), the basic data such as wiring layer, via holes, etc., the desired wiring mesh (NET) and wiring graphics read , The initialization of the wiring window, the initialization of the wiring mesh, the initialization of the wiring resources required during the algorithm expansion process.

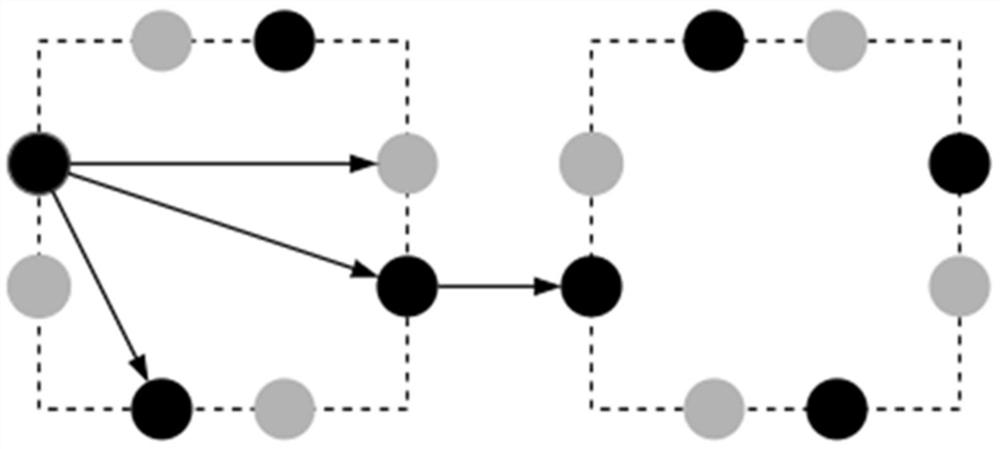

[0057]At step 102, the grid node is modeled to obtain the extended grid of the wiring grid.

[0058]In the embodiment of the present invention, the grid node is modeled, and a mesh node is abstracted to have a plurality of sub-nodes, which constitute a wiring grid of the wiring grid...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com