Chip packaging structure and preparation method of chip packaging structure

A chip packaging structure and chip packaging technology, applied in semiconductor/solid-state device manufacturing, electrical components, electric solid-state devices, etc., can solve problems such as poor heat dissipation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

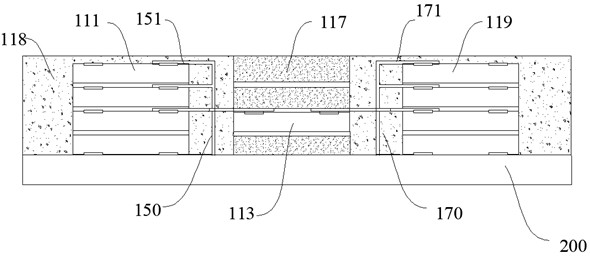

[0036] see figure 1 The embodiment of the present invention provides a chip packaging structure 100 with good heat dissipation effect. At the same time, through the stacked structure of the first memory chip 111, multiple chips can be stacked, which increases the number of stacks and ensures good heat dissipation effect.

[0037] The chip packaging structure 100 provided in this embodiment includes a dielectric layer 130 and a chip packaging module 110 disposed on the dielectric layer 130, wherein the chip packaging module 110 can be prepared in advance, and a dielectric layer is formed on the bottom of the chip packaging module 110 after the chip packaging module 110 is prepared. layer 130, or attach the chip packaging module 110 on the dielectric layer 130 prepared in advance.

[0038] The chip packaging module 110 includes a logic chip 113, a plurality of first memory chips 111, at least one first heat dissipation block 115, at least one second heat dissipation block 117 and ...

no. 2 example

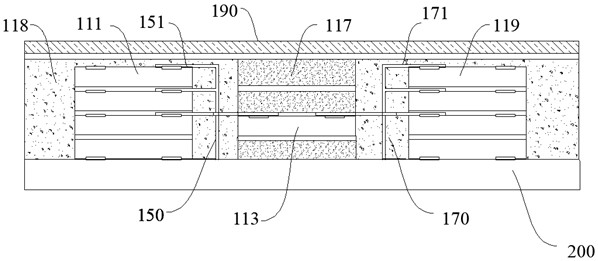

[0057] see figure 2 , this embodiment provides a chip packaging structure 100, the basic structure and principle and the technical effect produced are the same as those of the first embodiment, for a brief description, the parts not mentioned in this embodiment can refer to the first embodiment corresponding content.

[0058]In this embodiment, the chip packaging structure 100 includes a dielectric layer 130 and a chip packaging module 110 disposed on the dielectric layer 130, wherein the chip packaging module 110 can be prepared in advance, and formed on the bottom of the chip packaging module 110 after the chip packaging module 110 is prepared. dielectric layer 130 , or attach the chip packaging module 110 on the dielectric layer 130 prepared in advance. The chip packaging module 110 includes a plurality of first memory chips 111, a plurality of second memory chips 119, a logic chip 113, at least one first heat dissipation block 115, at least one second heat dissipation bl...

no. 3 example

[0062] This embodiment provides a method for manufacturing a chip packaging structure 100, which is used to prepare the chip packaging structure 100 provided in the first embodiment or the second embodiment.

[0063] The preparation method includes:

[0064] S1 : Prepare the chip packaging module 110 on the carrier 200 .

[0065] Specifically, use the carrier 200 to prepare the chip packaging module 110, mold the chip packaging module 110 on the carrier 200, remove the carrier 200 at last, form the dielectric layer 130 on the bottom side of the chip packaging module 110 after molding, or package the chip The module 110 is mounted on the pre-prepared dielectric layer 130 . The carrier 200 can be made of glass, silicon oxide, metal and other materials, and the chip packaging module 110 can be prepared by using the carrier 200, which can eliminate the warping problem during the manufacturing process and ensure the structural stability of the chip packaging module 110.

[0066] ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More