Model order reduction method and device of delay circuit system and medium

A delay circuit and model reduction technology, which is applied in the direction of electrical digital data processing, special data processing applications, instruments, etc., can solve the problems that the passivity and structure of the circuit system cannot be guaranteed, and achieve passivity and structure. , increase operability, improve the effect of stability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

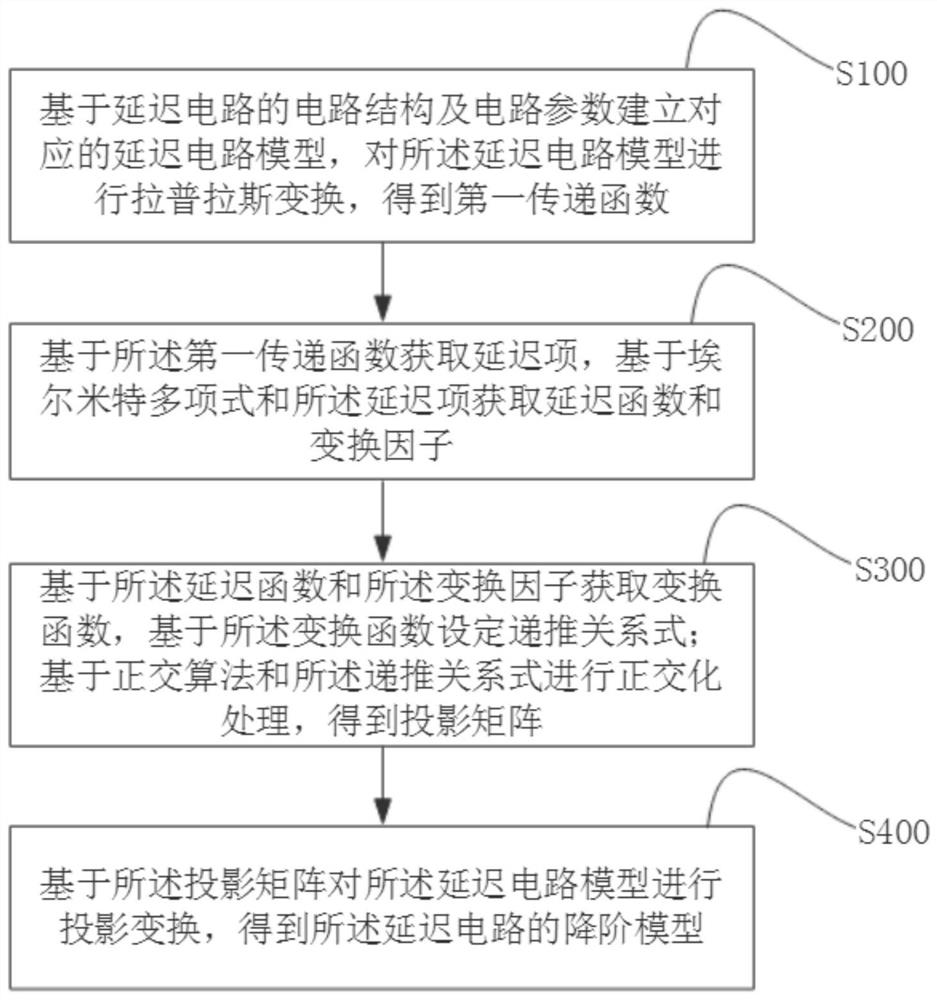

[0060] This embodiment provides a method for reducing the order of the model of the delay circuit system, such as Figure 1 to Figure 4 shown, including the following steps:

[0061] S100, performing mathematical modeling on the interconnection circuit system to obtain a corresponding delay circuit mathematical model (ie delay circuit model);

[0062] Step S100 specifically includes:

[0063] The transmission line part of the interconnection circuit system is modeled by telegraph equation to obtain the first circuit model; the lumped parameter part of the interconnection circuit system is modeled by the improved node voltage method to obtain the second circuit model; combining the first circuit model and The second circuit model is obtained by obtaining the mathematical model of the delay circuit;

[0064] The mathematical model of the delay circuit is:

[0065]

[0066] In the mathematical model of the delay circuit, there are the following state variables and coefficie...

Embodiment 2

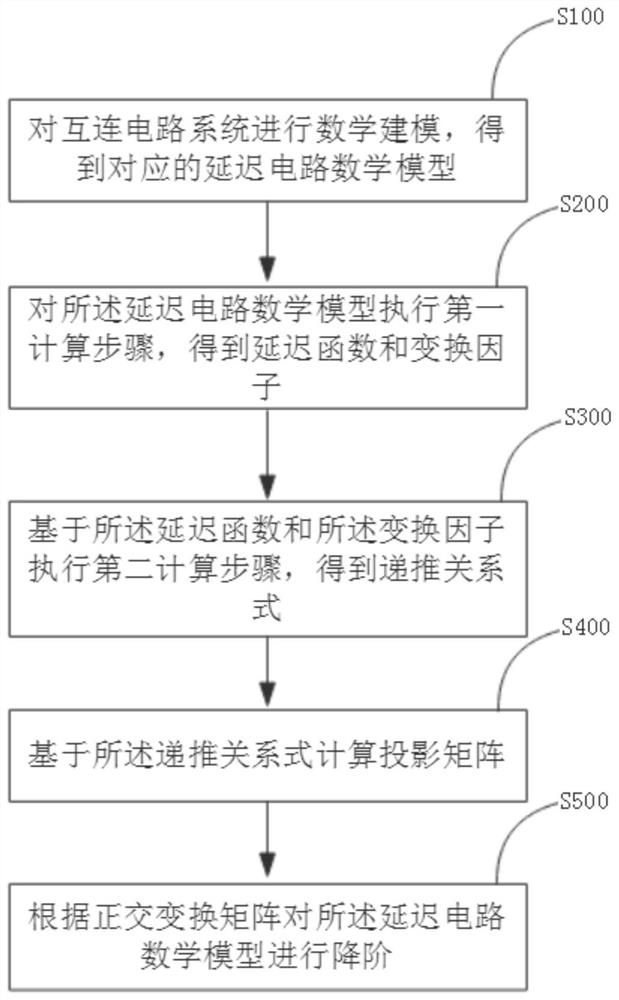

[0124] This embodiment provides a model reduction device for a delay circuit system, such as Figure 5 shown, including:

[0125] a first processor, a second processor and a third processor;

[0126] Before the operation of the device, the first circuit model is obtained by modeling the transmission line part of the interconnection circuit system in advance using the telegraph equation; the lumped parameter part of the interconnection circuit system is modeled by the improved node voltage method to obtain the second circuit model; combining the first circuit model and the second circuit model to obtain a delay circuit mathematical model;

[0127] The first processor is configured to perform a first calculation step on the mathematical model of the delay circuit to obtain a delay function and a transformation factor;

[0128] When the first processor executes the first calculation step, it specifically includes:

[0129] The first processor performs Laplace transform on the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More