Single input single output RCS interconnection circuit degradation method

A single-input, single-output, interconnected circuit technology, applied in the electronic field, can solve the problems that the system cannot be matched accurately, and the moment matching accuracy cannot be guaranteed.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0118] The present invention is further illustrated below by specific examples.

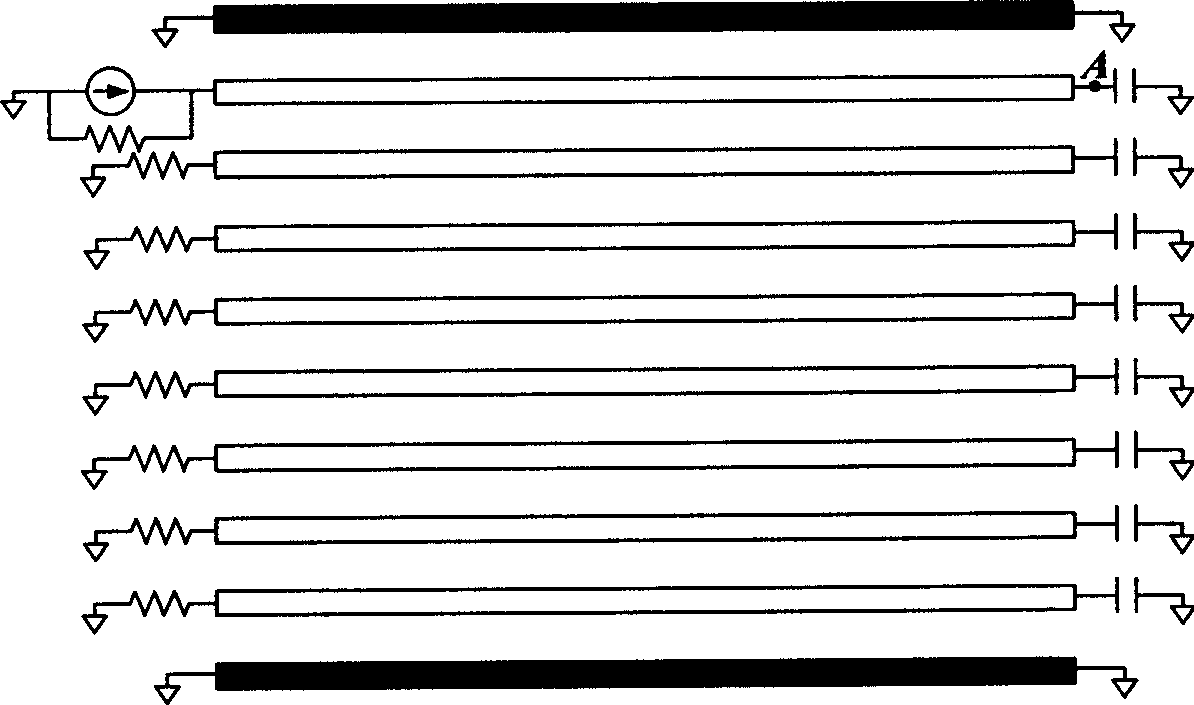

[0119] right figure 1 The 8-bit bus circuit shown (including two shielded wires) can be obtained by using the corresponding parameter extraction tool to obtain an equivalent RCS circuit. There are 490 unknown variables in the equivalent circuit, including 330 node voltages and 160 susceptance currents. We use the frequency response of node A as a measure of the accuracy of the order reduction.

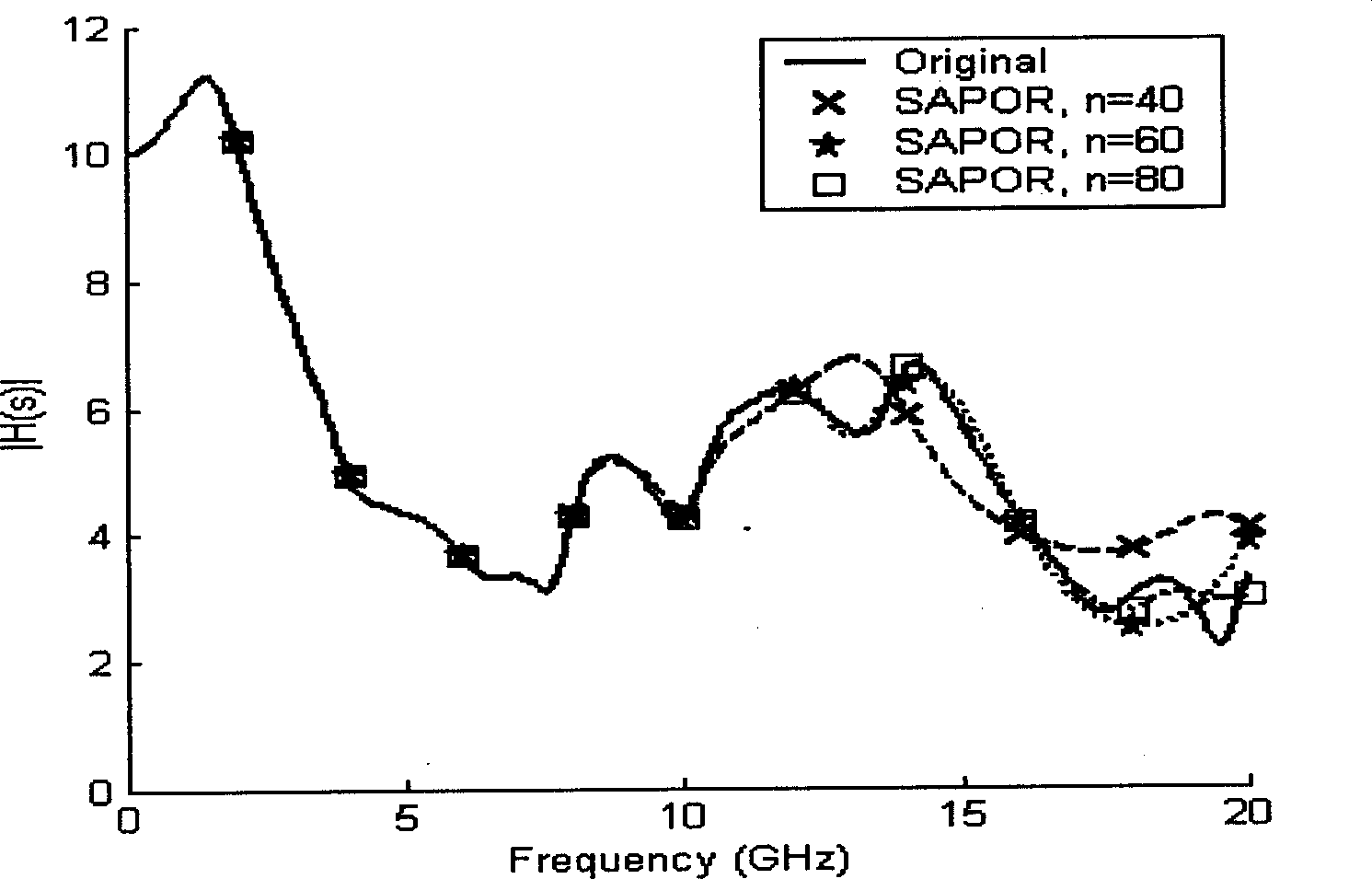

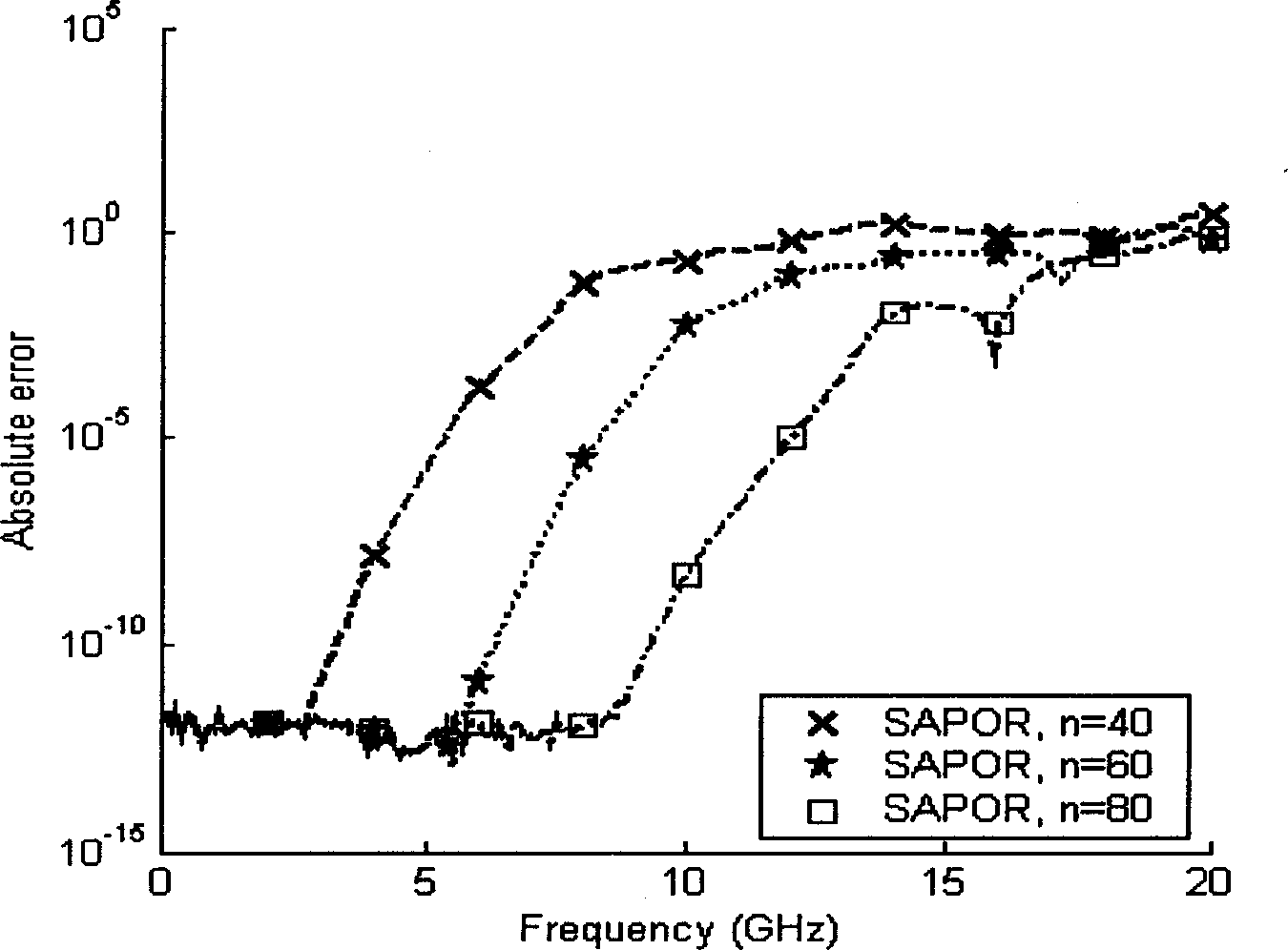

[0120] First, we use the algorithm of the present invention to reduce the order of the original circuit to different orders, namely 40, 60, and 80, and compare the accuracy of the order reduction. figure 2 It is a comparison chart of the frequency response curve of the original system and the frequency response curve of the reduced-order system of different orders obtained by SAPOR of the present invention. image 3 It is the error comparison of the frequency response of the reduced-order system with ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More