Order reducing method for non-linear circuit model based on direct progection and variation analysis

A nonlinear circuit and model technology, applied in the electronic field, can solve problems such as poor precision of the reduced-order system, non-linear system cannot be reduced, and a large number of input ports

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0100] The present invention is further illustrated below by specific examples.

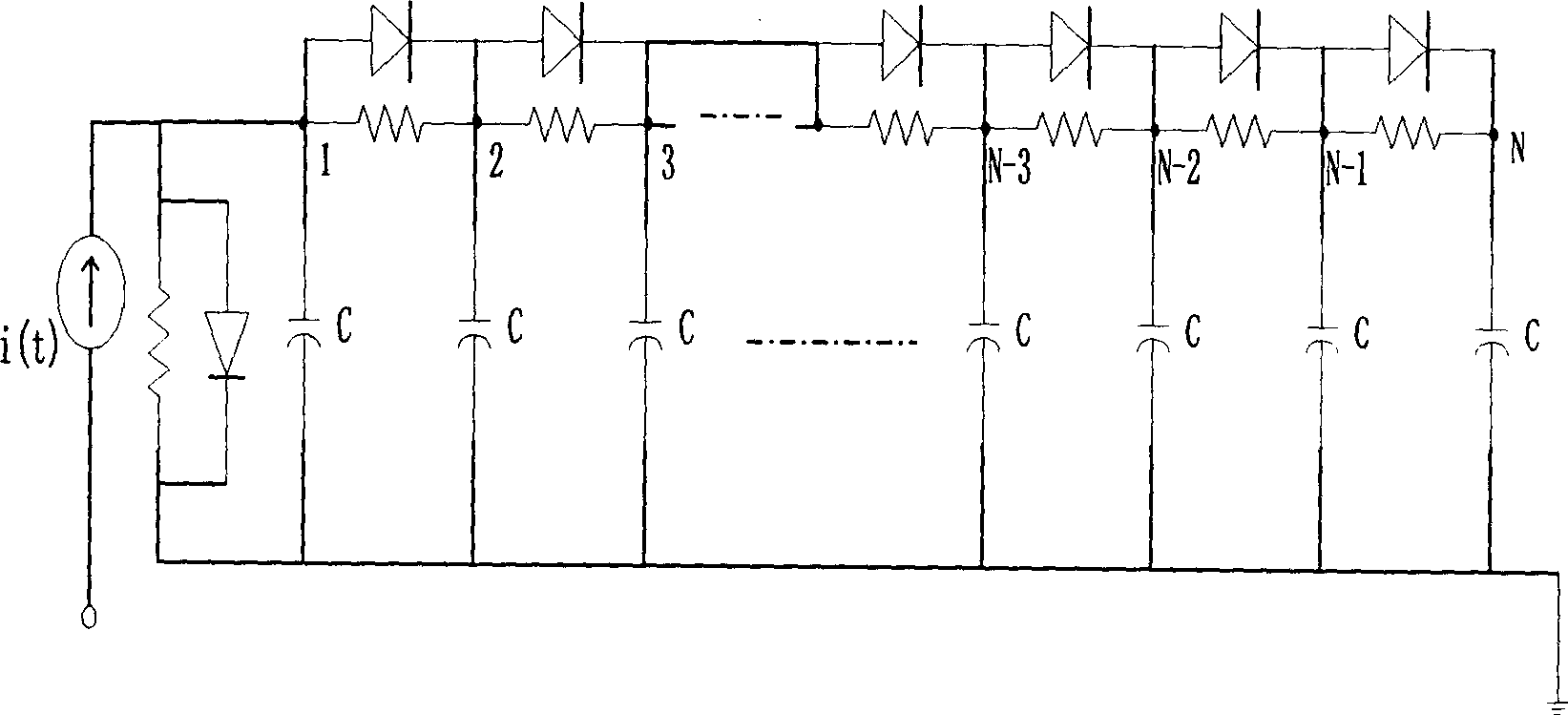

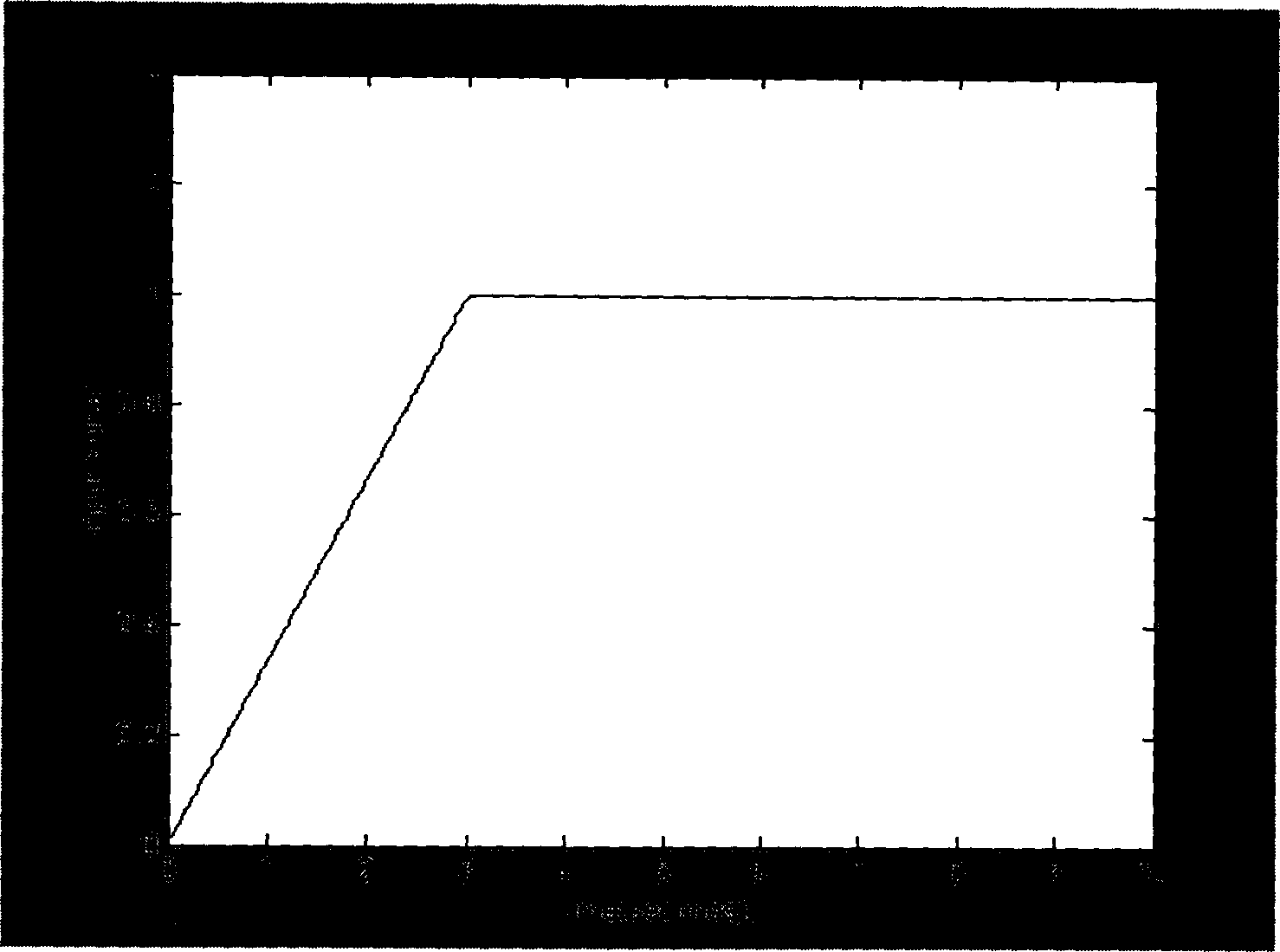

[0101] by figure 1 Take the circuit in as an example, the number of nodes in the circuit is N=100, and the order of the nonlinear circuit model (1) obtained from this circuit is n=100. The input signal is a step signal, see figure 2 .

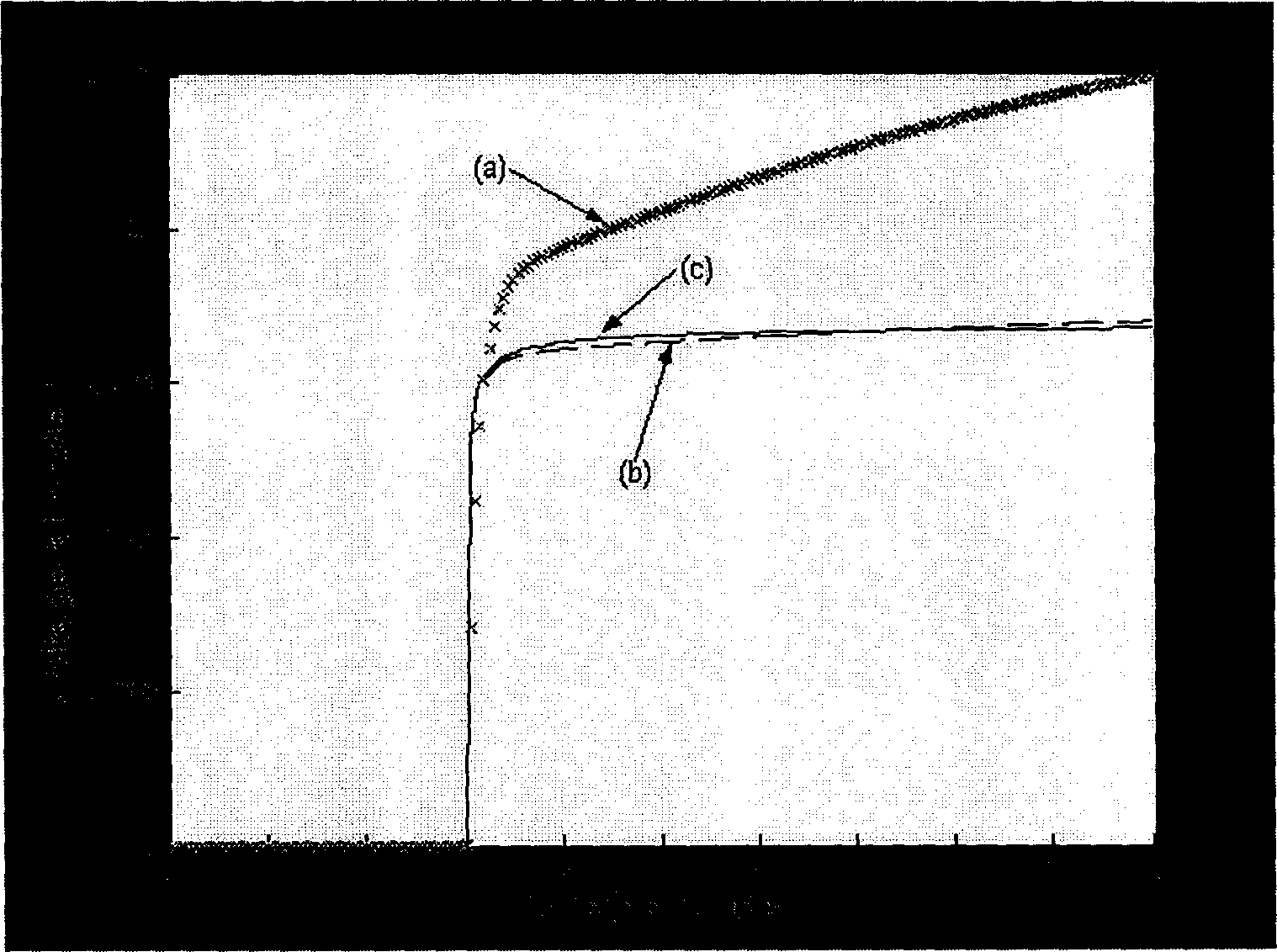

[0102] To reduce the order of this nonlinear system, first approximate (1) with the nonlinear approximation system (9), and then calculate the projection matrix. First calculate the matrix V 1 , where q 1 Take 7, that is, we orthogonalize the following 7 vectors

[0103] A -1 1 B,A -2 1 B,...A -7 1 B

[0104] Orthogonal technology is realized by using the existing algorithm Anorldi process. After orthogonalization we get V 1 .

[0105] for V 2 , first put A 2 After orthogonalizing the columns in Note that due to the usual A 2 There are many linearly related column vectors, so after orthogonalization, The number of column vec...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More