Method for forming semiconductor structure

A semiconductor and work function technology, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve problems such as transistor performance needs to be improved, achieve the effects of accurate thickness, simplified process, and improved production efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0028] As mentioned in the background art, the performance of existing transistors still needs to be improved. Now analyze and illustrate in conjunction with specific embodiment.

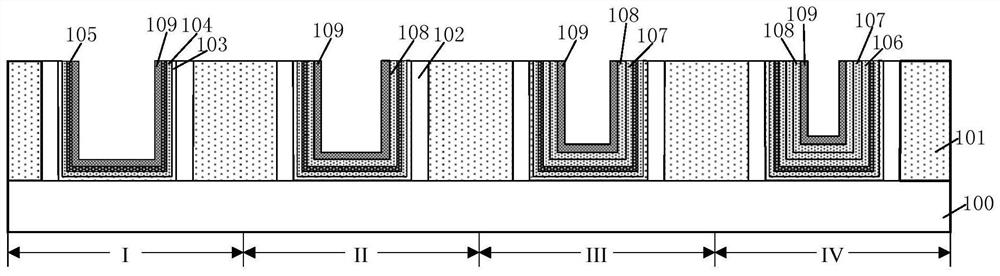

[0029] figure 1 It is a schematic cross-sectional structure diagram of a semiconductor structure in an embodiment.

[0030] Please refer to figure 1 , including: a substrate 100, which includes a first region I, a second region II, a third region III and a fourth region IV; a dielectric layer 101 on the substrate 100; a dielectric layer on the first region I The first gate opening (not shown) in 101, the second gate opening (not shown) in the upper dielectric layer 101 of the second region II, the third gate opening (not shown) in the upper dielectric layer 101 of the third region III electrode opening (not shown), the fourth gate opening (not shown) located in the dielectric layer 101 on the fourth region IV, the sidewall of the first gate opening, the sidewall of the second gate opening, the th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More