Clock recovery circuit and method, data processing chip and electronic equipment

A clock recovery and circuit technology, applied in the field of circuits, can solve the problems of low clock signal accuracy and achieve the effect of precise clock recovery

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0021] As mentioned in the background art above, the accuracy of the clock signal recovered by the existing clock recovery circuit is low.

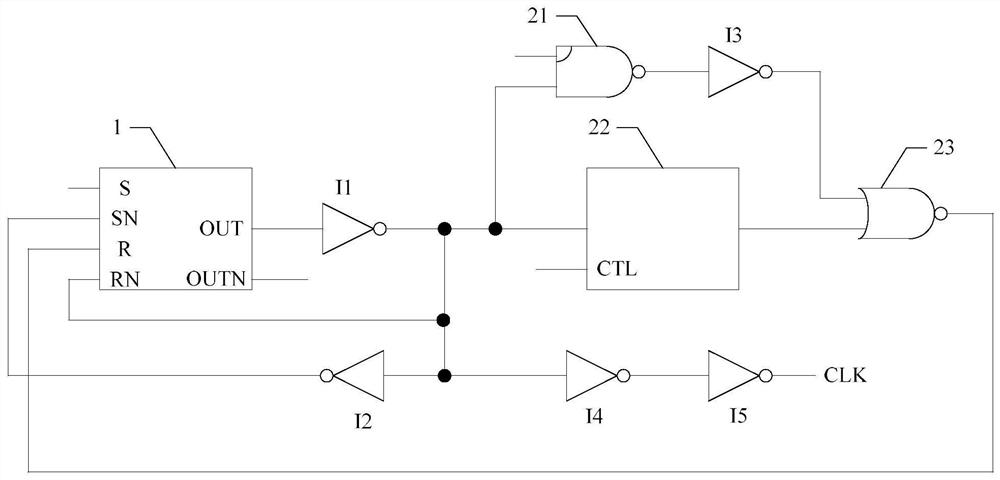

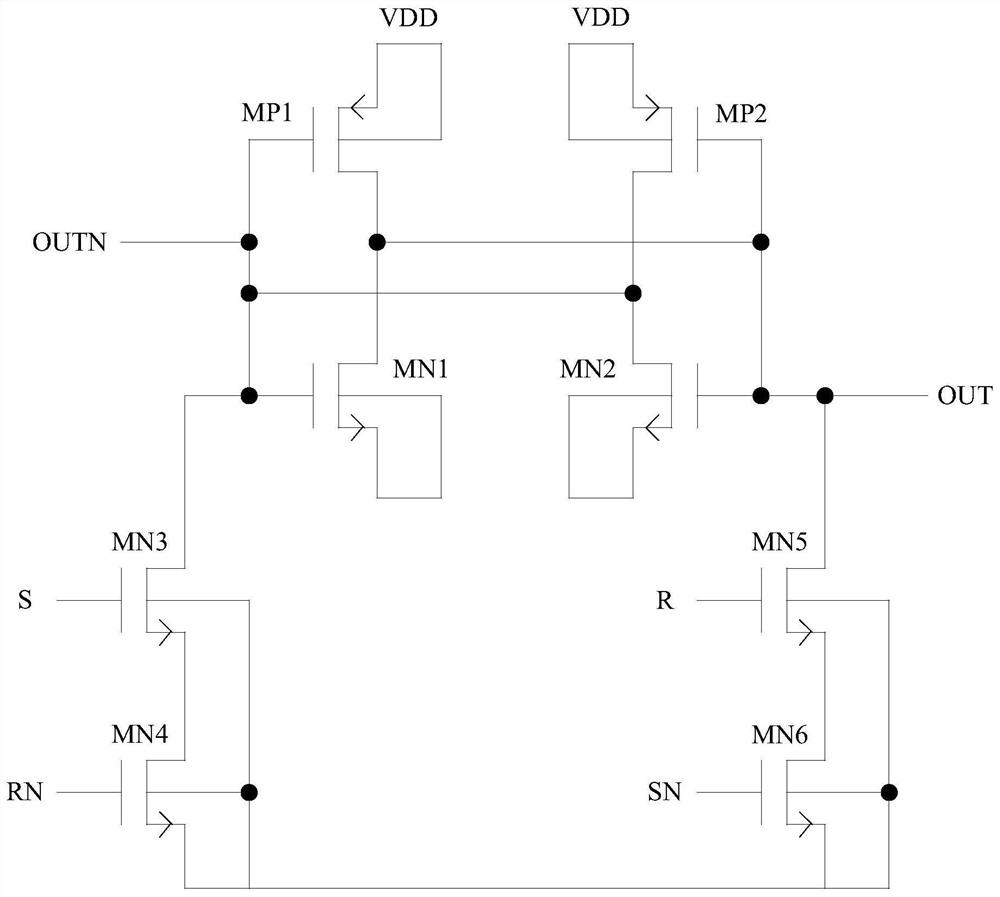

[0022] In the embodiment of the present invention, the clock recovery circuit includes a latch module, a monostable module, and an inverting logic unit, through the latch module to latch multiple groups of pulse signals input from its first set terminal, when any group of pulse signals from When it transitions from low level to high level, its rising edge is latched. The first output terminal of the inversion logic unit inverts the output signal of the first output terminal of the latch module, and the second output terminal of the inversion logic unit inverts the output signal of the first output terminal thereof. The first input terminal of the monostable module inputs the output signal of the first output terminal of the latch module through inversion, and a stable delay is obtained through the delay path of the monostable module, ther...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More