Chip mounting process capable for reducing stress

It is a technology of chip mounting and surface mounting technology, which is applied in the manufacture of electrical components, electrical solid devices, semiconductor/solid devices, etc. It can solve problems such as broken interconnection solder balls, increased difficulty of chip consistency, and inability to realize folding or bending. , to achieve the effect of reducing stress and solving terminal reliability problems

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0040] Embodiment 1, in this embodiment, a stress-reducing chip mounting process includes the following steps:

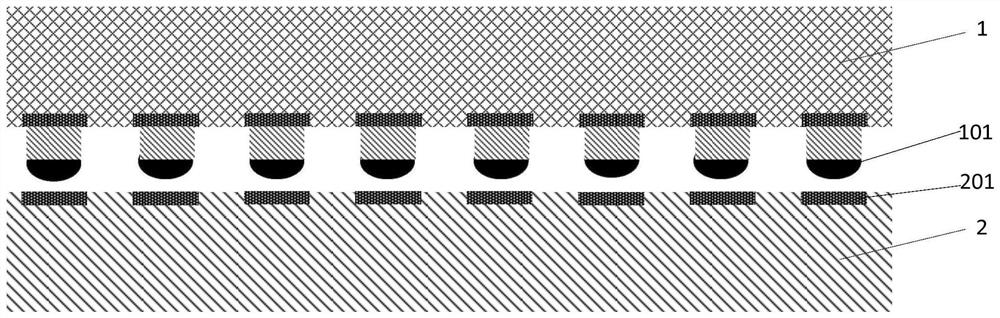

[0041] Step S1, the chip 1 is mounted on the surface of the substrate 2 through the surface mount process, and the solder balls 101 on the front of the chip 1 are connected to the pads 201 on the substrate 2 by reflow soldering; the chip 1 is preset with an array of small chip unit;

[0042] Specifically, such as Figure 1a As shown, pads 201 and wiring are distributed on the surface of the substrate 2, solder balls 101 for interconnection have been prepared on the front of the chip 1, and the chip 1 and the substrate 2 are welded by reflow soldering; the material of the substrate 2 is a PCB board, or a ceramic substrate , plastic substrates, etc.;

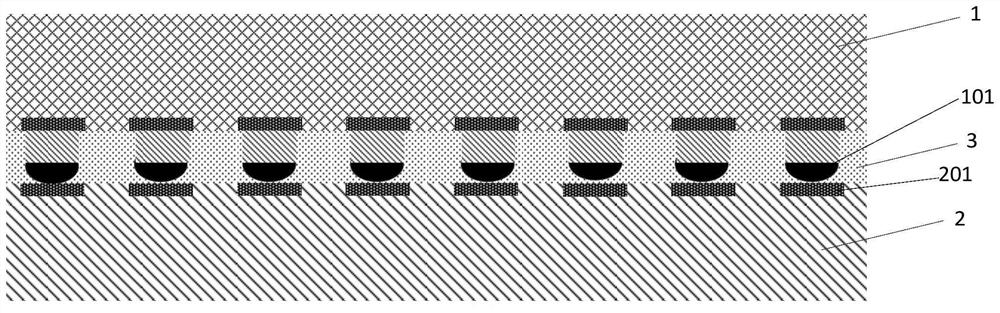

[0043] Step S2, filling the underfill glue 3 at the bottom of the chip 1, absorbing the liquid underfill glue 3 into the gap between the chip 1 and the substrate 2 through the surface tension of the chip 1 and the subs...

Embodiment 2

[0048] Embodiment 2, in this embodiment, a stress-reducing chip mounting process includes the following steps:

[0049] Step S1, the chip 1 is mounted on the surface of the substrate 2 through the surface mount process, and the solder balls 101 on the front of the chip 1 are connected to the pads 201 on the substrate 2 by reflow soldering; the chip 1 is preset with an array of small chip unit;

[0050] Specifically, such as Figure 1a As shown, it is the same as step S1 in Embodiment 1;

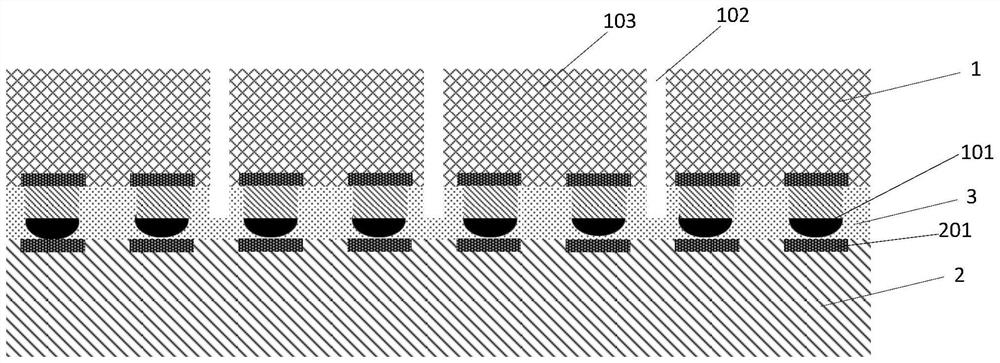

[0051] Step S2, splitting from the back of the chip 1 to form grooves 102, and splitting the chip 1 into array-type small chip units 103; interconnection;

[0052] Specifically, the chip 1 can be divided into an array of small chip units 103 by photolithography and dry etching; or, the chip 1 can be divided into an array of small chip units 103 by blade cutting or laser cutting; the formed The trench 102 can be as Figure 2a or Figure 2b shown;

[0053] Step S3, filling the underfill glu...

Embodiment 3

[0055] Embodiment 3, in this embodiment, a stress-reducing chip mounting process includes the following steps:

[0056] Step S1, making a groove 102 on the front of the chip 1, the groove 102 does not penetrate the material of the chip 1; the chip 1 is preset with an array of small chip units;

[0057] Specifically, the groove 102 can be made by dry etching, blade cutting or laser cutting;

[0058] In step S2, the chip 1 is mounted on the surface of the substrate 2 through a surface mount process, and the solder balls 101 on the front of the chip 1 are connected to the pads 201 on the substrate 2 by reflow soldering;

[0059] The material of the substrate 2 is a PCB board, and can also be a ceramic substrate, a plastic substrate, etc.;

[0060] Step S3, grinding or dry etching the back of the chip 1, so that the prefabricated groove 102 penetrates through the material of the remaining thickness of the chip 1, thereby dividing the chip 1 into an array of small chip units 103; ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More