Embedded synthetic network substrate lamination based on multiple lamination and design method

A technology of multiple lamination and design methods, applied in the direction of multi-layer circuit manufacturing, printed circuits, electrical components, etc., can solve the problem of difficult to meet the needs of high-density integrated applications, and achieve flexible and convenient application, convenient wiring, and RF signal isolation. good performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

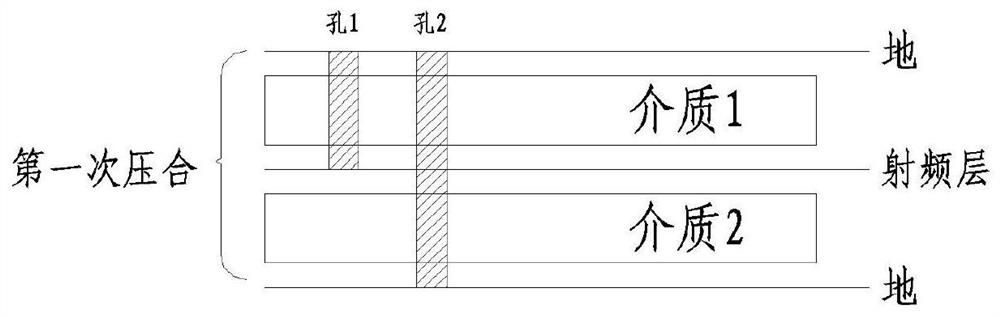

[0035] This embodiment provides a multi-lamination-based design method for embedded synthetic network substrate stacking, including: laminating one radio frequency layer and two ground property layers into a basic unit, wherein , the radio frequency layer is located in the middle of the two ground property layers;

[0036] A single basic unit is stacked as an array composite network integrated substrate or multiple basic units are laminated multiple times, and at the same time, a radio frequency isolation hole that conducts the entire basic unit is separately designed in the basic unit.

[0037] Specifically, in this embodiment, as figure 1 As shown, a single basic unit is used as an array composite network substrate stack, and the radio frequency layer in the basic unit is placed between the two ground property layers in the way of embedded resistance film processing, so as to realize the corresponding coupling and board-level embedding of the composite network. The size of ...

Embodiment 2

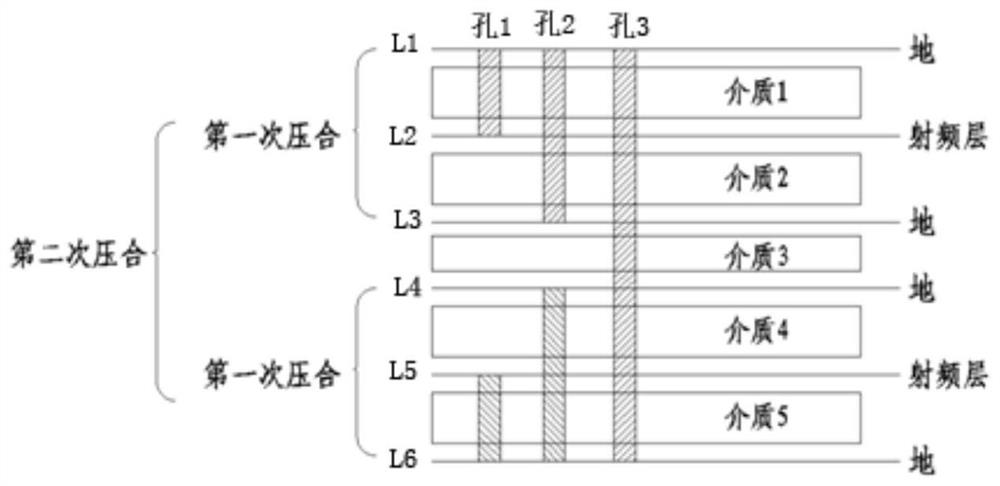

[0042] This embodiment is basically the same as Embodiment 1, the difference is that in this embodiment, the array synthesis network integrated substrate stack is composed of two basic units, when the array synthesis network integrated substrate stack is composed of multiple basic units When the unit is formed, a plurality of basic units are provided with communicating ground holes or installation holes.

[0043] Such as figure 2 As shown, the two basic unit structures are laminated twice to form an array composite network integrated substrate stack, in which L2 and L5 are two radio frequency layers, and the upper and lower layers (L1, L3, L4, L6) are ground Attribute layer, each layer has an independent radio frequency isolation hole (hole 2), which is used for signal isolation and electromagnetic shielding around the grounding and radio frequency transmission lines. Hole 1 is the gap between the L2, L5 radio frequency layer and the respective surface layers L1, L6 Signal t...

Embodiment 3

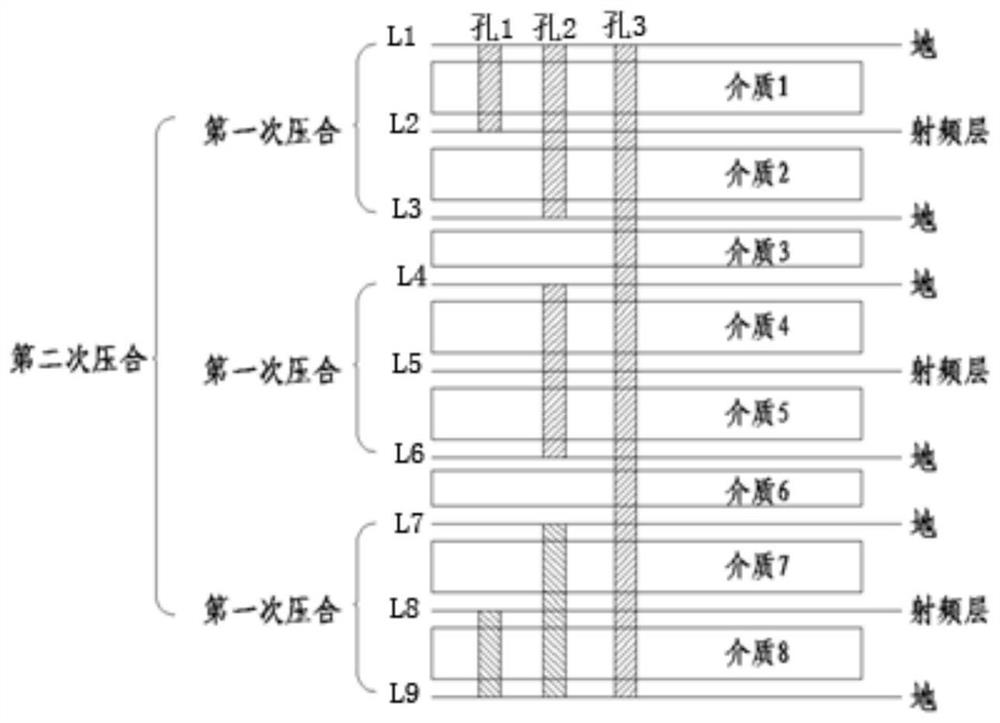

[0048] This embodiment is basically the same as Embodiment 1 and Embodiment 2, the difference is that in this embodiment, the array synthesis network integrated substrate stack is composed of three basic units, such as image 3 As shown, the laminated structure formed by secondary pressing of three basic unit structures, in which L2, L5, and L8 are three radio frequency layers, each of which has two upper and lower layers (L1, L3, L4, L6, L7, L9) They are all ground layers, and each layer has an independent radio frequency shielding hole (hole 2), which is used for signal isolation and electromagnetic shielding around the grounding and radio frequency transmission lines. Hole 1 is for the L2, L8 radio frequency transmission layer and the respective surface layers L1, The signal transmission hole between L9, hole 3 can be used as a ground hole, installation hole, etc. Arbitrary layer interconnection of radio frequency signals and addition of low frequency layers can be designed...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More