Field-programmable gate array device and memory power supply control method

A technology of power control and memory, applied in the fields of instruments, climate sustainability, electrical digital data processing, etc., can solve the problems of FPGA chip power consumption waste, heat dissipation difficulty, high temperature, etc., to alleviate the high working temperature and reduce power consumption Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0038] In order to enable those skilled in the art to better understand the solutions of the present application, the technical solutions in the embodiments of the present application will be clearly and completely described below in conjunction with the drawings in the embodiments of the present application. Apparently, the described embodiments are only some of the embodiments of the present application, not all of them. Based on the embodiments in this application, all other embodiments obtained by persons of ordinary skill in the art without creative efforts shall fall within the scope of protection of this application.

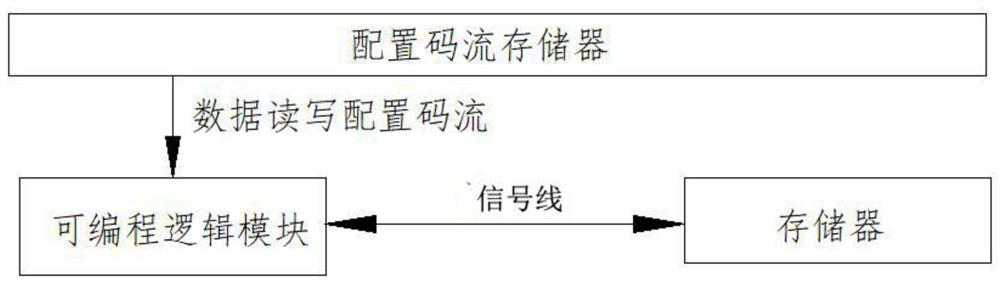

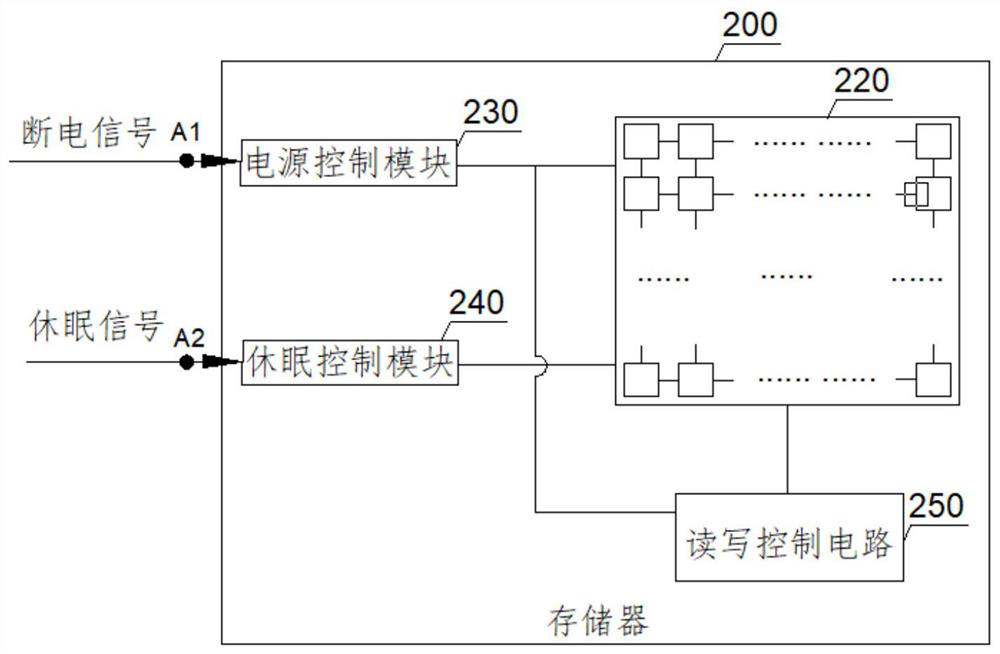

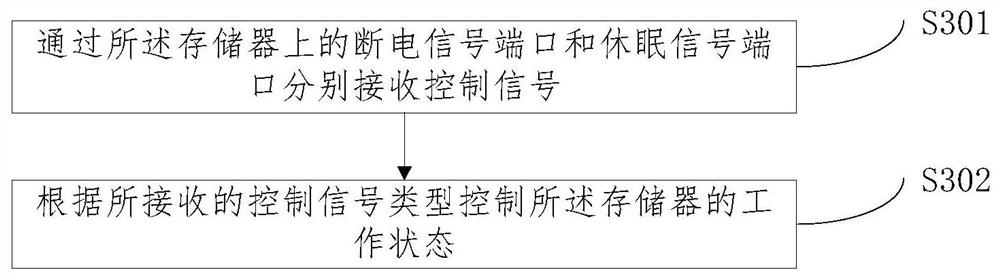

[0039] Such as figure 1 As shown, in the configuration of the existing FPGA chip, all the functional logics of the memory will be powered on and enabled at one time. However, the utilization rate of the memory in the FPGA chip is low. For example, the utilization rate of the memory in the FPGA chip is 50%, and the remaining 50% of memory resources are no...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More