Nano CMOS circuit fault-tolerant mapping method capable of optimizing power consumption

A mapping method and circuit technology, applied in the field of integrated circuits, can solve problems such as increased power consumption of nano-CMOS circuits, and achieve the effects of improving solution speed, optimizing power consumption, and reducing circuit fault tolerance complexity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

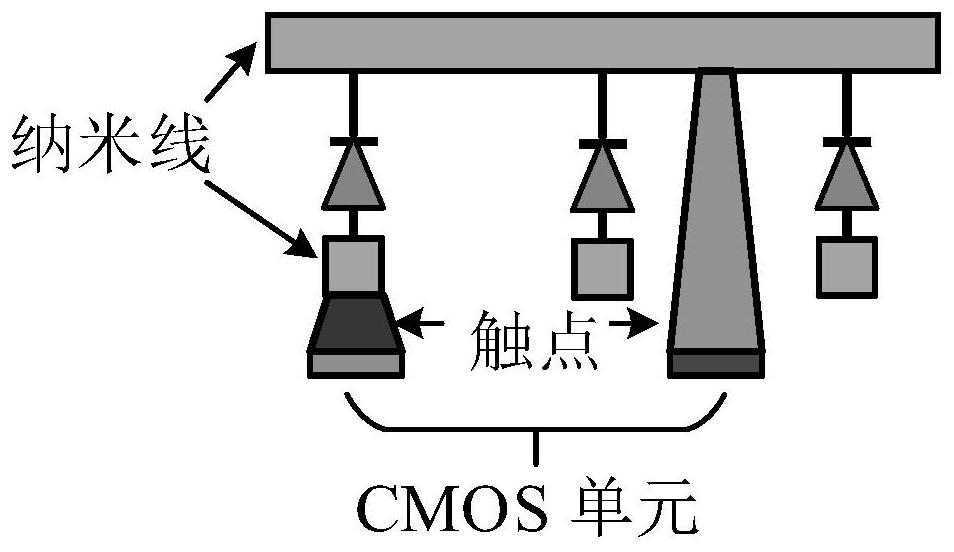

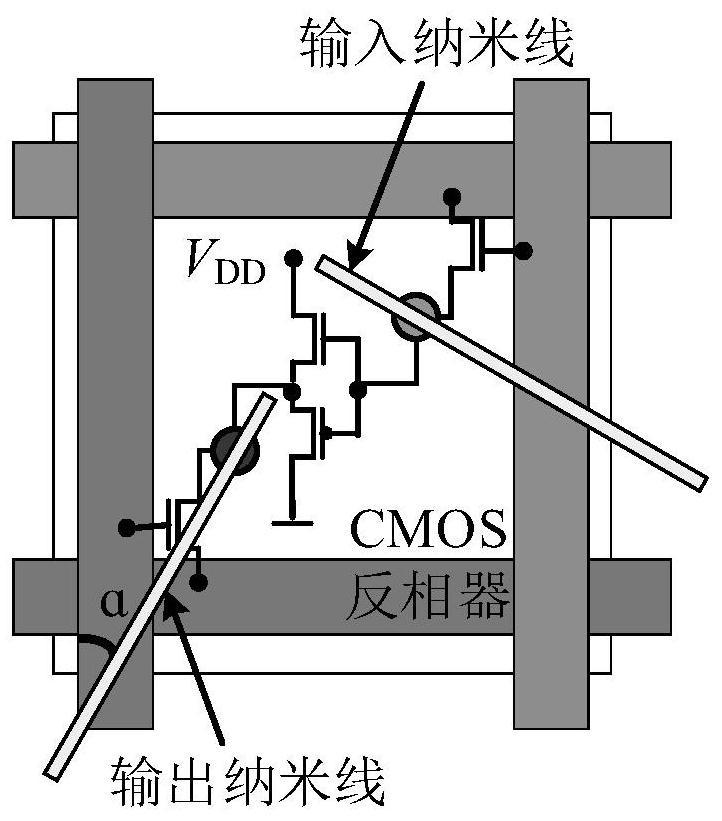

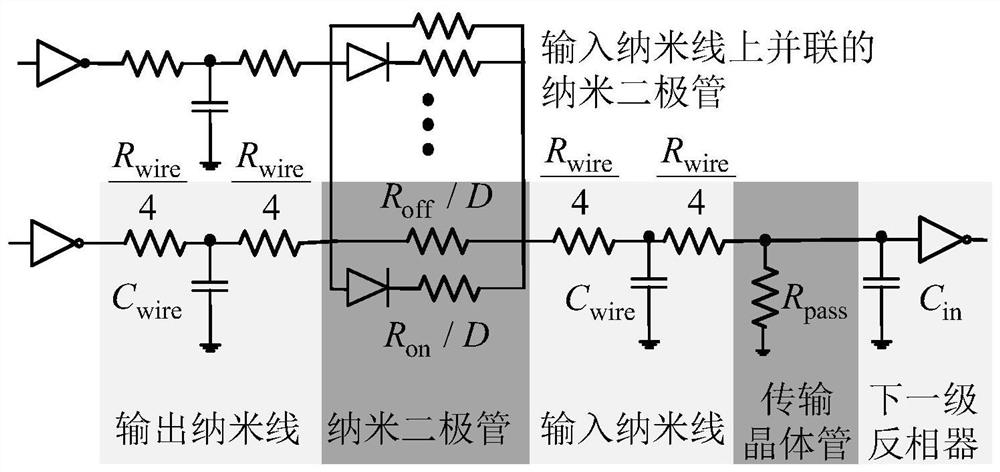

Method used

Image

Examples

Embodiment 1

[0075] Embodiment 1: using the fault-tolerant mapping method of the present invention, the Figure 7 The logic circuit shown with 8 nodes maps to Figure 8 Defect nanoscale CMOS circuit of 4 x 4 size is shown. exist Figure 7 In the logic circuit of , there are 3 original inputs {i 1 ,i 2 ,i 3}, 3 logical nodes {g 1 , g 2 , g 3}, 2 raw outputs {o 1 ,o 2}, each node is coded according to the integer {i 1 ,i 2 ,i 3 , g 1 , g 2 , g 3 ,o 1 ,o 2}→{0,1,2,3,4,5,6,7}. exist Figure 8 In the nano-CMOS circuit of , the black dots on the nano-wires represent nano-diodes with normally connected defects. The normal nano-devices are not shown, and the units A, B, C, D, and E are normally-connected units. According to their positions in the circuit, they are From bottom to top and from left to right, it is encoded as {D,C,B,A,E}→{0,1,2,3,4}, and stored in the set P. Assuming that the radius of the connected domain is large enough, each unit is in the connected domain of e...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More