Fault-tolerant method of torus network based on topology reconfiguration and path planning

A technology of topology reconfiguration and path planning, applied in the direction of advanced technology, climate sustainability, sustainable communication technology, etc., can solve the problem of rising solution time, reduce delay, shorten rescheduling time, and facilitate load balancing Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0204] The first TT message is marked as Msg

[0205] tt.src represents the source node, tt.dest represents the destination node, tt.length represents the message frame length, tt.period

[0216]

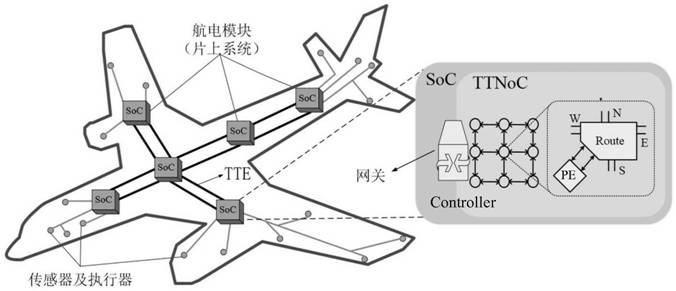

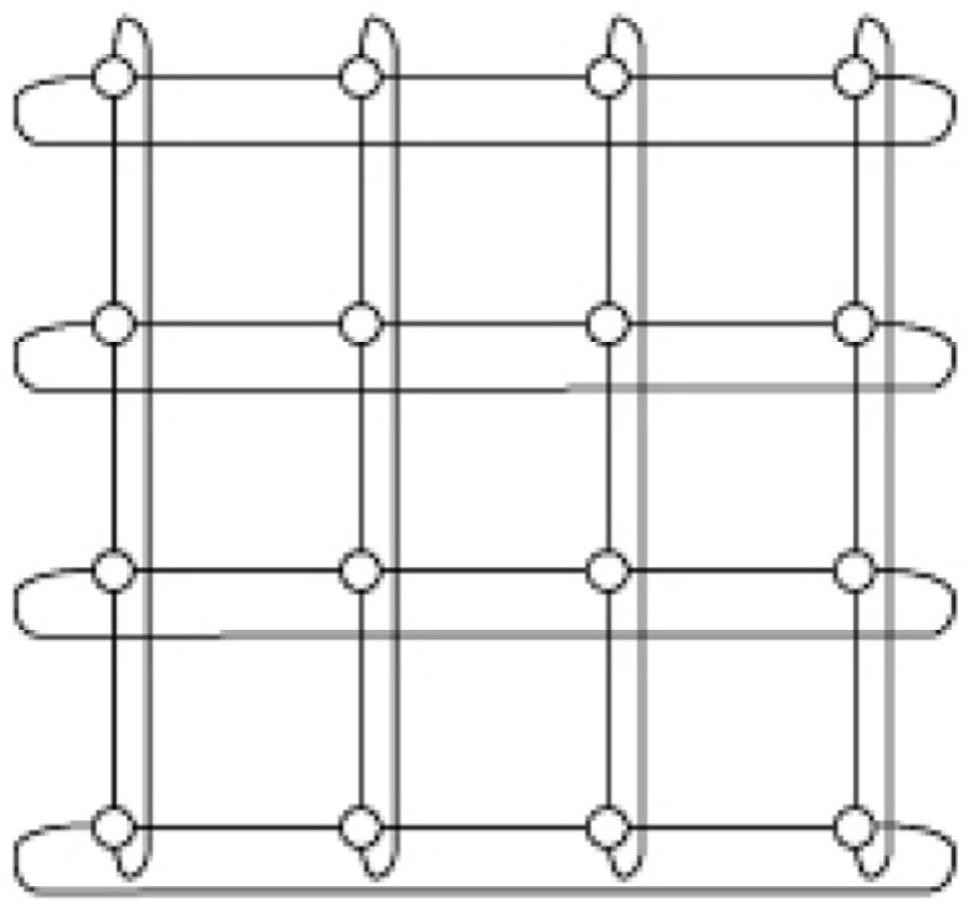

[0221] The avionics network-on-chip was configured according to Torus to obtain the avionics-on-chip topology. network on chip

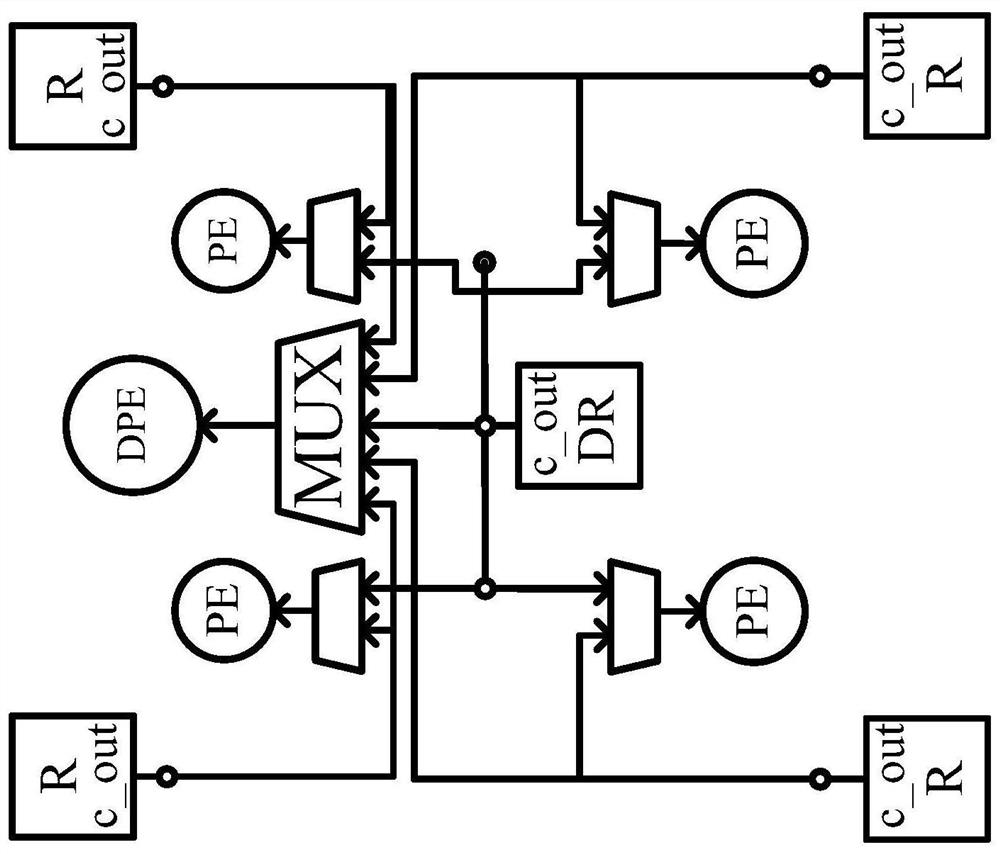

[0228] Step 2: Set the area block-processing unit and the area block-router in each node-area block to obtain

[0229] respectively set one area block-processing unit and one area in the 6 area blocks obtained in step 1

[0230] For example, by the node NE

[0231] The same can be obtained: in the second area block QU

[0238] In the present invention, a built-in self-test mechanism is used to obtain fault information. The fault information BD includes node fault information

Embodiment 2

[0250] tt.src represents source node, tt.dest represents destination node, tt.length represents message frame length, tt.period

[0261]

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More