Self-adaptive resource configuration, layout and wiring method and system for storage and calculation integrated framework

A technology of layout, routing and resource allocation, which is applied in the field of adaptive resource configuration layout and routing of the storage-computing integrated architecture, which can solve the application development that limits the storage-computing integrated architecture, and the layout and routing algorithm cannot be applied to the layout and routing tasks of the storage-computing integrated architecture, etc. problem, to achieve the effect of improving the utilization rate

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

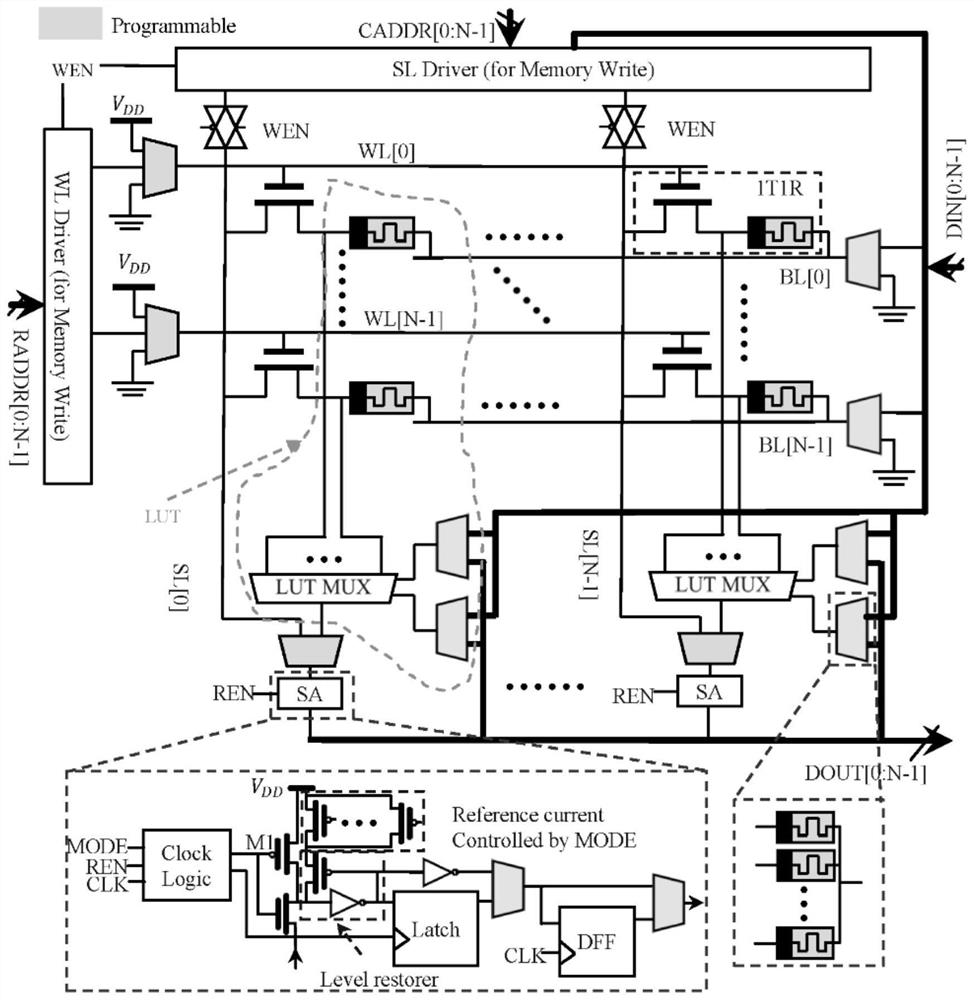

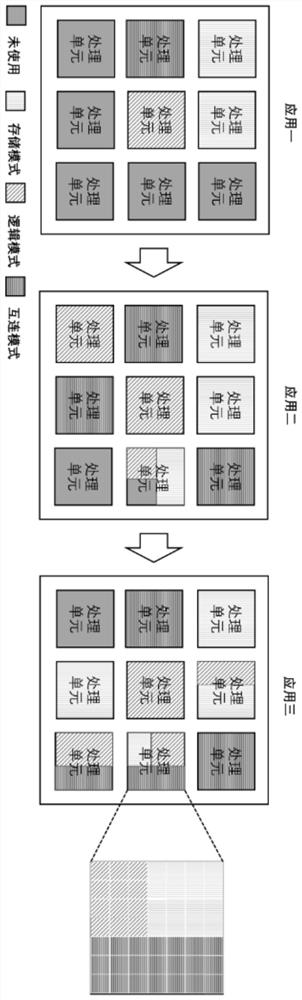

[0069] see figure 1 , figure 2 , an adaptive resource allocation layout and routing method for an integrated storage-computing architecture, followed by the following steps:

[0070] 1. Use the circuit written in Verilog language as input, use ODIN II tool to read and analyze the file, and generate a netlist file in blif format;

[0071] 2. Use the ABC logic synthesis and optimization tool to read the generated netlist file, and compile and optimize to generate a blif netlist file containing logic gate information;

[0072] 3. Read the blif netlist file containing logic gate information, and set the initial value of the storage-computing integrated architecture composed of multiple storage-computing swap processing units, including first setting the storage-computing swap processing in the storage-computing integrated architecture The hardware resource configuration of the unit, and then specify the number of storage and calculation swap processing units;

[0073] 4. Use t...

Embodiment 2

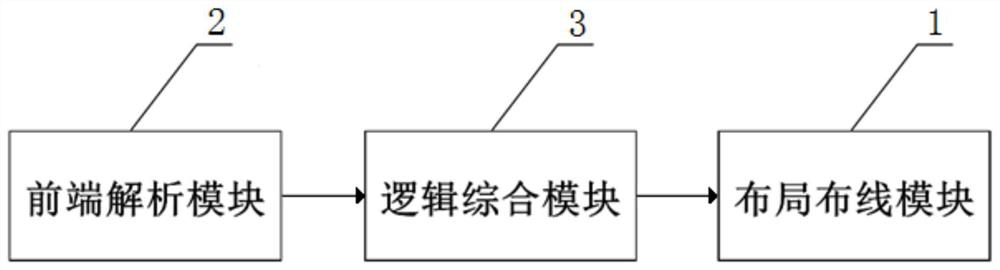

[0085] see image 3 , an adaptive resource configuration layout and wiring system with integrated storage and computing architecture, including a layout and wiring module 1, a front-end analysis module 2, and a logic synthesis module 3, and the signal output terminal of the front-end analysis module 2 is connected with the layout and wiring by the logic synthesis module 3 The signal input terminal of module 1 is connected;

[0086] The front-end parsing module 2 executes step 1 described in Embodiment 1;

[0087] The logic synthesis module 3 is used to execute step 2 described in Embodiment 1;

[0088] The layout and wiring module 1 is used to execute the steps 3-9 in the first embodiment.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More