Semiconductor device and manufacturing method of semiconductor device

A manufacturing method and semiconductor technology, which is applied in semiconductor/solid-state device manufacturing, semiconductor devices, semiconductor/solid-state device components, etc., can solve problems such as deterioration of insulation properties, and achieve the effect of suppressing poor insulation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment approach 1

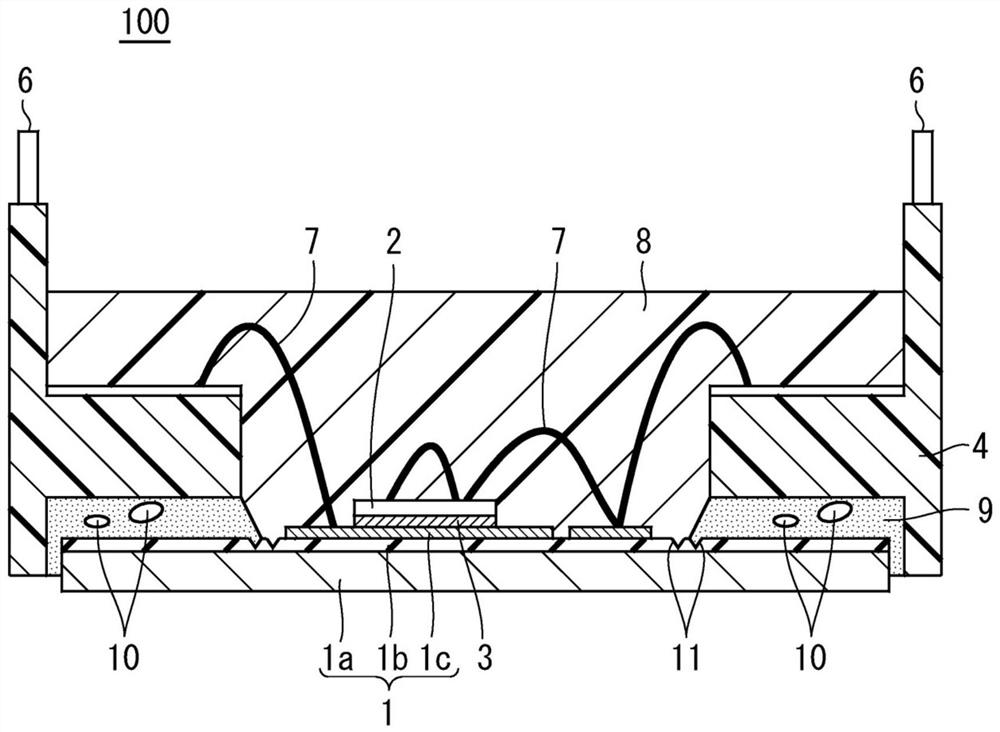

[0015] Hereinafter, Embodiment 1 will be described with reference to the drawings. figure 1 It is a cross-sectional view of the semiconductor device 100 according to the first embodiment.

[0016] like figure 1 As shown, the semiconductor device 100 has a resin-insulated copper base plate 1 , a semiconductor element 2 , a case 4 , electrode terminals 6 , a packaging material 8 , and a roughening pattern 11 .

[0017] The resin-insulated copper base plate 1 has a copper base plate 1a, an insulating layer 1b, and a circuit pattern 1c. The copper base plate 1a, the insulating layer 1b, and the circuit pattern 1c are integrated. The copper base plate 1a is formed in a rectangular shape in plan view. The insulating layer 1b is provided over the entire upper surface of the copper base plate 1a. The insulating layer 1b is made of resin and has a thickness of 0.2 mm. The circuit pattern 1c is provided at a portion other than the outer peripheral portion at the upper surface of th...

Embodiment approach 2

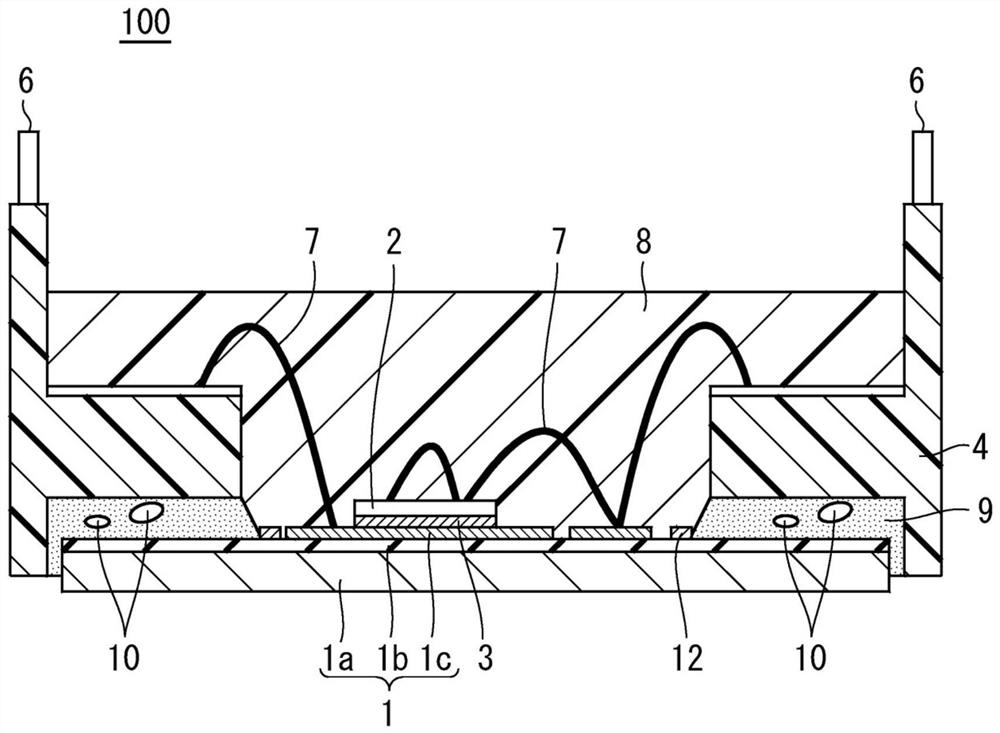

[0031] Next, the semiconductor device 100 according to the second embodiment will be described. figure 2 It is a cross-sectional view of the semiconductor device 100 according to the second embodiment. In addition, in Embodiment 2, the same code|symbol is attached|subjected to the same component as the component demonstrated in Embodiment 1, and description is abbreviate|omitted.

[0032] like figure 2 As shown, in Embodiment 2, instead of the roughening pattern 11 , the semiconductor device 100 has the metal spacer 12 .

[0033] The metal spacer 12 is provided on the upper surface of the insulating layer 1b so as to continuously surround the circuit pattern 1c in a plan view. The metal spacer 12 is made of a metal that can be bonded to the insulating layer 1b, and is formed in a rectangular frame shape in plan view. The metal that can be bonded to the insulating layer 1b is, for example, copper, nickel, aluminum, or the like, but copper is preferable in consideration of ...

Embodiment approach 3

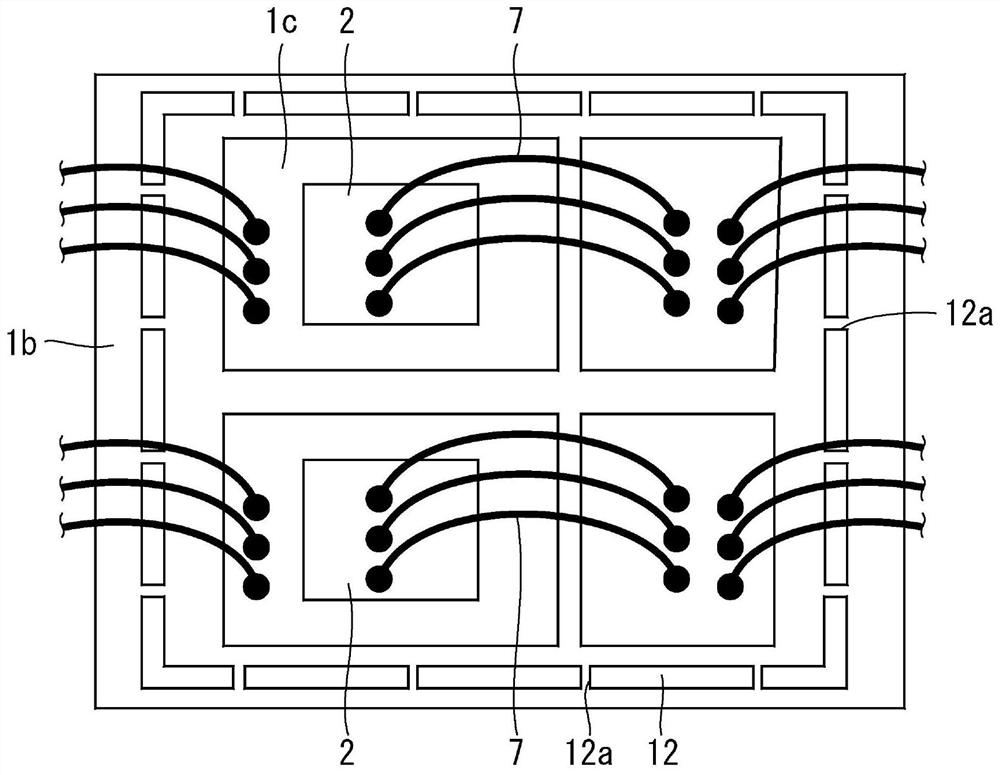

[0042] Next, the semiconductor device 100 according to the third embodiment will be described. image 3 It is a plan view of the resin-insulated copper base plate 1 included in the semiconductor device according to Embodiment 3 and its surroundings. In addition, in Embodiment 3, the same code|symbol is attached|subjected to the same component as the component demonstrated in Embodiment 1, 2, and description is abbreviate|omitted.

[0043] In Embodiment 2, the metal spacer 12 is provided on the upper surface of the insulating layer 1b so as to continuously surround the circuit pattern 1c in plan view, but as image 3 As shown, in Embodiment 3, the metal spacer 12 is provided on the upper surface of the insulating layer 1b so as to surround the circuit pattern 1c intermittently in a plan view. Therefore, gaps 12a are provided in the metal spacer 12 at predetermined intervals.

[0044] When the air bubbles 10 exist in the epoxy resin existing between the circuit pattern 1 c and...

PUM

| Property | Measurement | Unit |

|---|---|---|

| width | aaaaa | aaaaa |

| width | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More