Patents

Literature

725 results about "Circuit graph" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

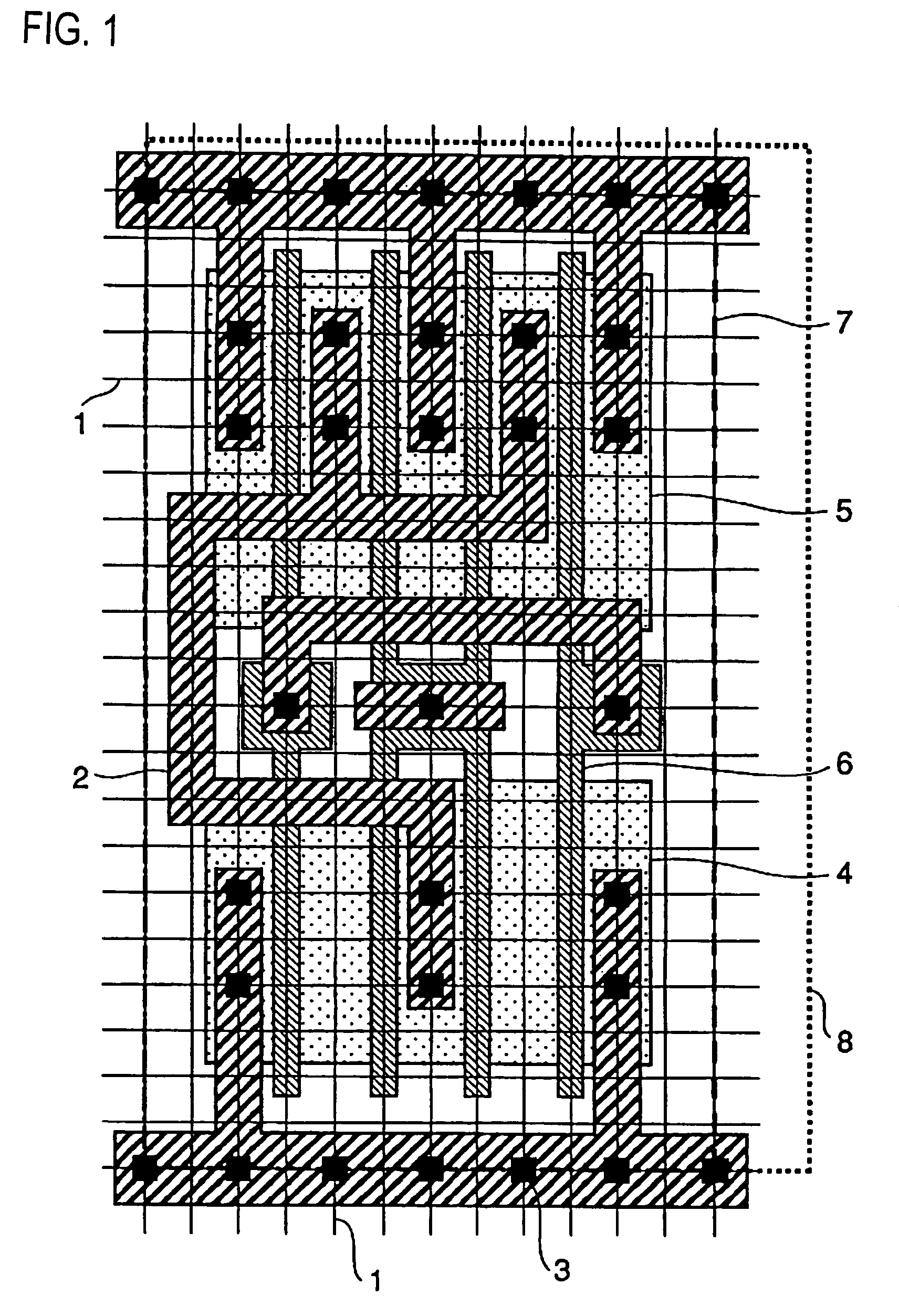

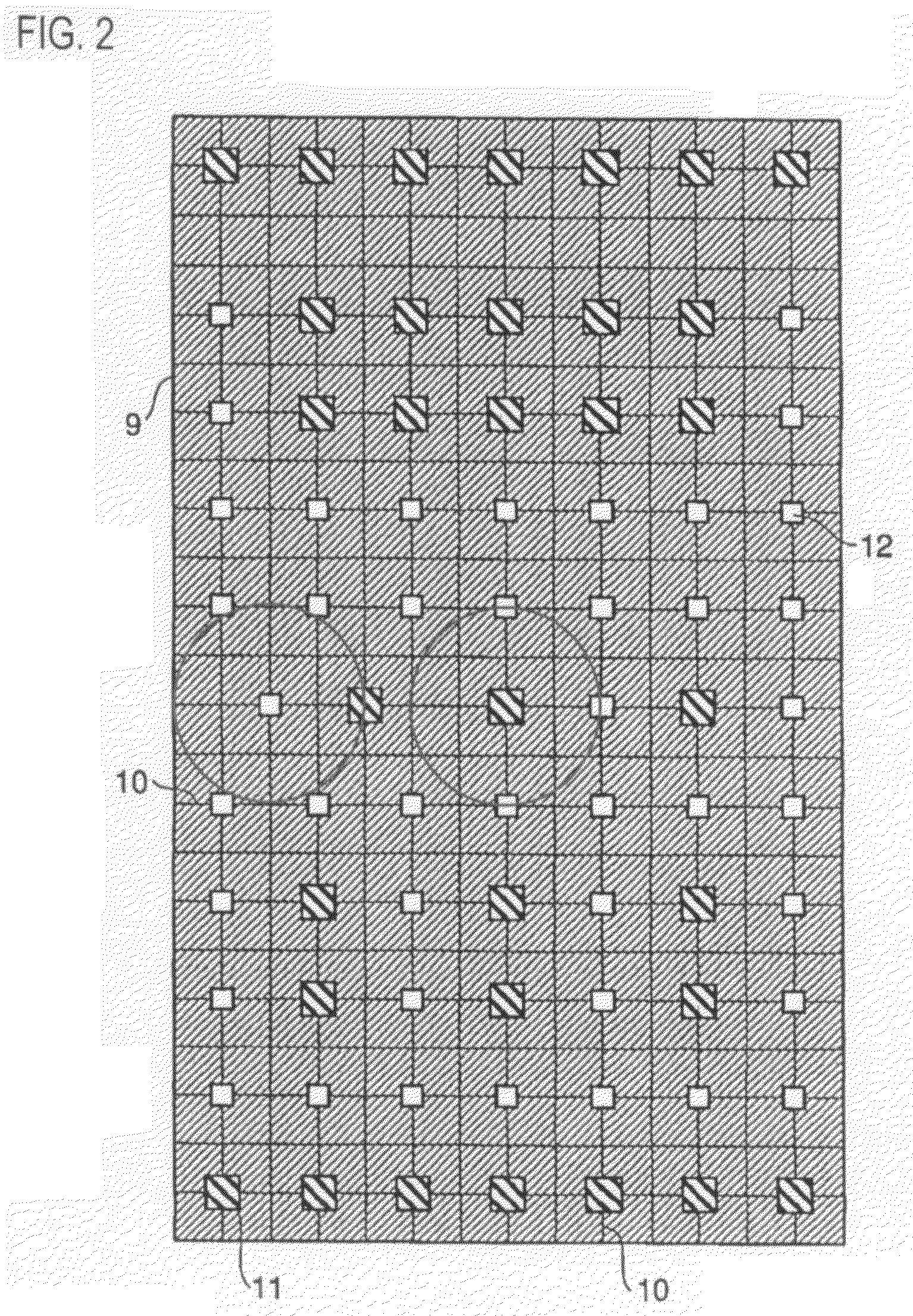

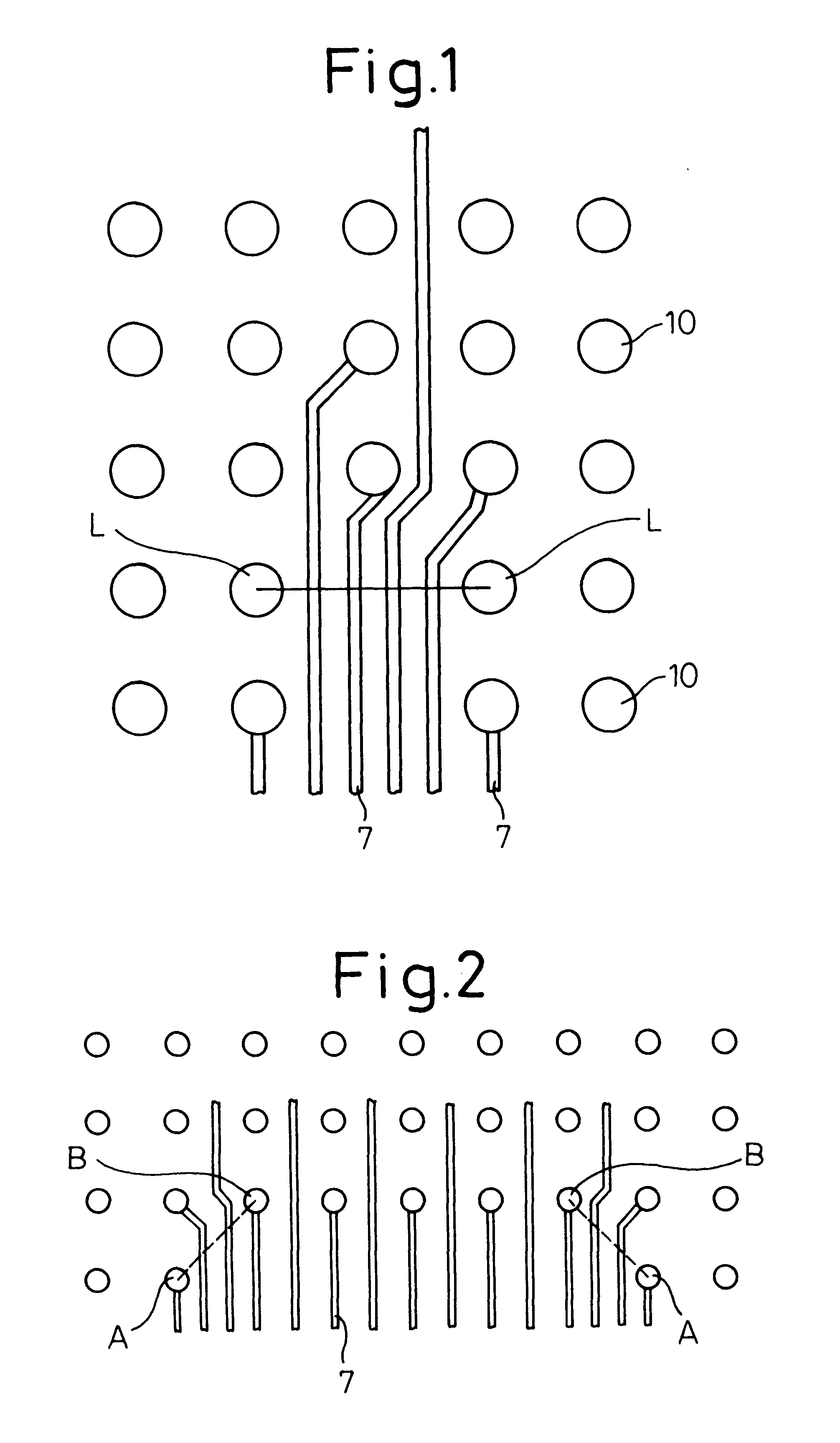

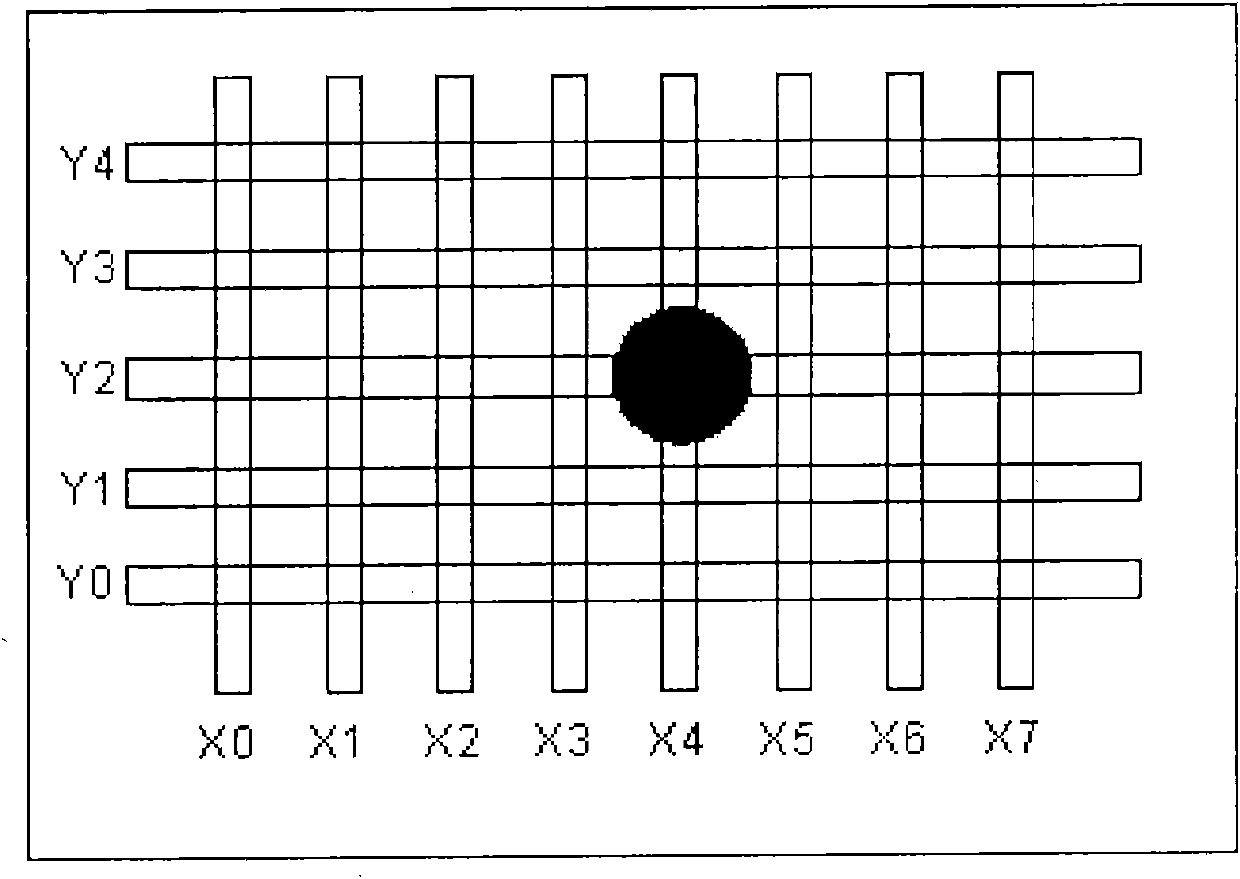

Method for providing layout design and photo mask

A method for providing the layout design of semiconductor integrated circuit that is capable of promoting the reduction of the circuit pattern area is provided. A hole pattern is disposed at the mesh point which is an intersecting point of mutually orthogonal virtual grid lines and another hole pattern is not disposed at the adjacent mesh point that is the closed mesh point having the hole pattern thereon.

Owner:RENESAS ELECTRONICS CORP

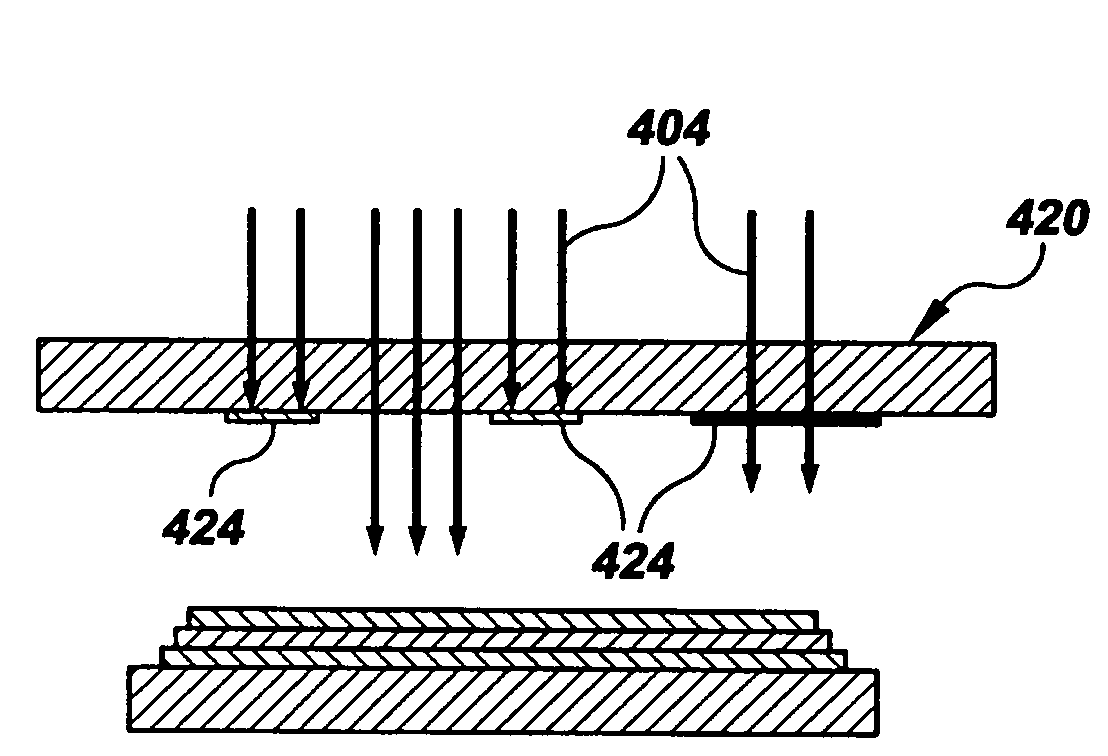

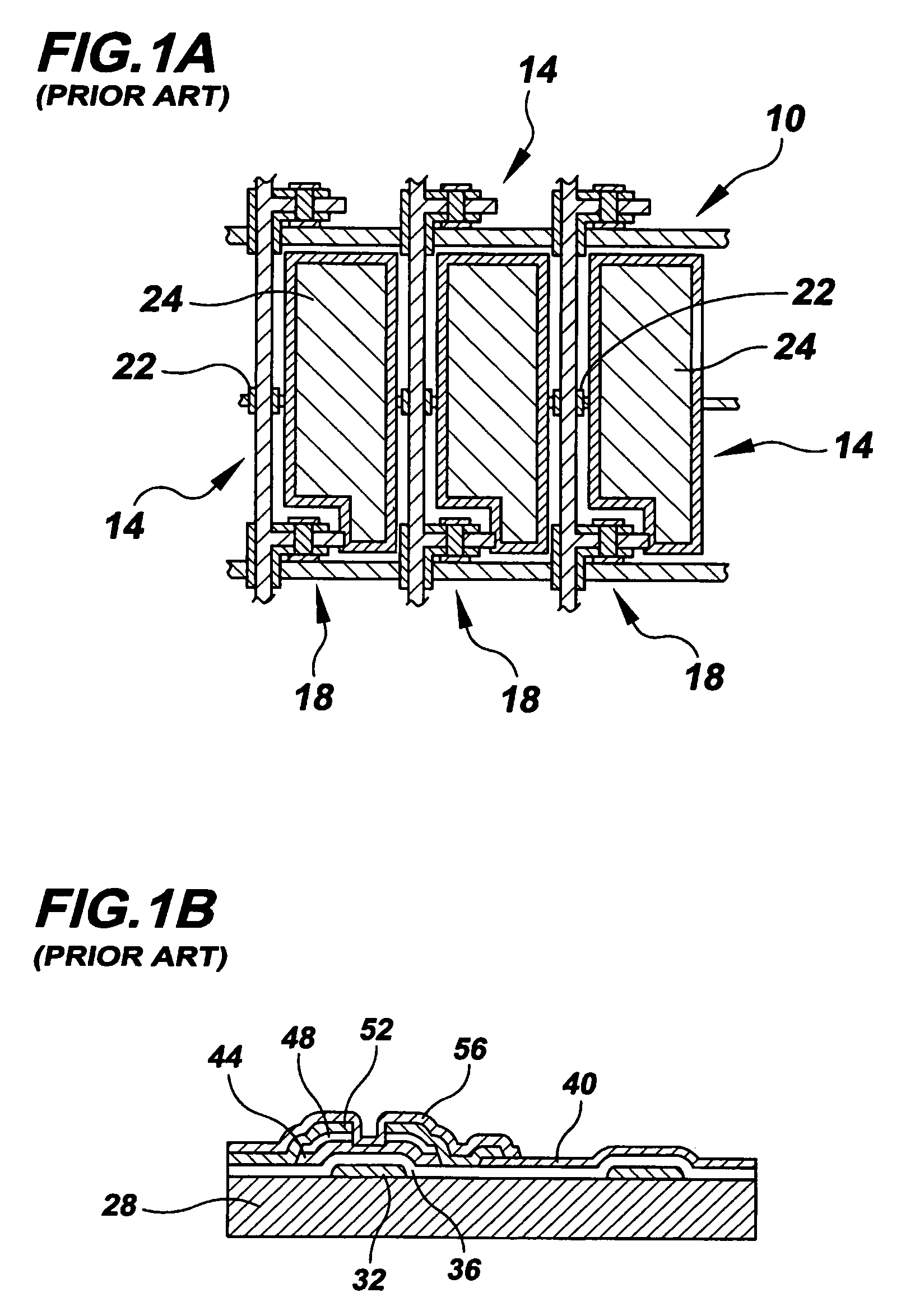

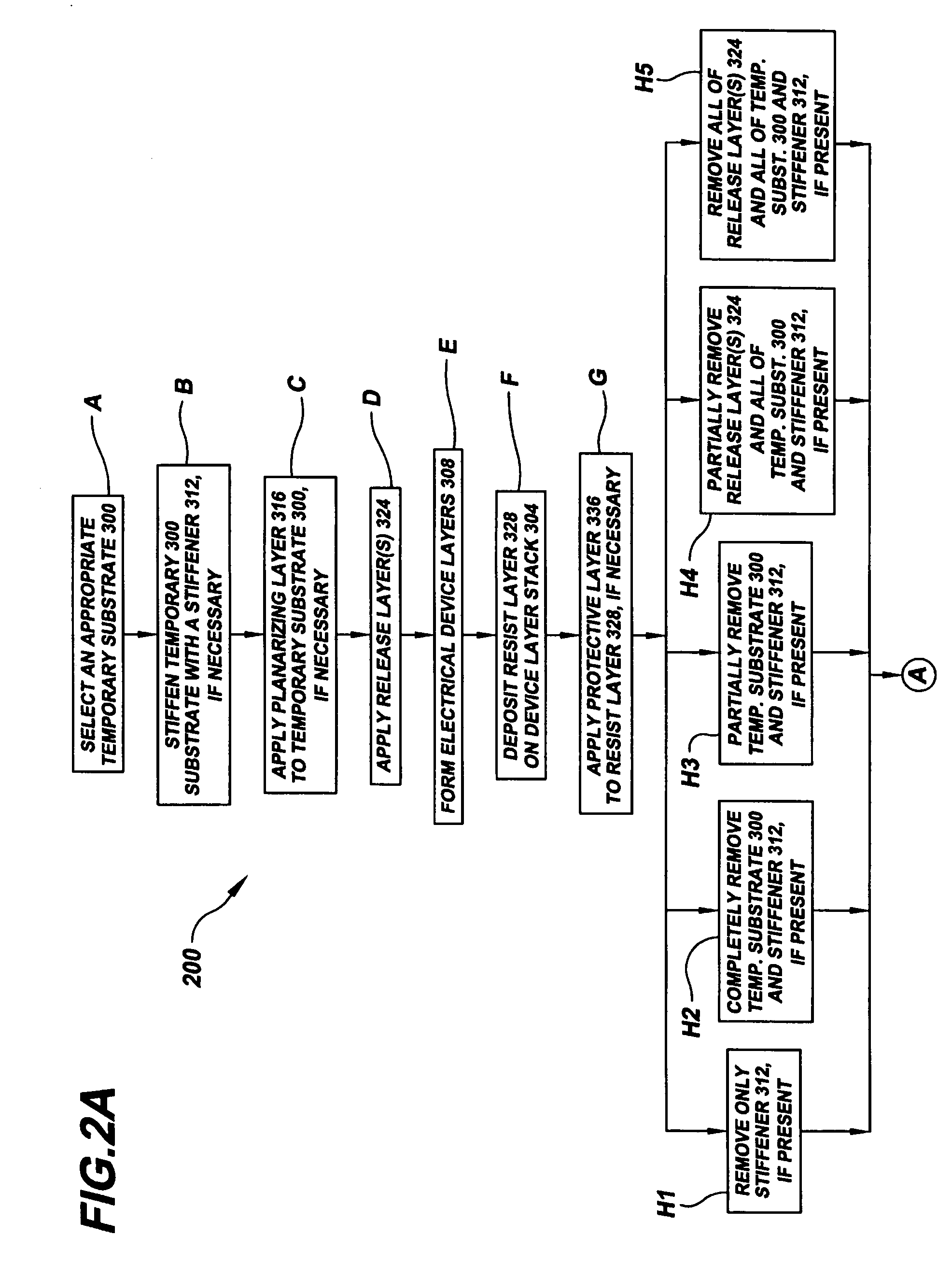

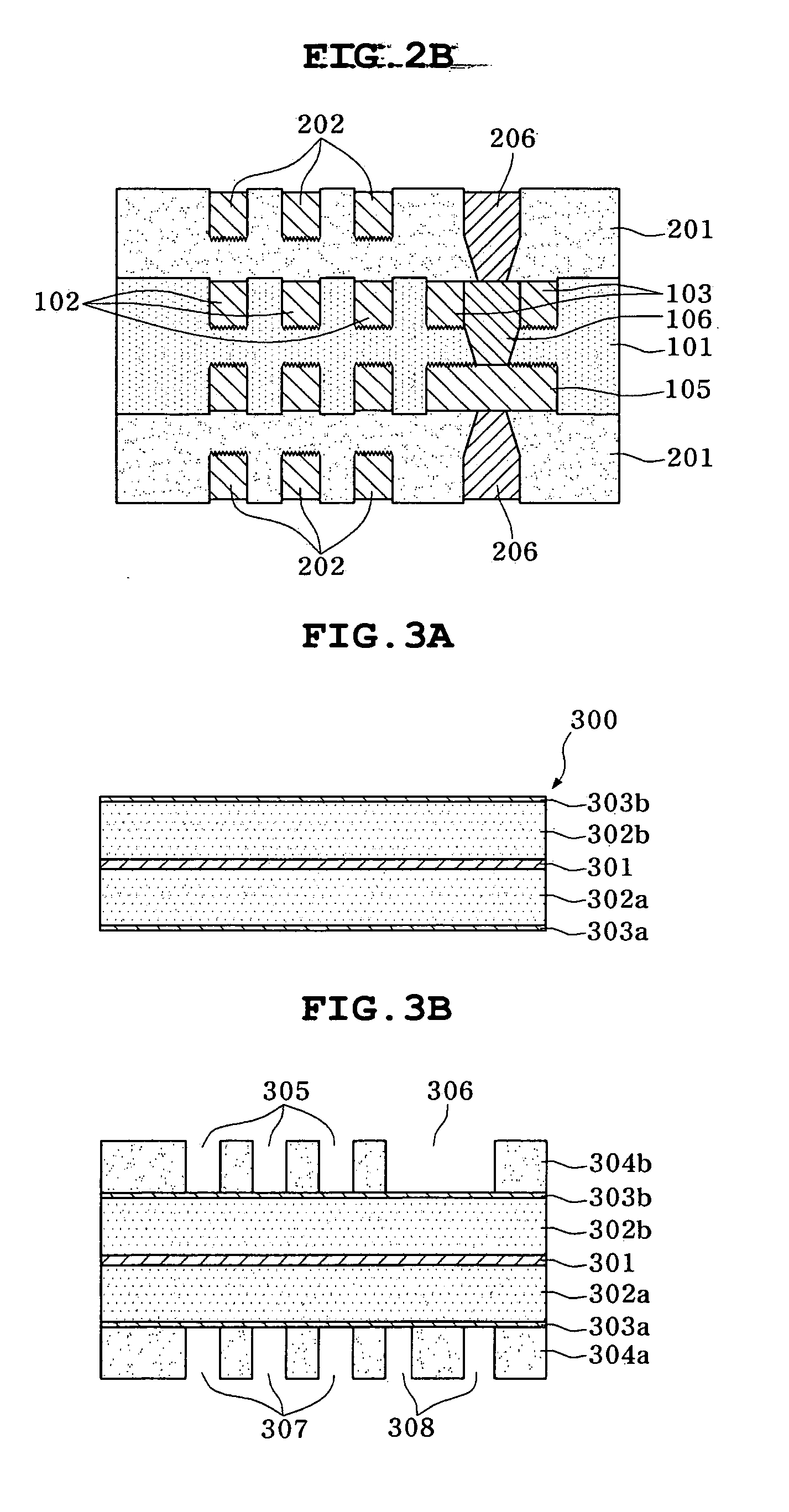

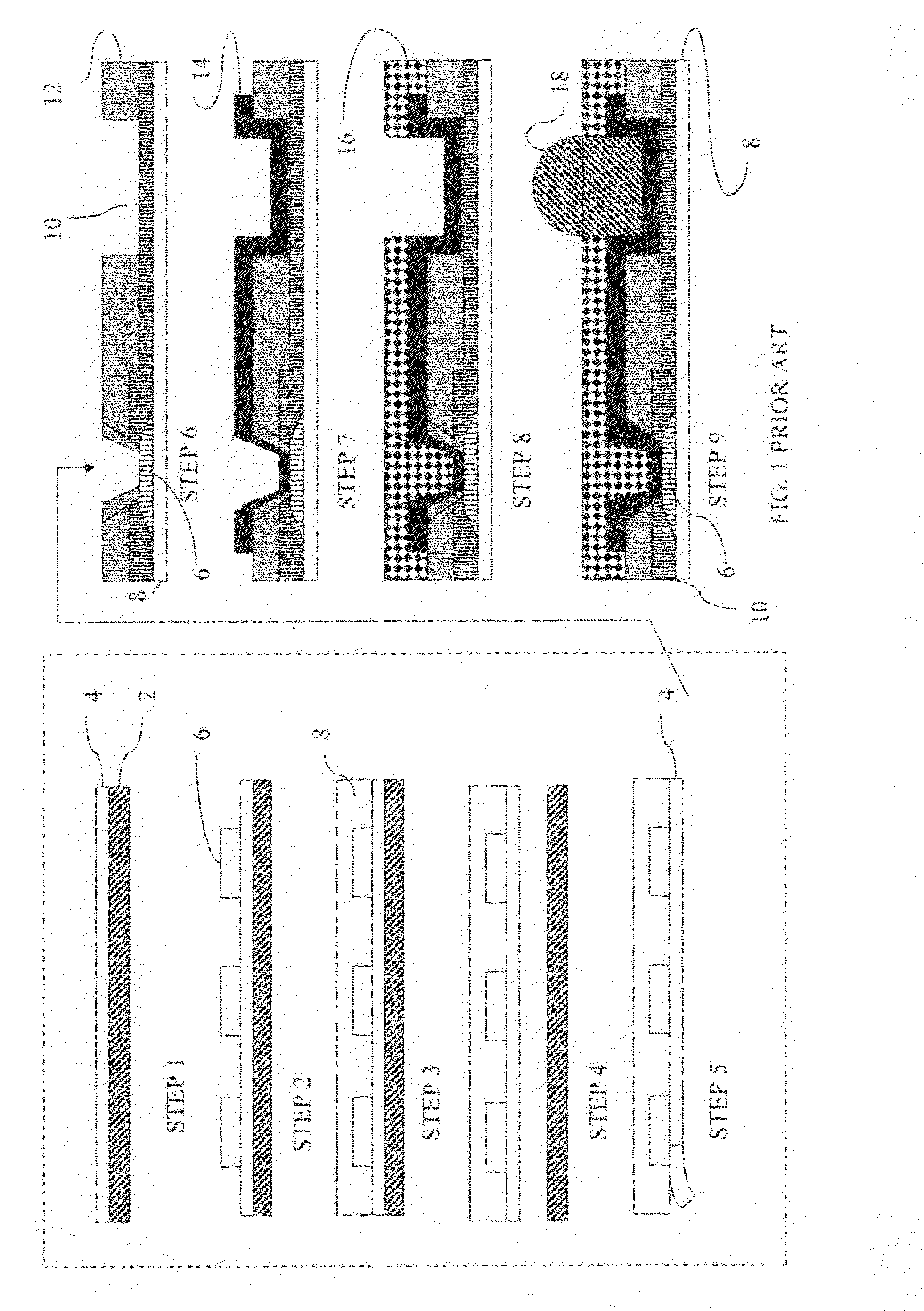

Method of making a microelectronic and/or optoelectronic circuitry sheet

InactiveUS7259106B2Printed electric component incorporationSolid-state devicesHemt circuitsThin membrane

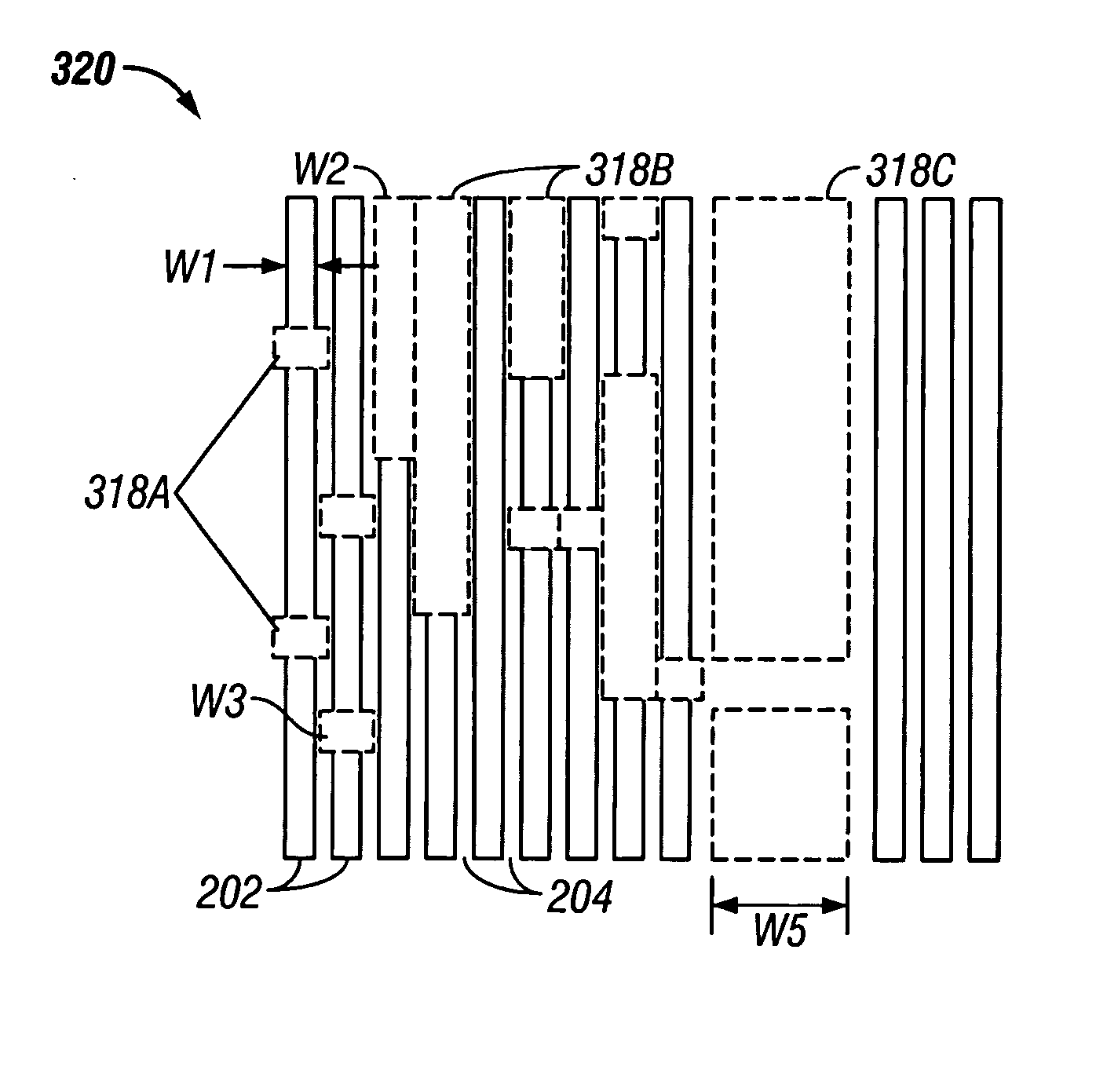

A circuitry sheet (322) comprising an electronic device layer stack (304) containing electronic devices, e.g., thin-film transistors, or portions thereof, formed by removing material from both sides of the device layer stack. The circuitry sheet may be made by an electronic / optoelectronic device manufacturing method (200) that includes the steps of forming the device layer stack on a temporary substrate (300), removing material from both sides of the device layer stack, and then attaching a permanent substrate (348) to the device layer stack. The method uses one or more resist layers (600) that may be activated simultaneously and independently to impart distinct circuit pattern images (603, 608, 612) into each of a plurality of image levels (612, 616, 620) within each resist layer, thereby obviating repetitive sequential exposure, registration and alignment steps.

Owner:VERSATILIS

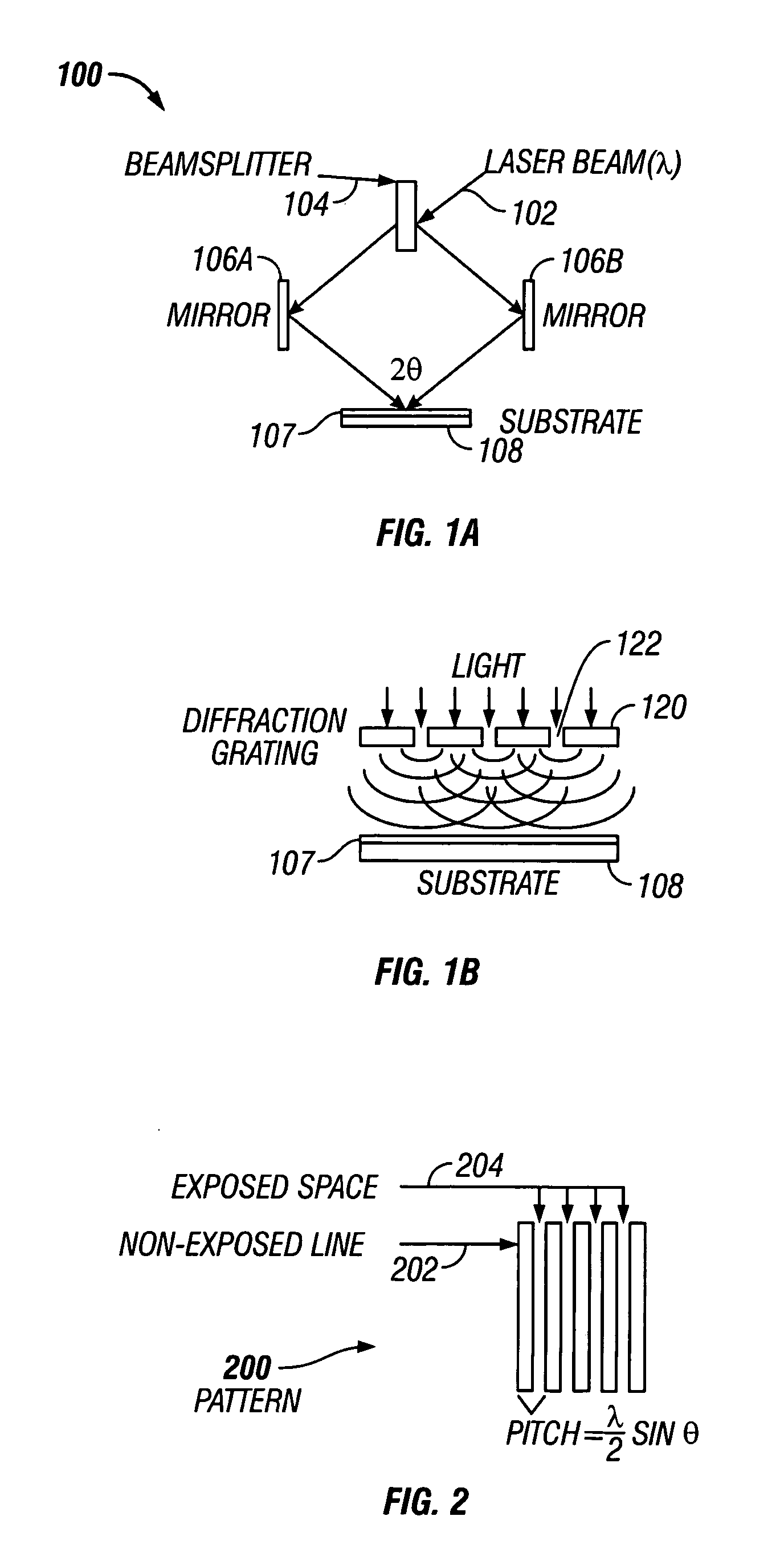

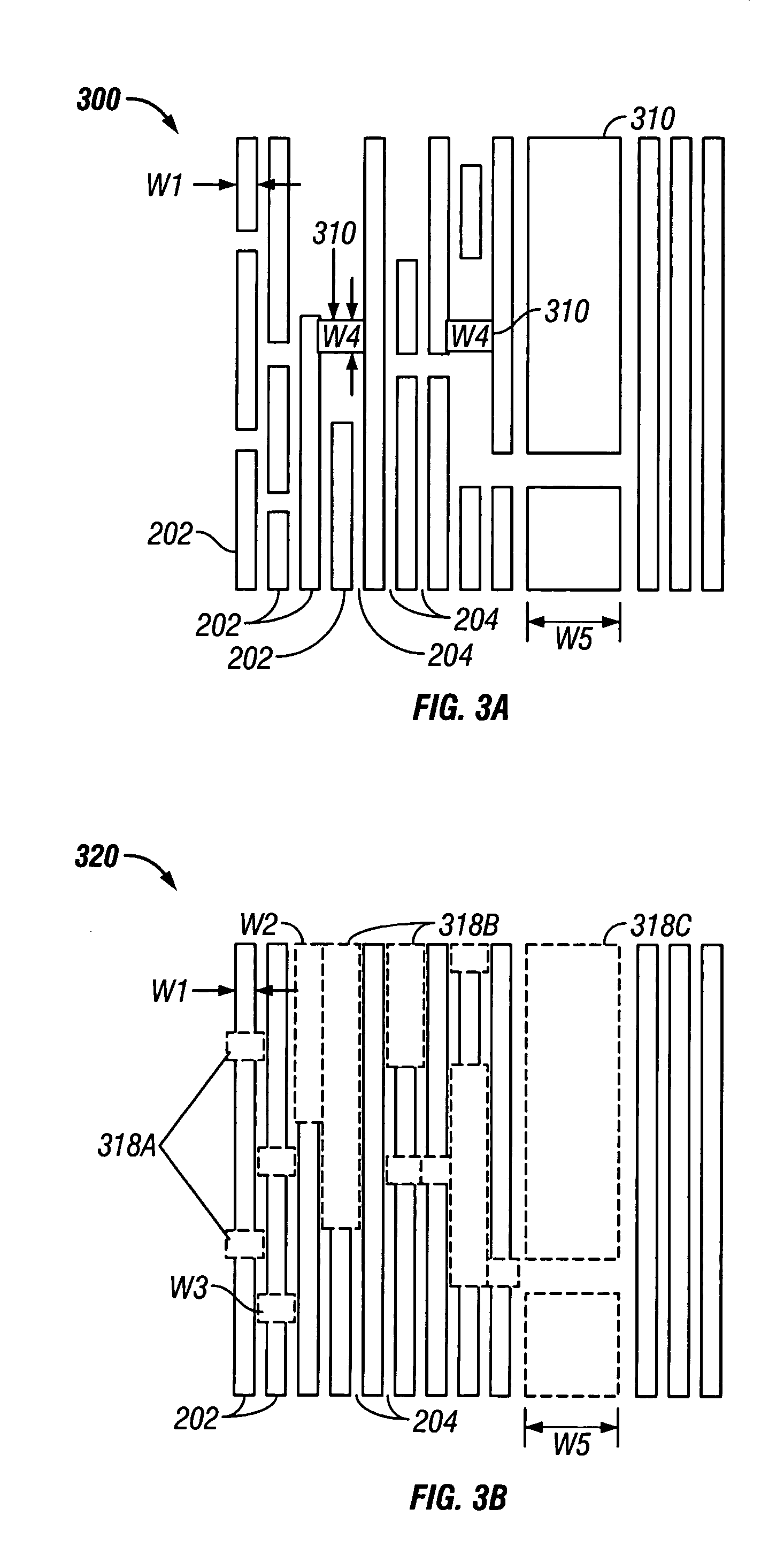

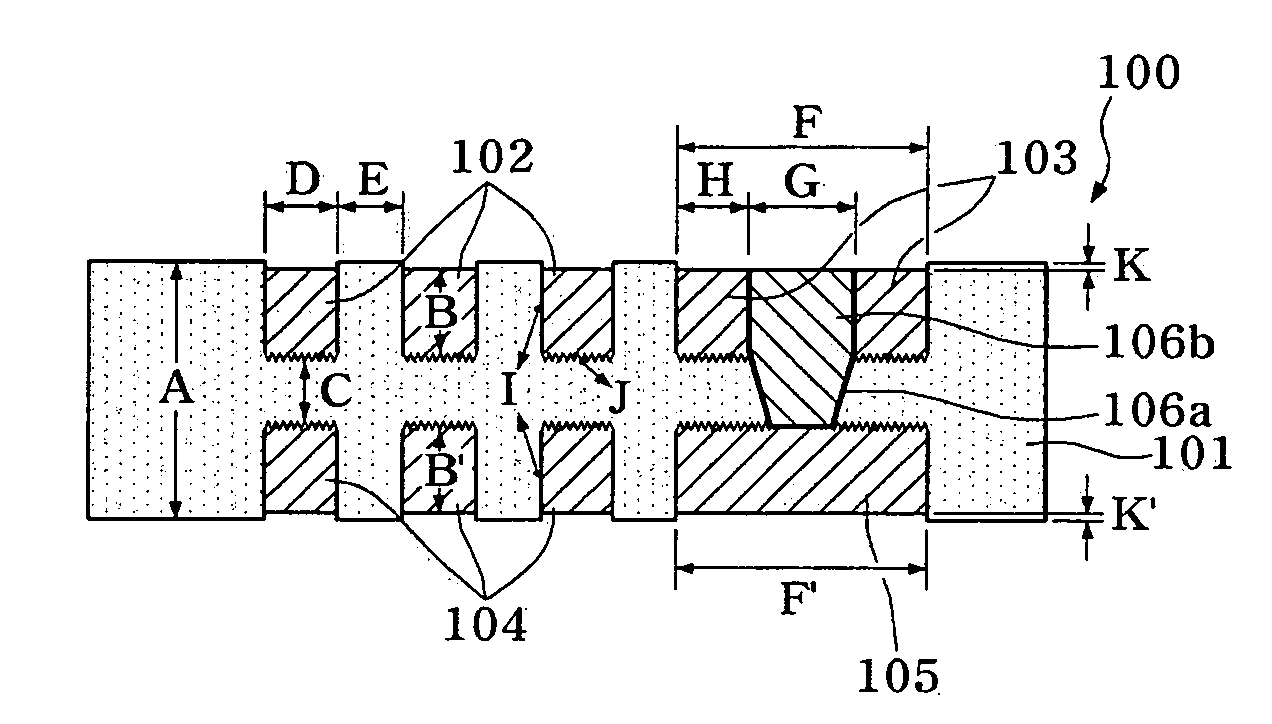

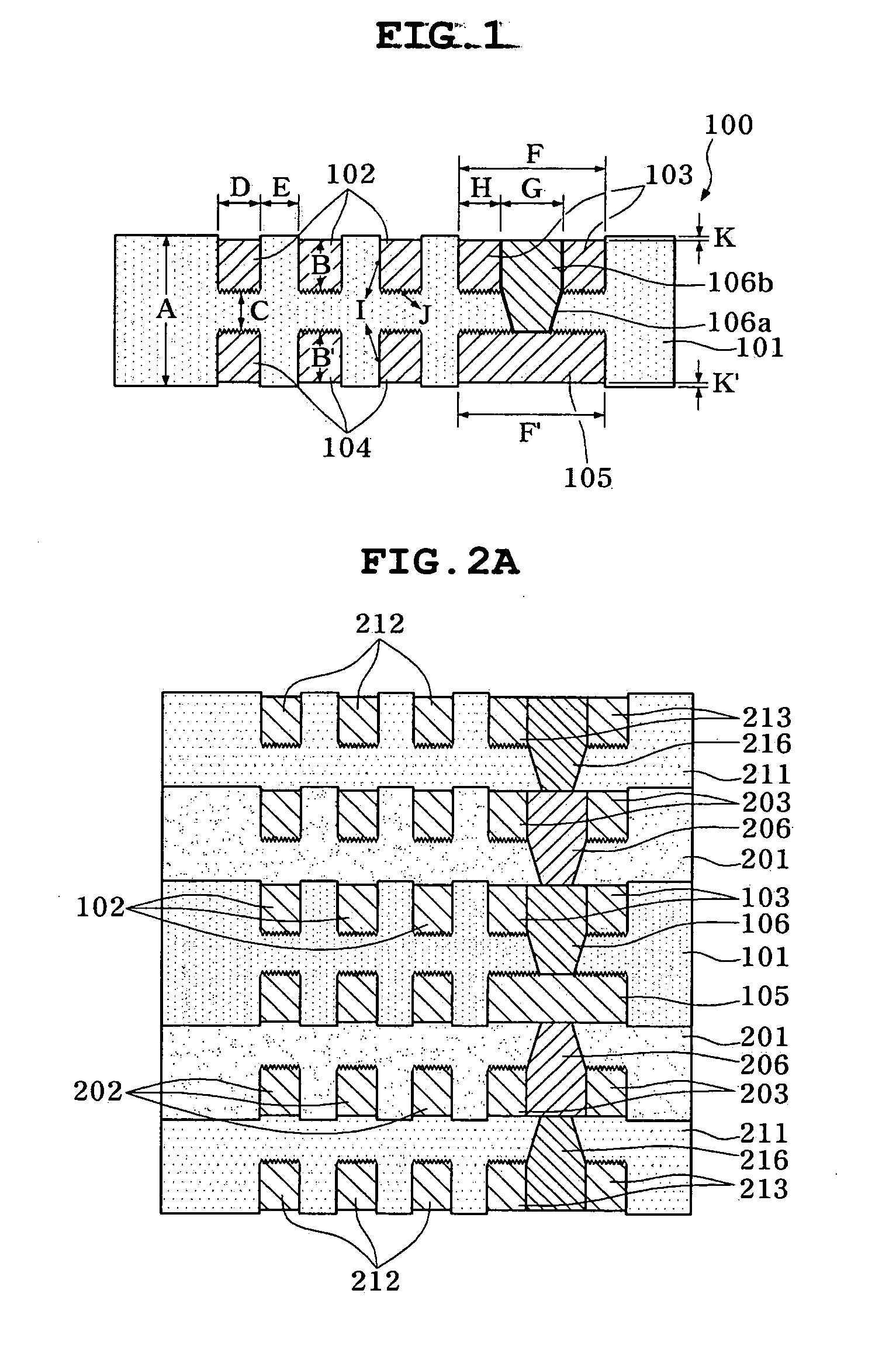

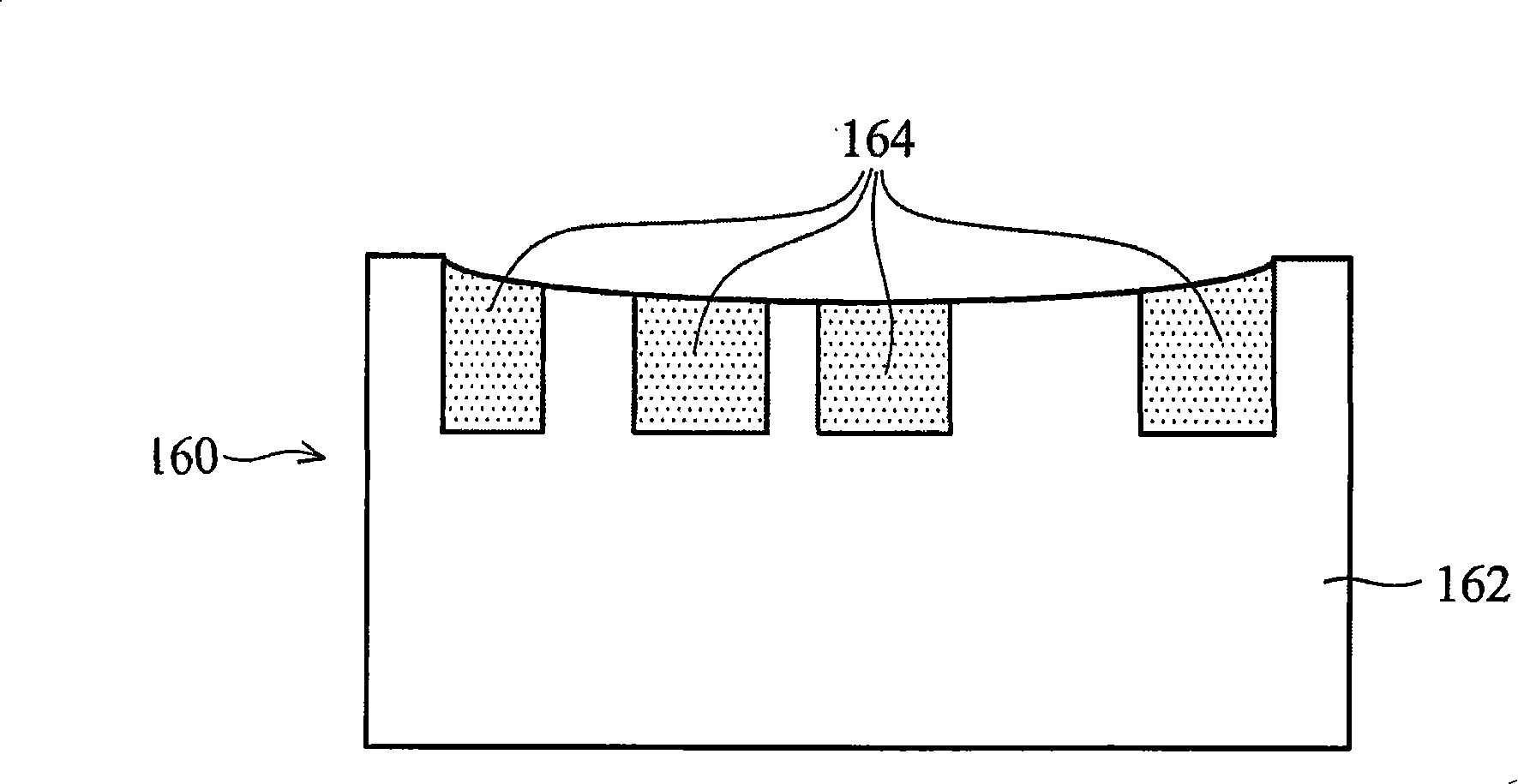

Composite optical lithography method for patterning lines of significantly different widths

InactiveUS20050074698A1Photo-taking processesSemiconductor/solid-state device manufacturingLithography processInterference lithography

A composite patterning technique may include three lithography processes. A first lithography process forms a periodic pattern of alternating continuous lines of substantially equal width and spaces on a first photoresist. A second lithography process uses a non-interference lithography technique to break continuity of the patterned lines and form portions of desired integrated circuit features. The first photoresist may be developed. A second photoresist is formed over the first photoresist. A third lithography process uses a non-interference lithography technique to expose a pattern on the second photoresist and form remaining desired features of an integrated circuit pattern.

Owner:INTEL CORP

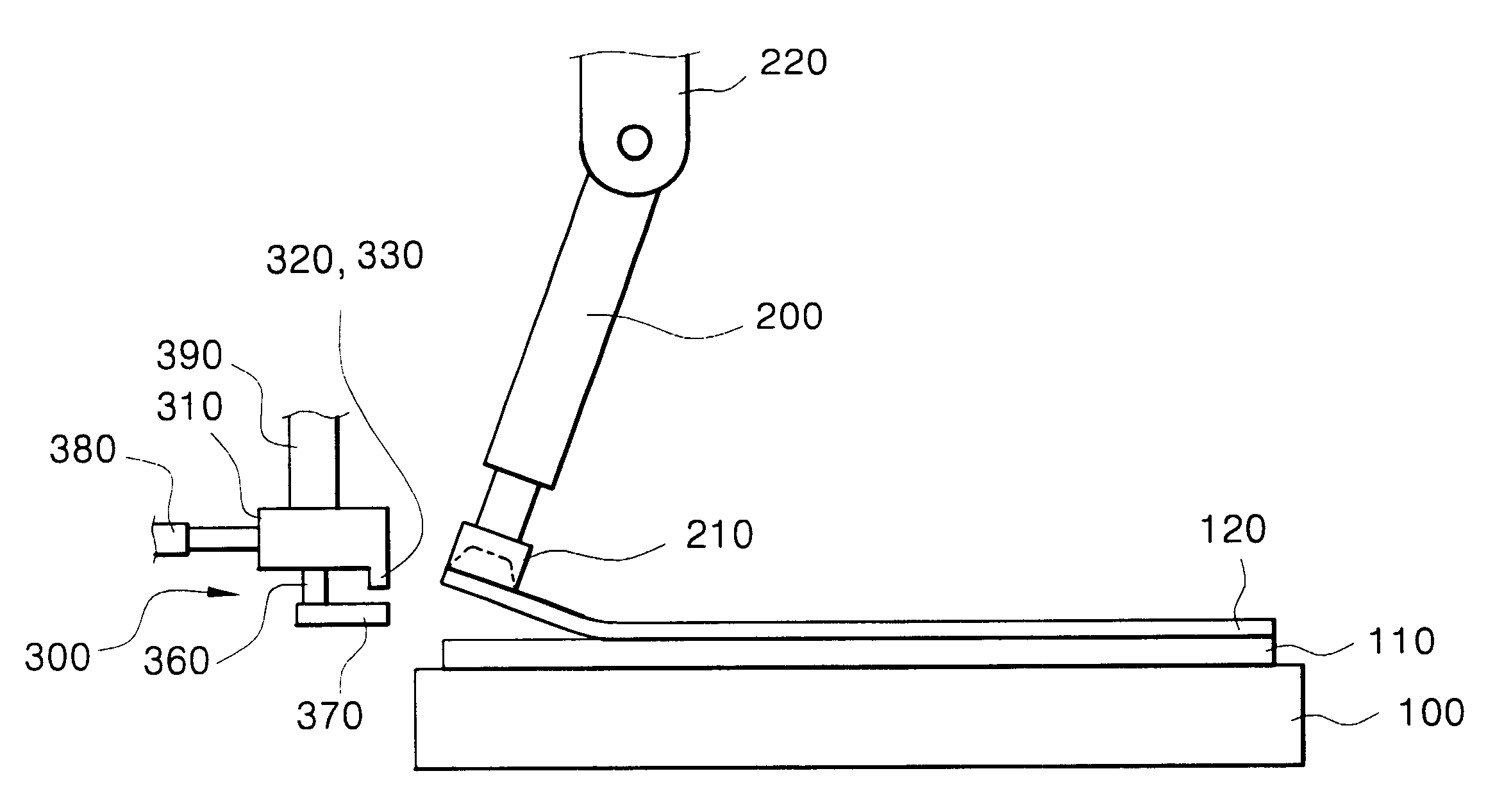

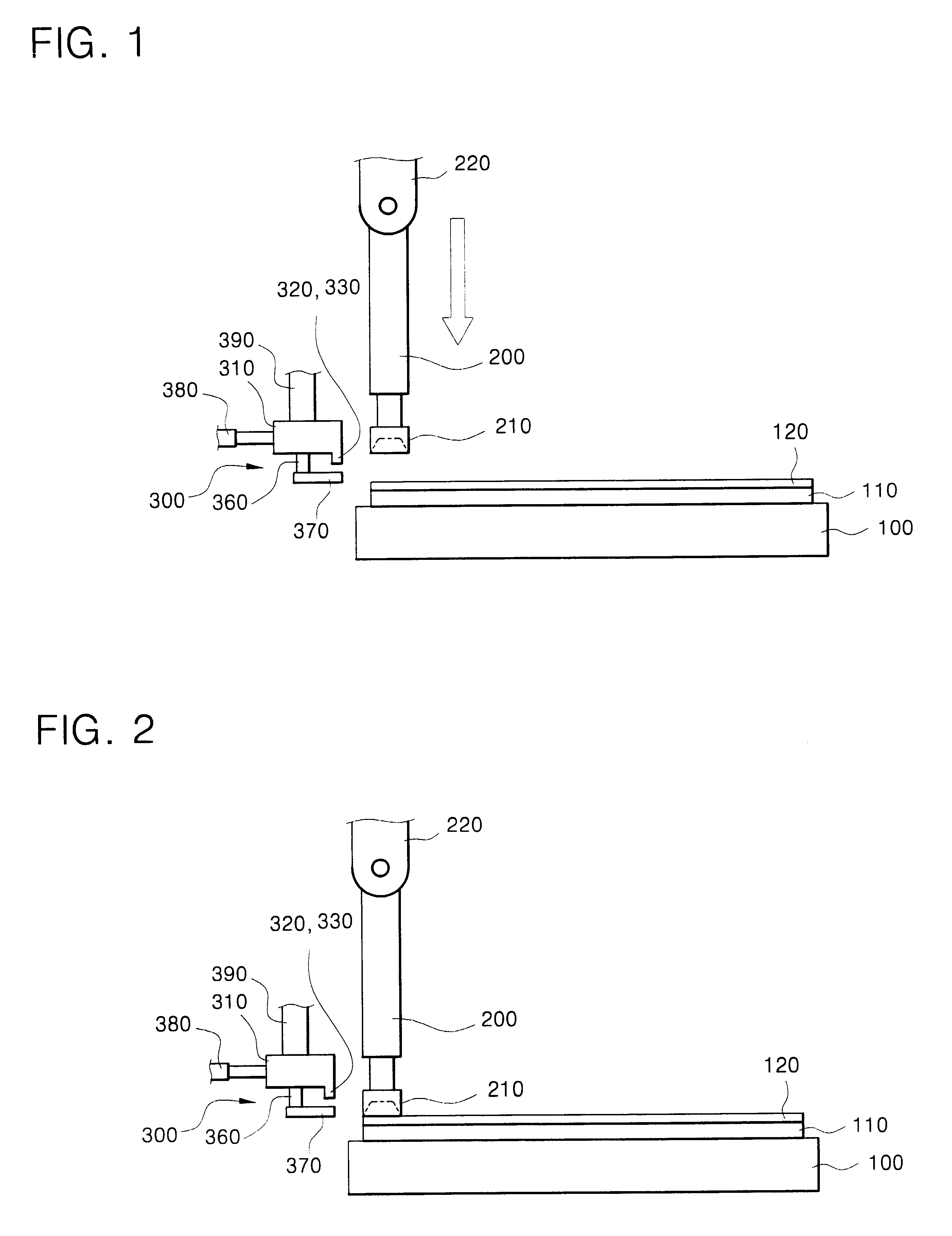

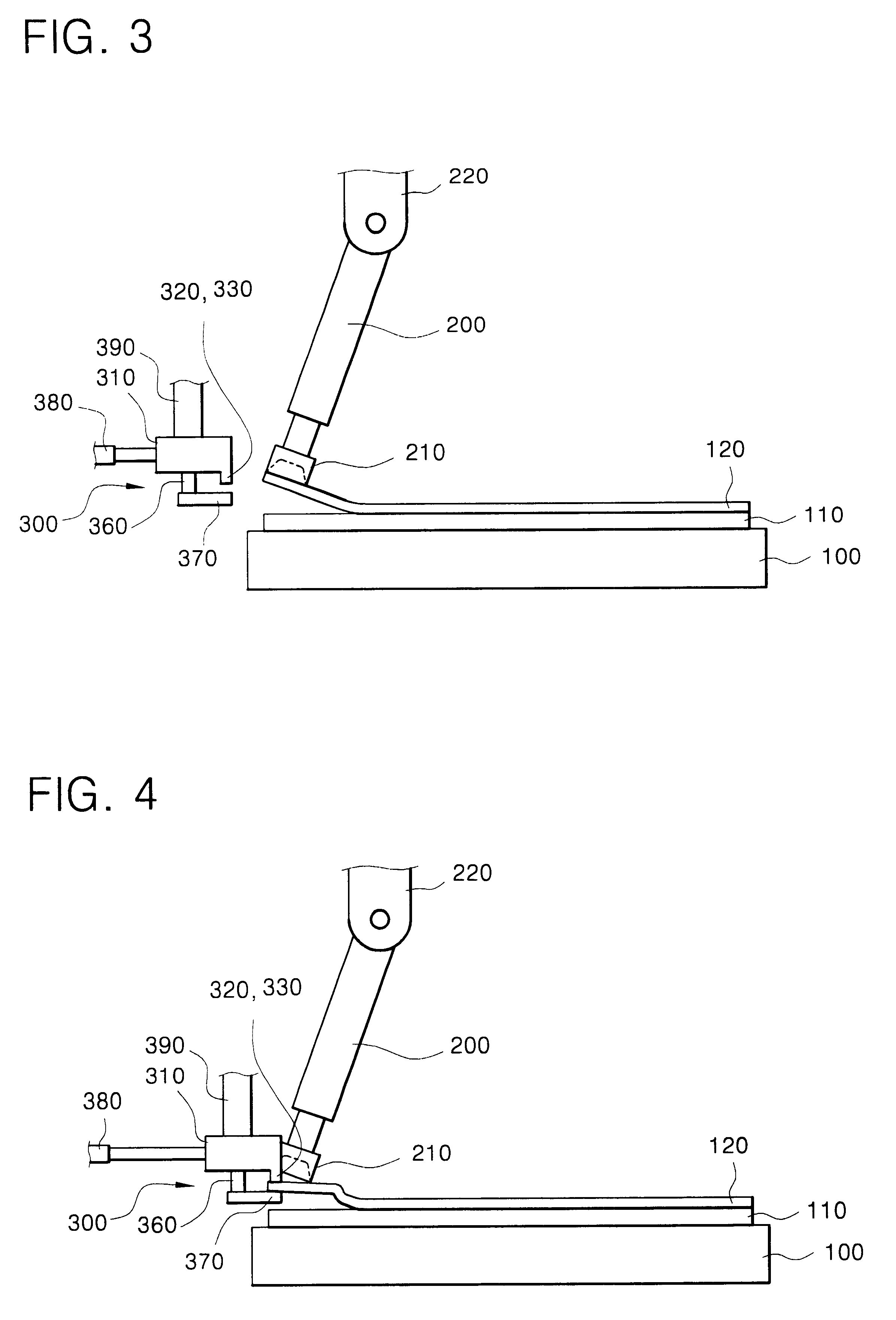

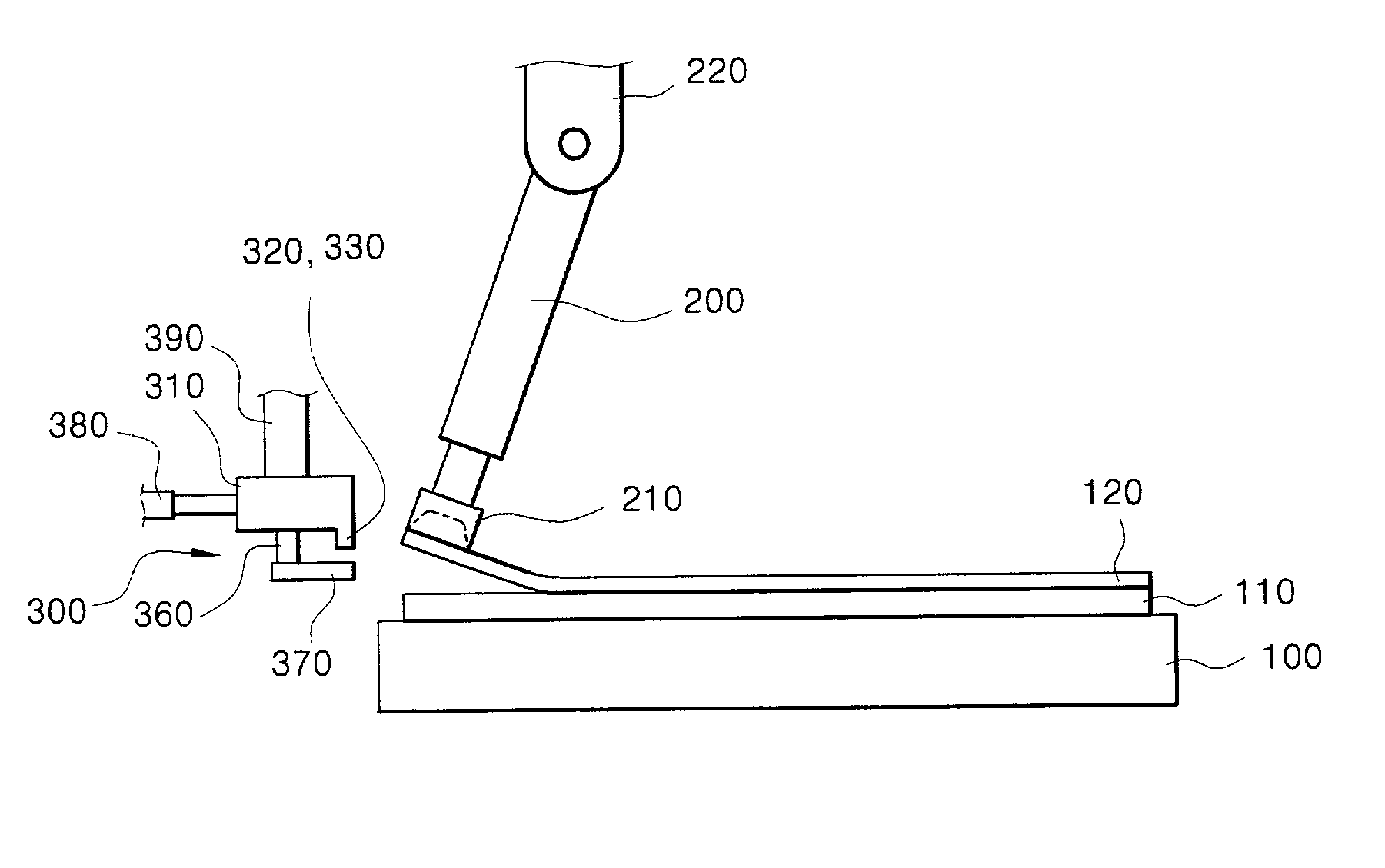

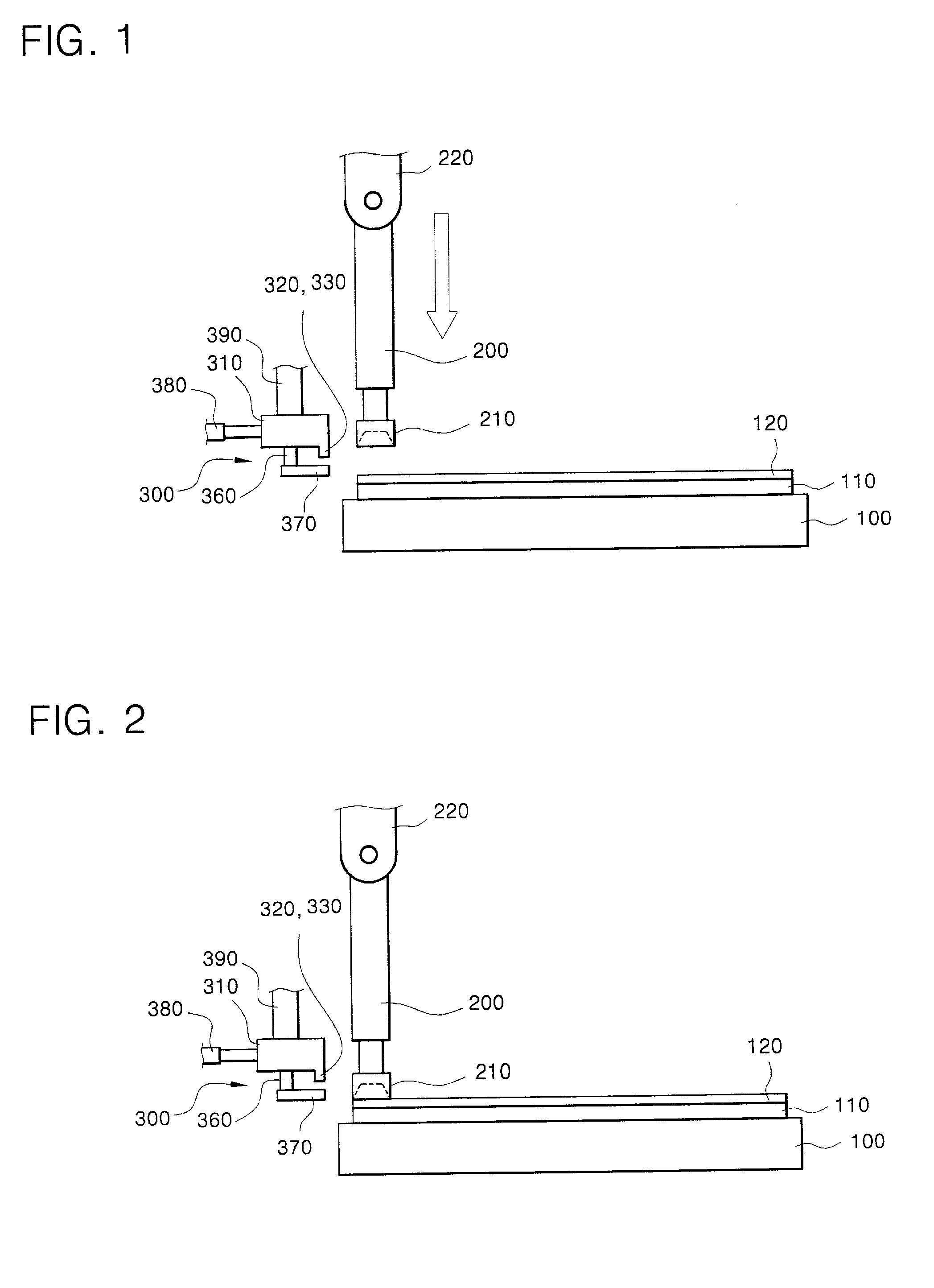

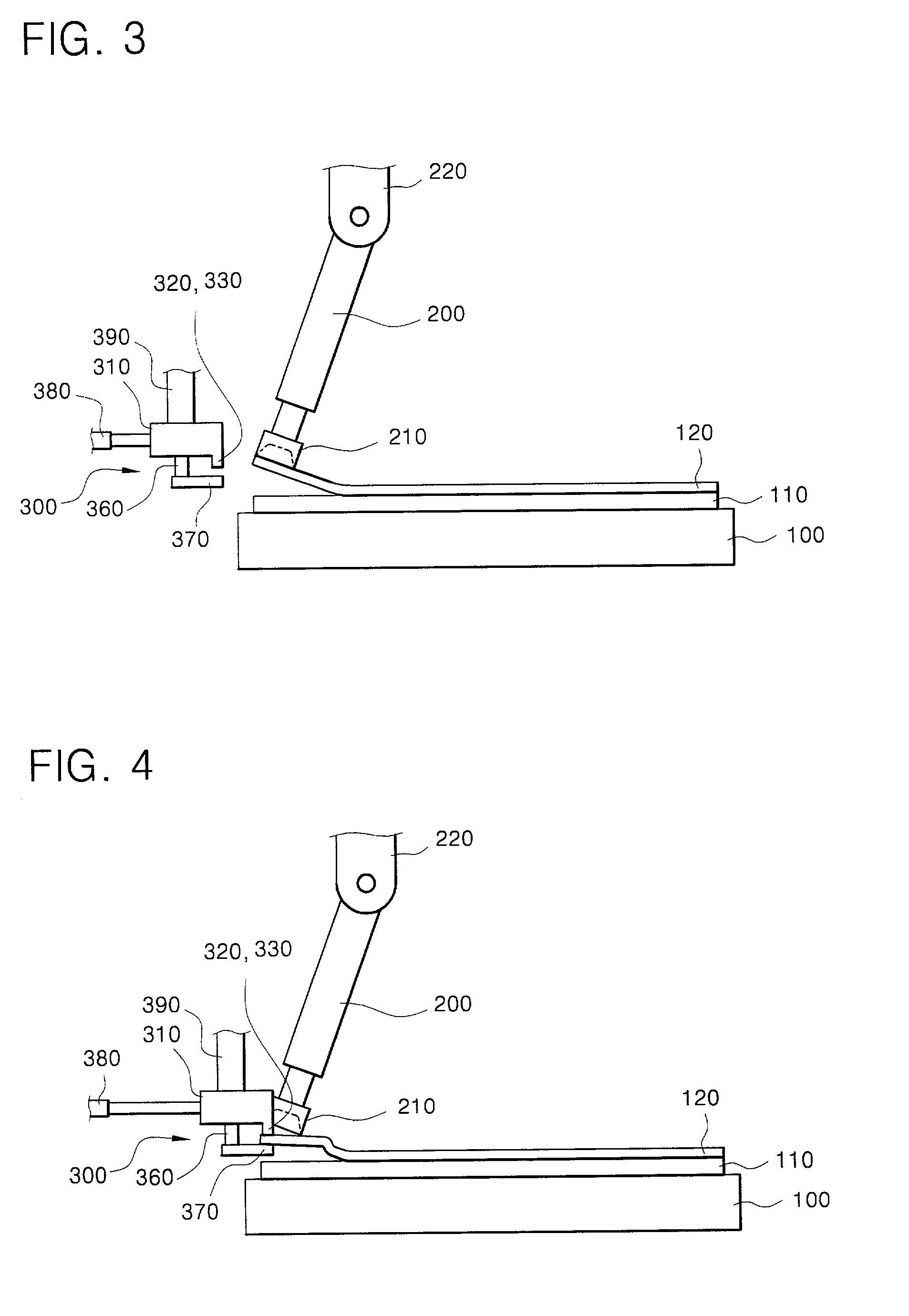

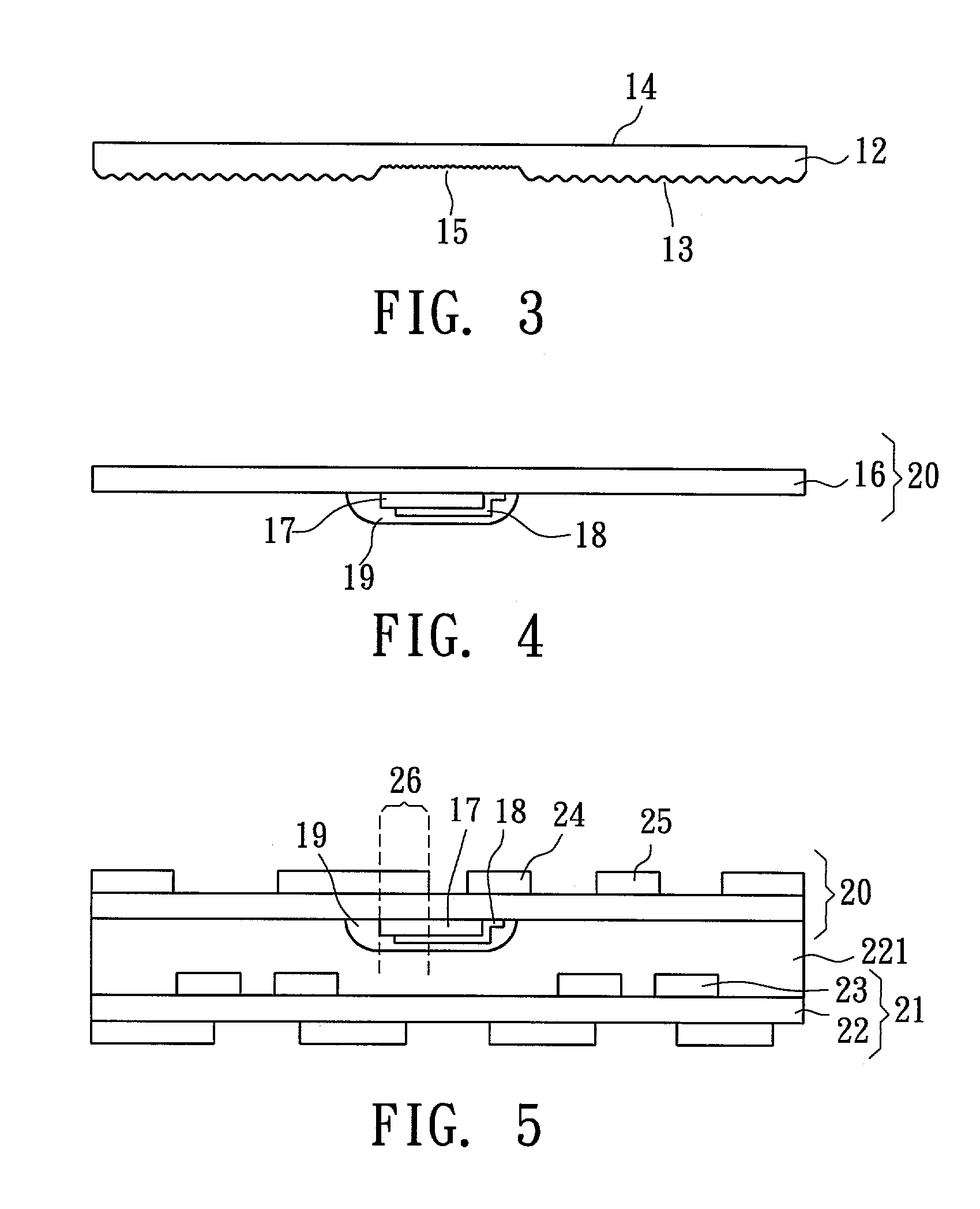

Protective film separator in semiconductor wafer grinding process

InactiveUS6503130B2Polishing machinesRevolution surface grinding machinesTectorial membraneEngineering

A protective film separator comprising an adsorption means and a peeling means for removing the protective film in a semiconductor wafer backside grinding process. The adsorption means uses a vacuum to separate a part of a protective film adhered to an electrical circuit patterned side of a wafer from the patterned side of the wafer. The peeling means presses each side of the part of the protective film separated from the wafer by the adsorption means, and separates unpeeled parts thereof from the patterned side of the wafer.The protective film separator of the present invention reduces costs and expenses for raw materials by eliminating the need for extra removing tape or heat-activated adhesive tape. The present invention may also improve semiconductor yields by reducing the external force applied to a wafer during removal of the protective film, thereby allowing better protection from impurities.

Owner:SAMSUNG ELECTRONICS CO LTD

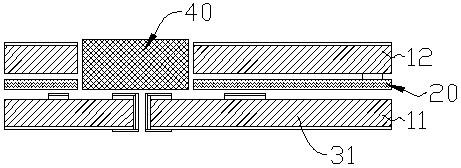

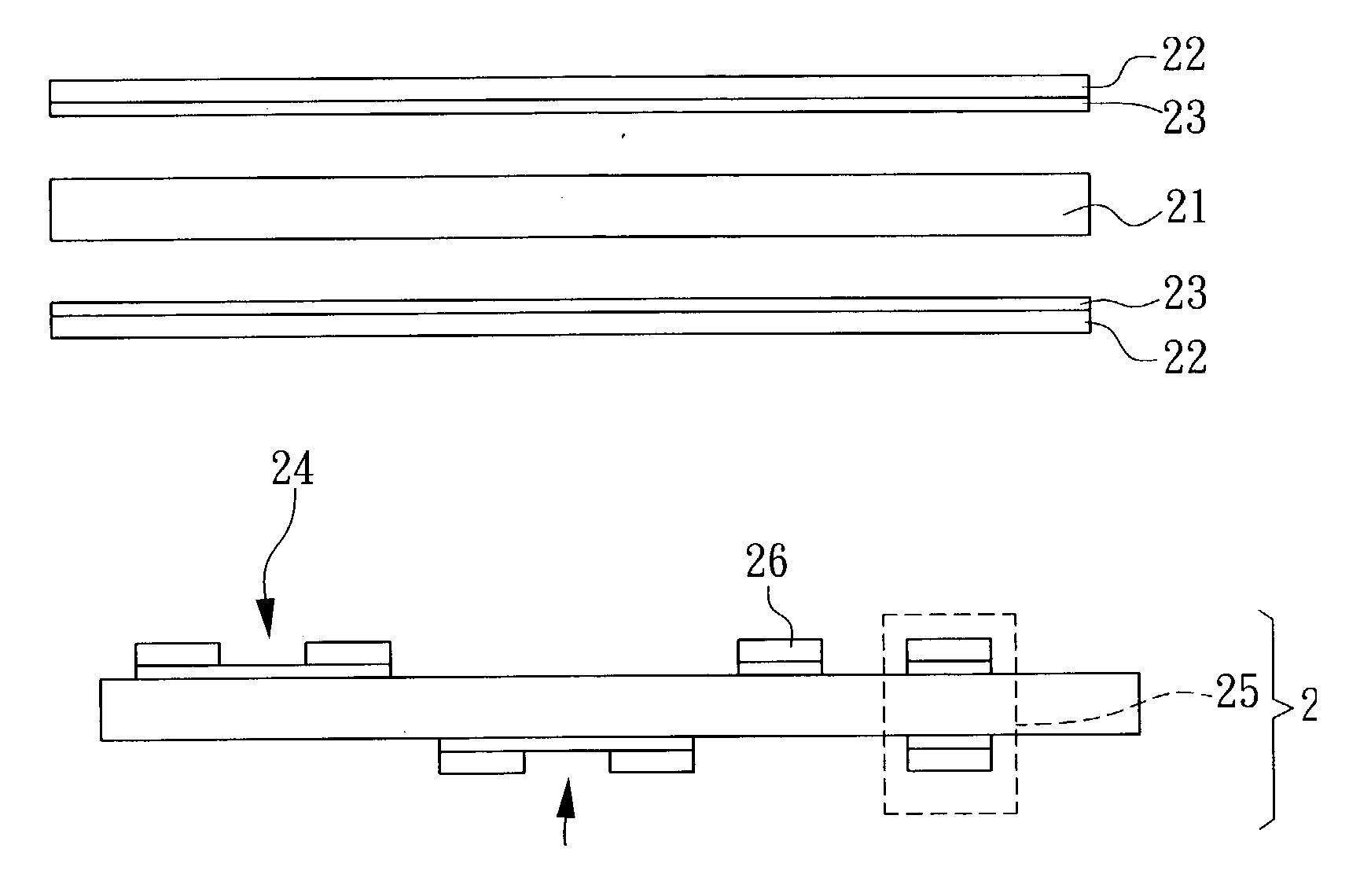

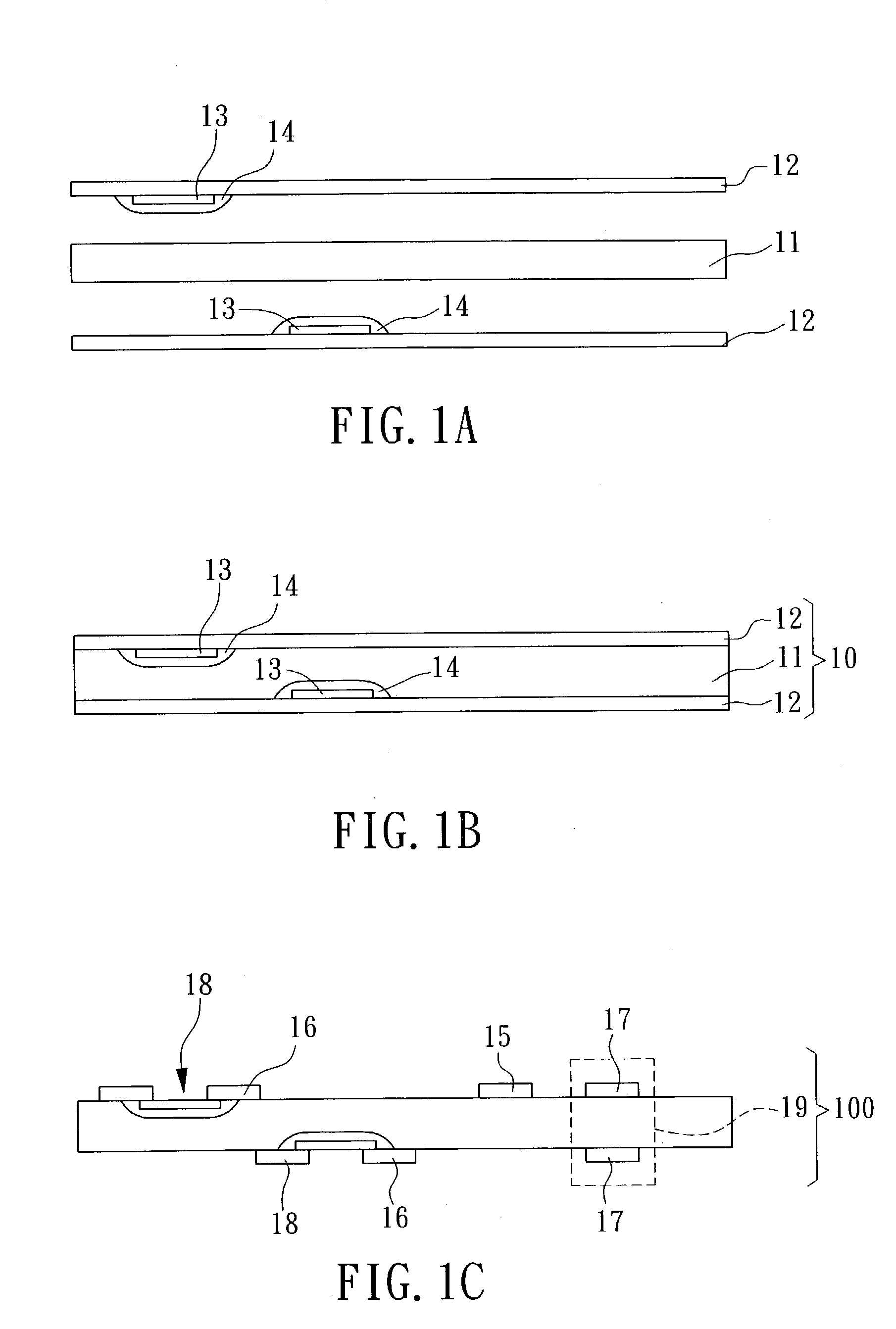

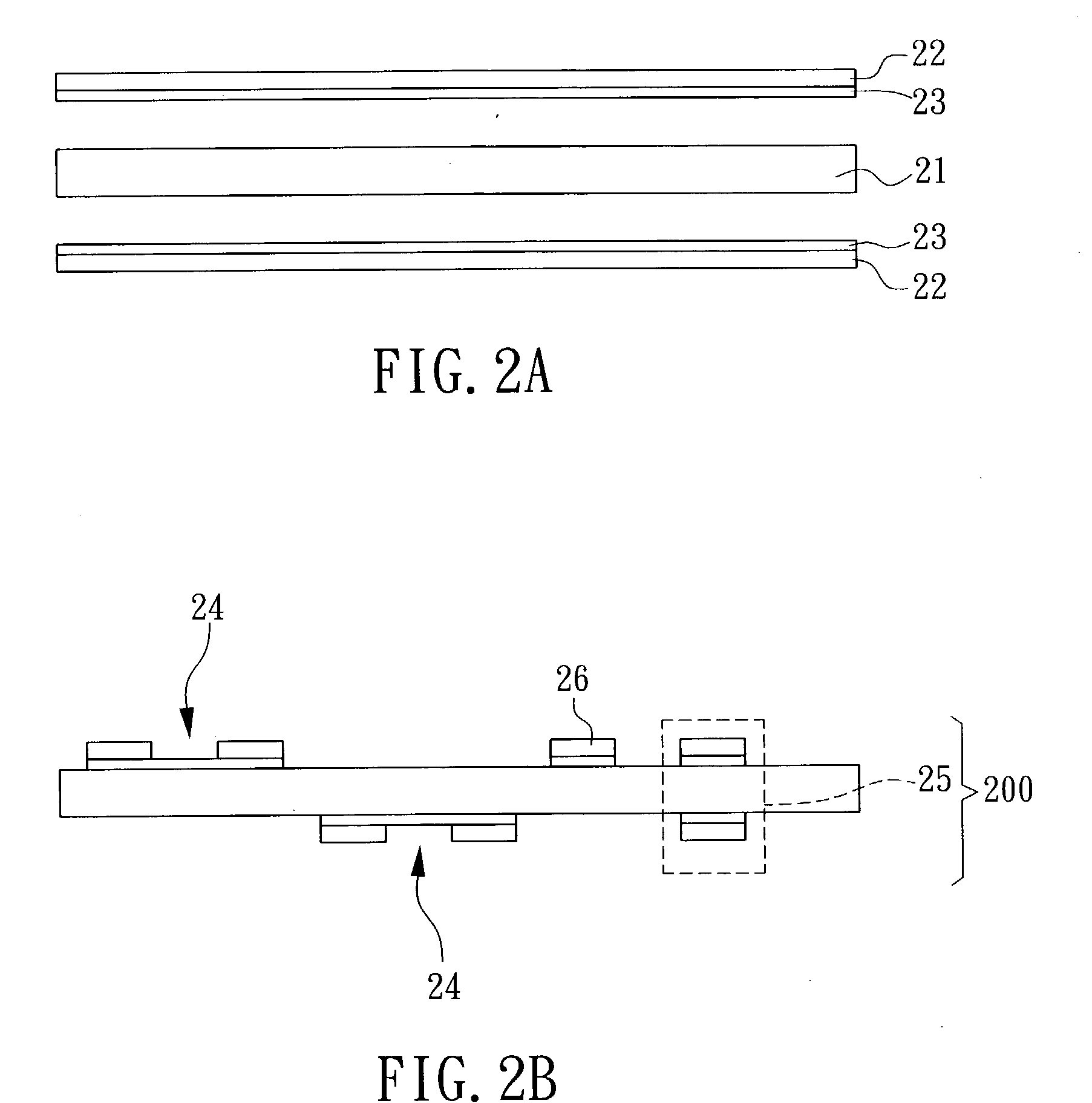

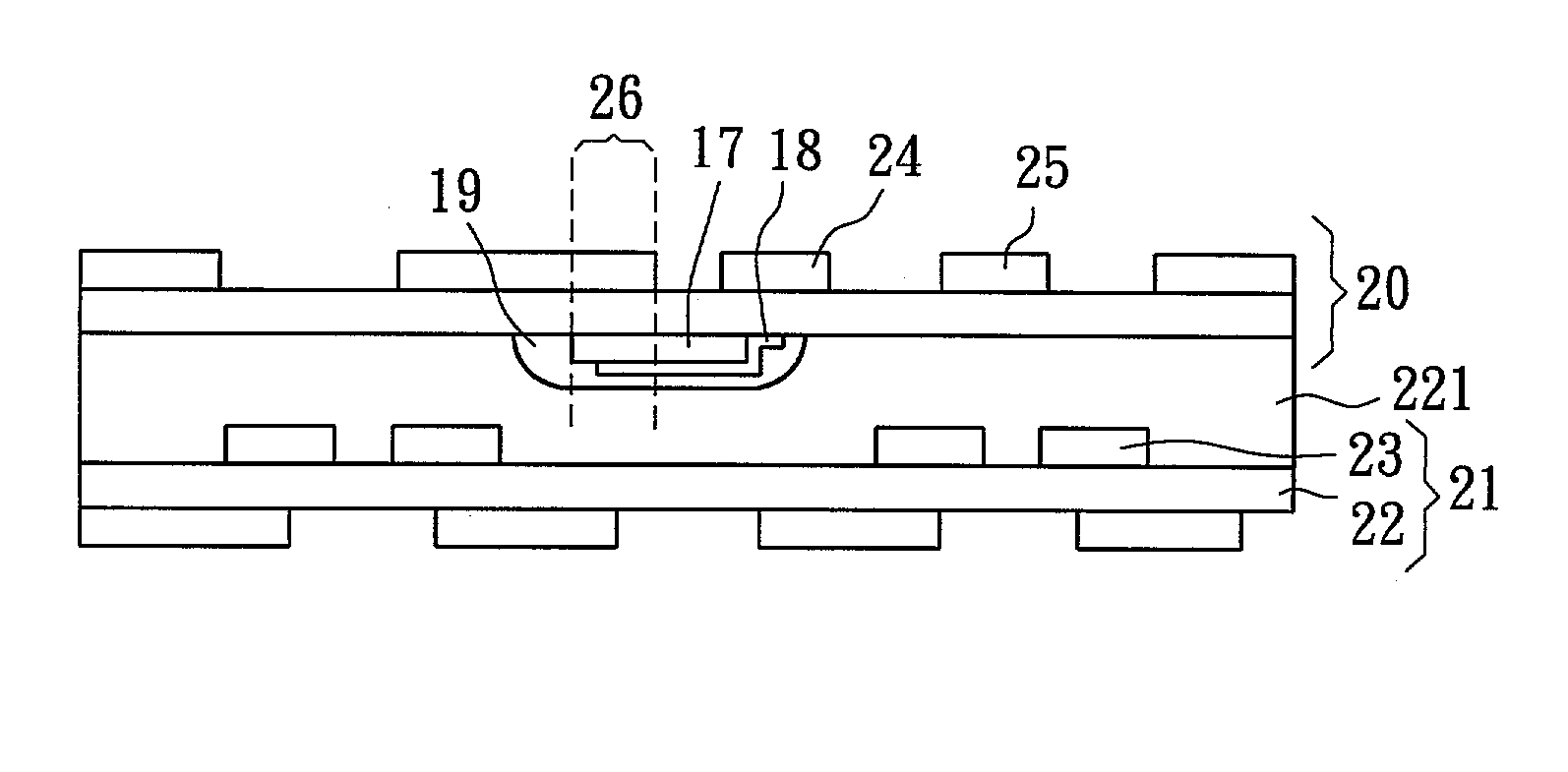

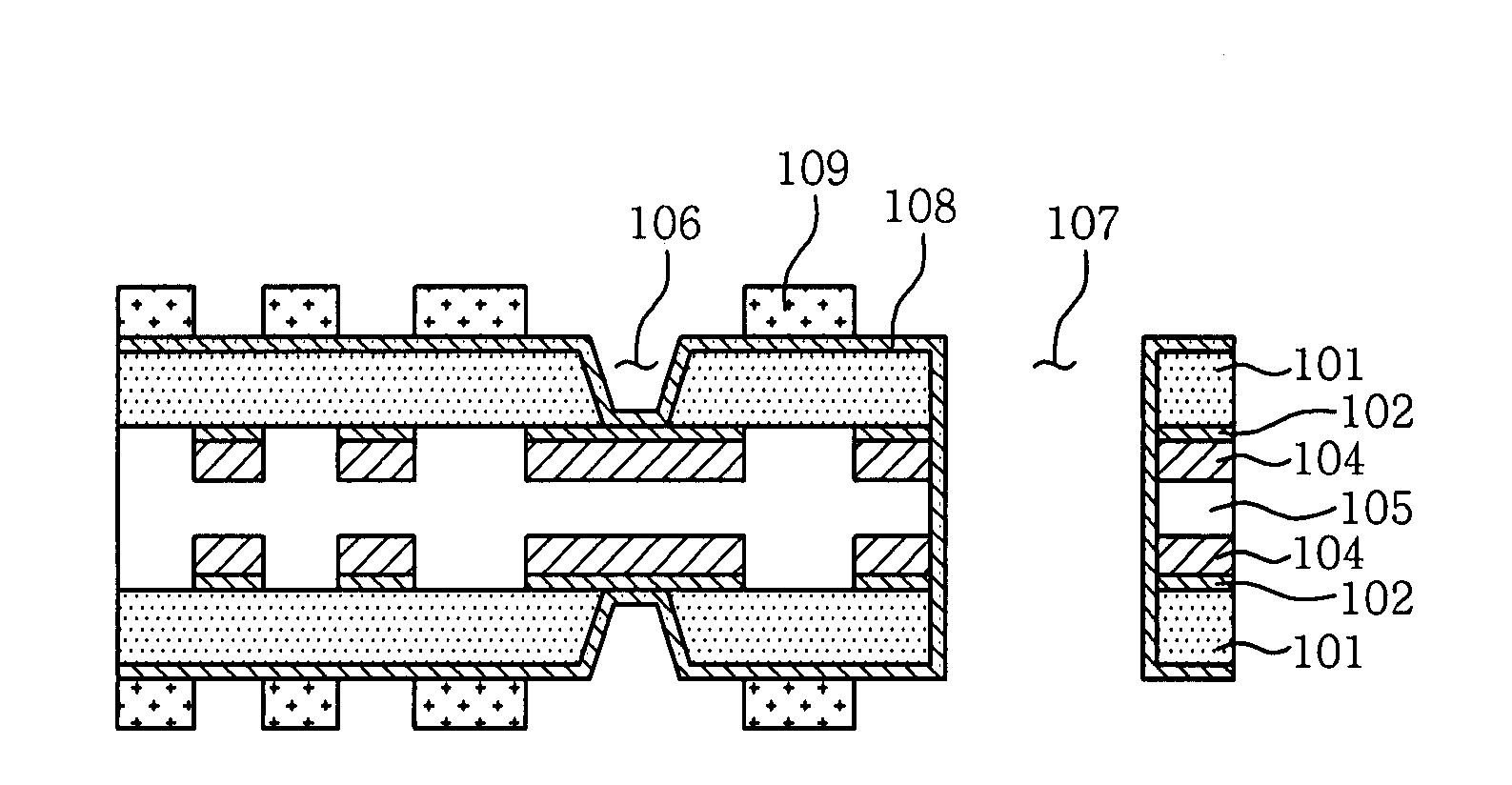

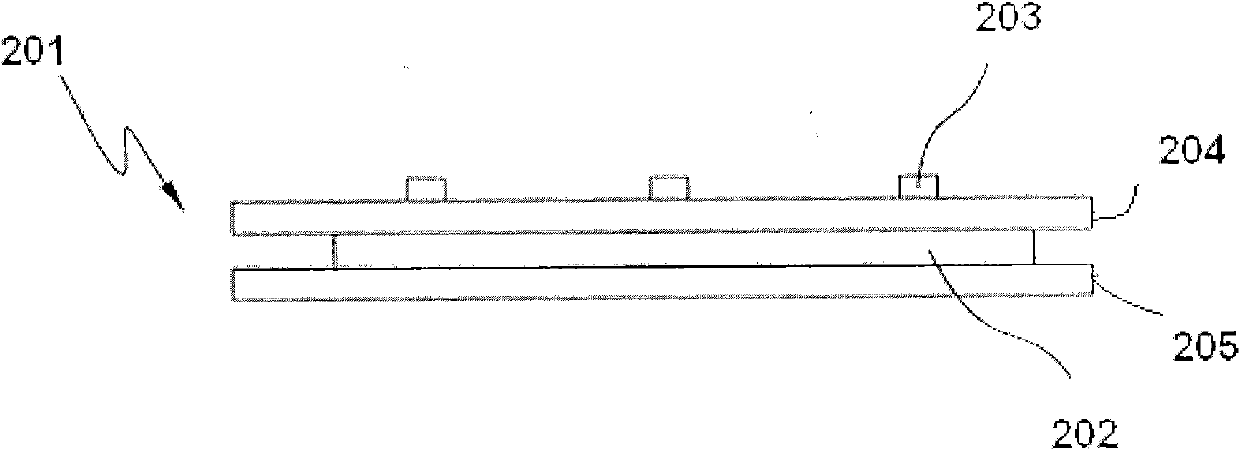

Carrier member for transmitting circuits, coreless printed circuit board using the carrier member, and method of manufacturing the same

InactiveUS20080264684A1Improve reliabilityPrinted circuit aspectsConductive pattern formationHigh densityEngineering

Disclosed herein is a carrier member for transmitting circuits, which is a component of a coreless printed circuit board having circuit patterns embedded therein, and which can be used to provide a high-density and highly reliable printed circuit board by forming protrusions only on the lower ends of the circuit patterns, a coreless printed circuit board using the carrier member, and methods of manufacturing the carrier member and the coreless printed circuit board.

Owner:SAMSUNG ELECTRO MECHANICS CO LTD

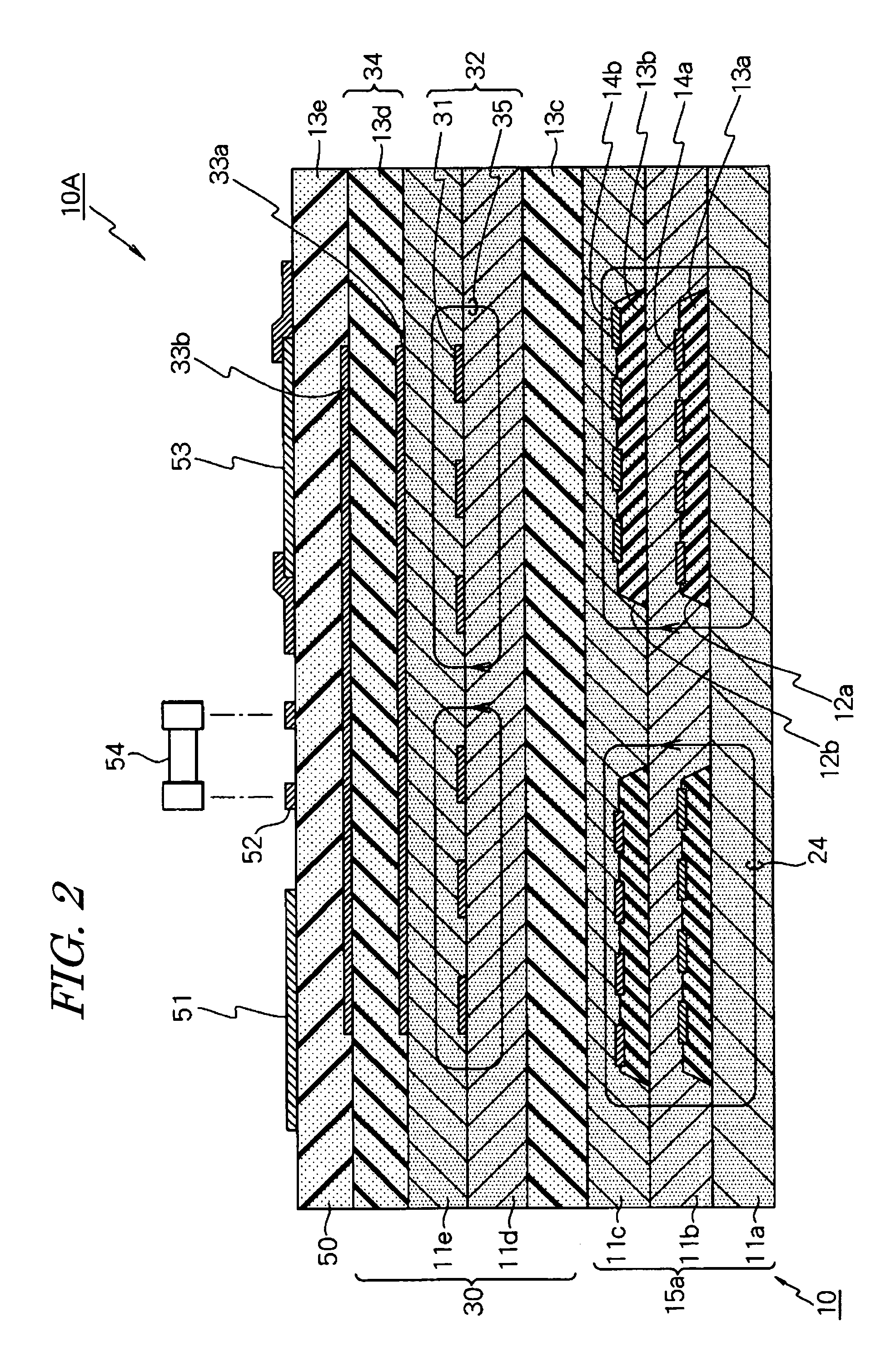

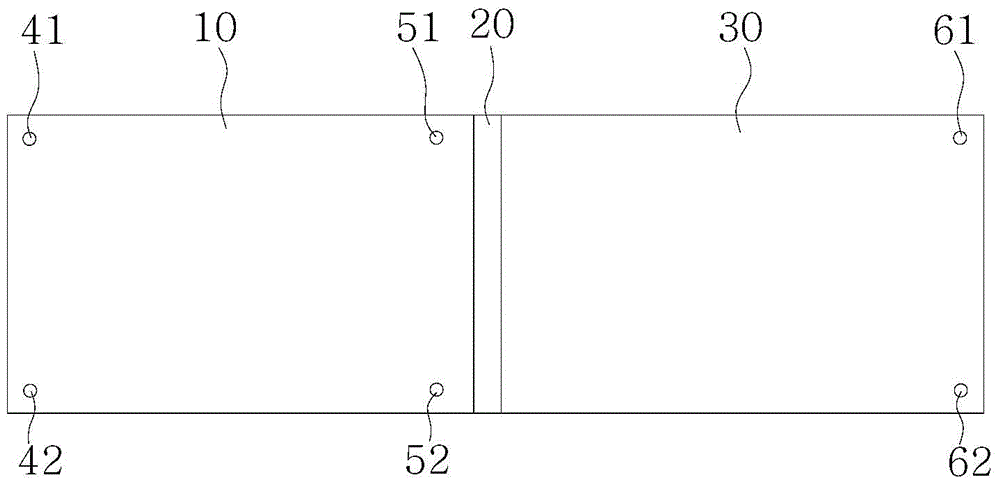

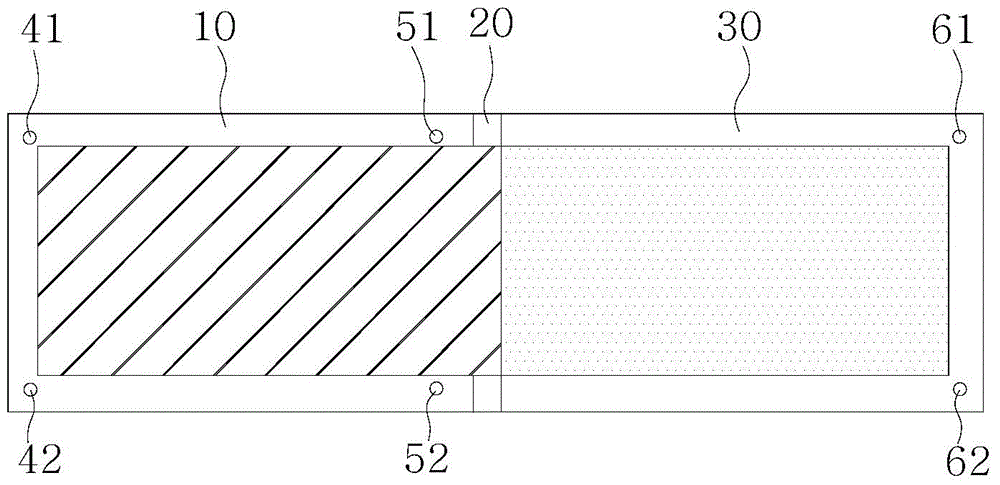

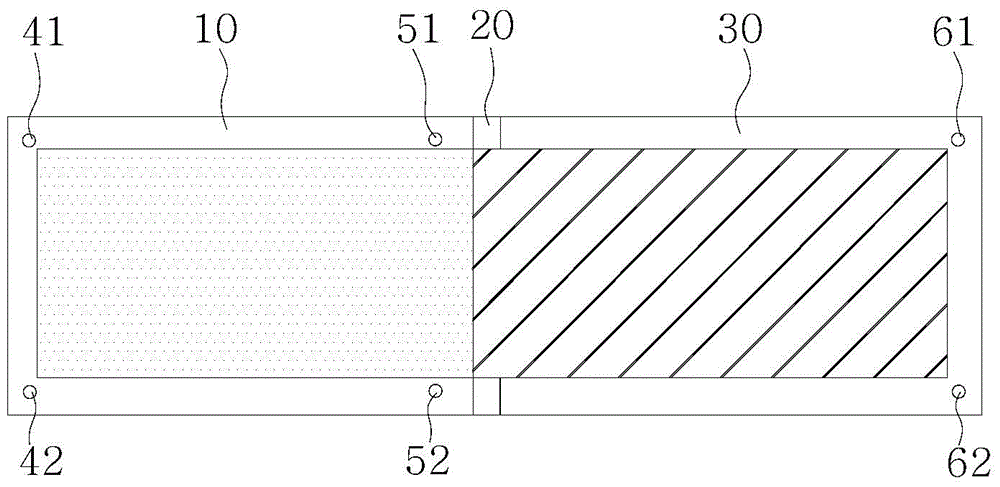

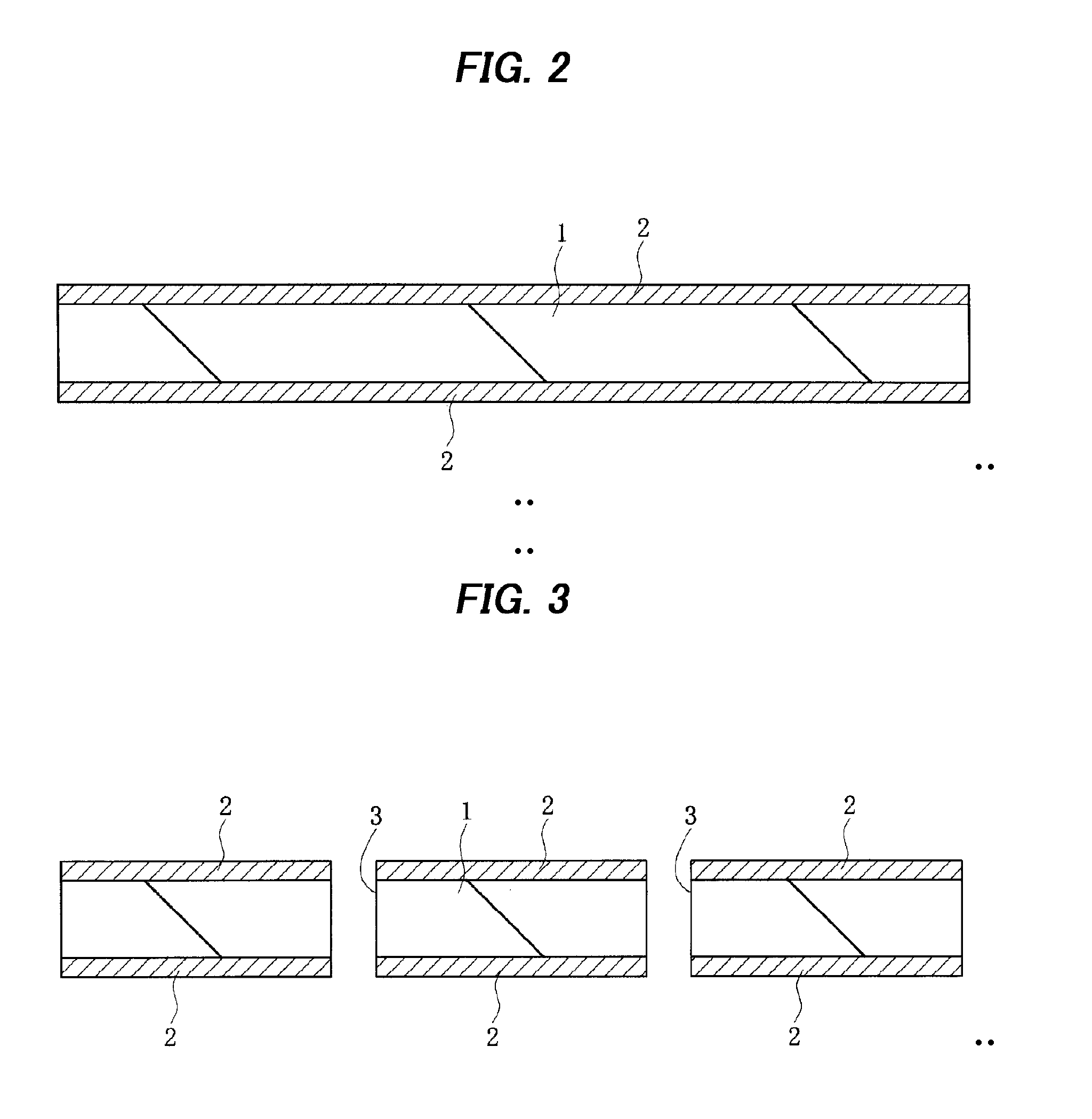

Multi-layer circuit board

InactiveUS6194668B1Semiconductor/solid-state device detailsPrinted circuit aspectsDiagonalOblique line

Owner:SHINKO ELECTRIC IND CO LTD

Manufacturing method of high-order multistage HDI (High Density Interconnection) printed circuit board

ActiveCN103179812AEnsure stacking accuracyEnsure alignment accuracy matchingMultilayer circuit manufactureGraphicsHigh density

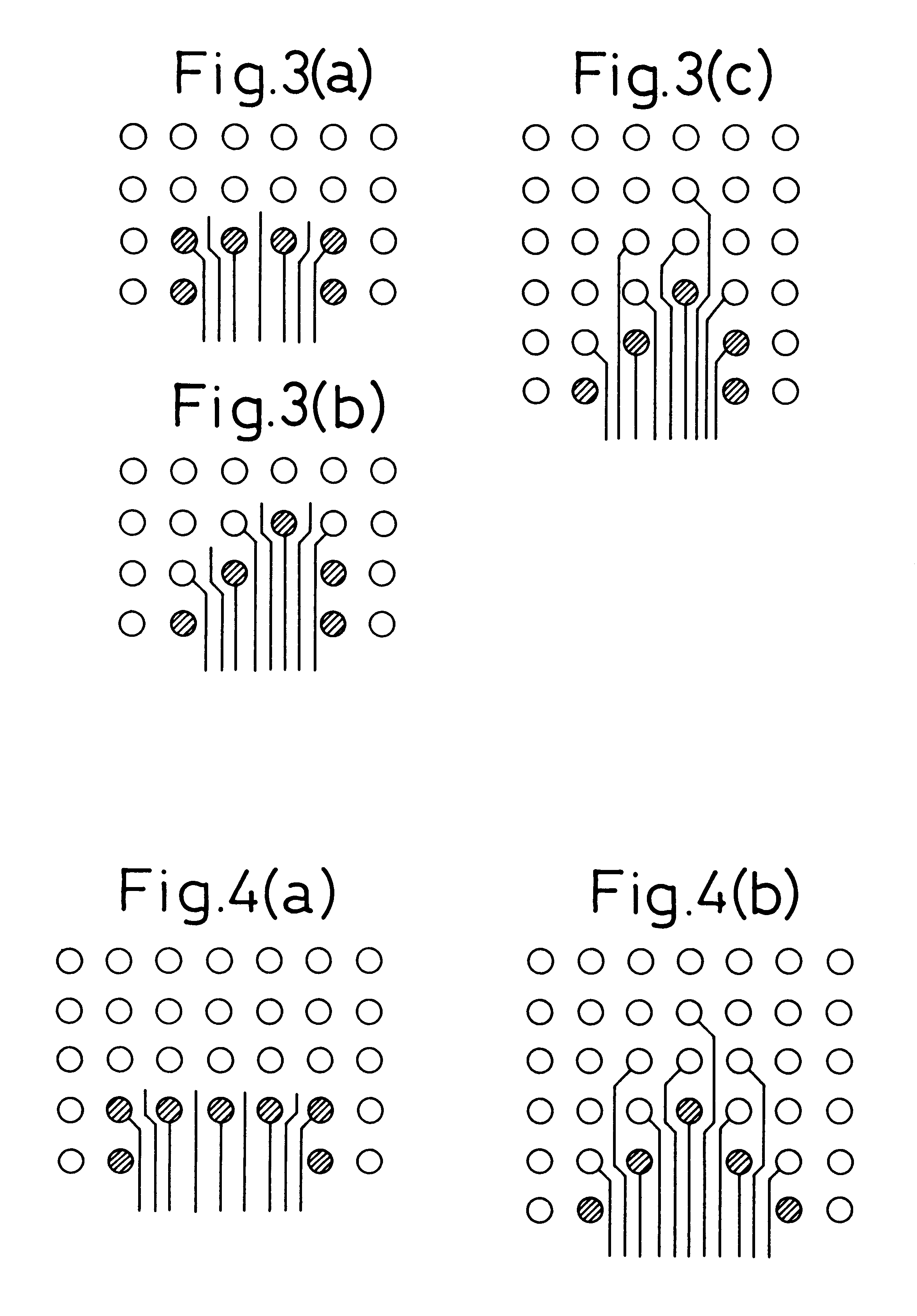

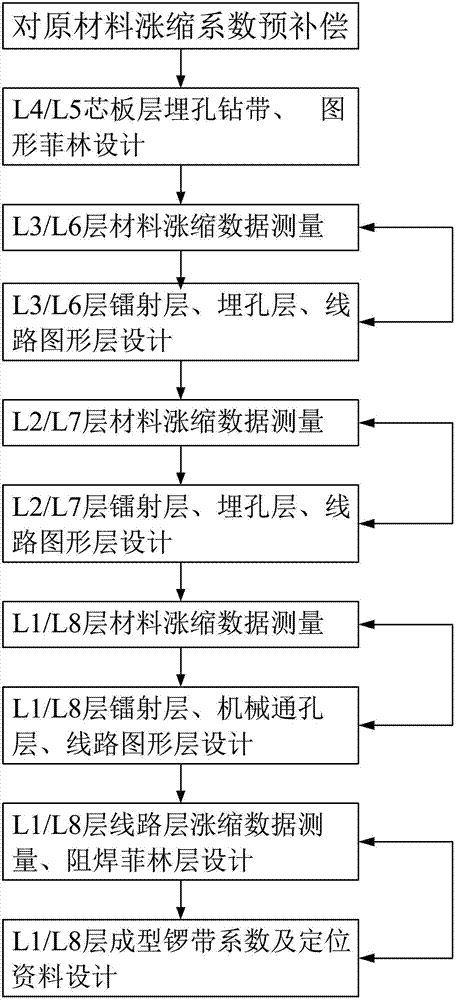

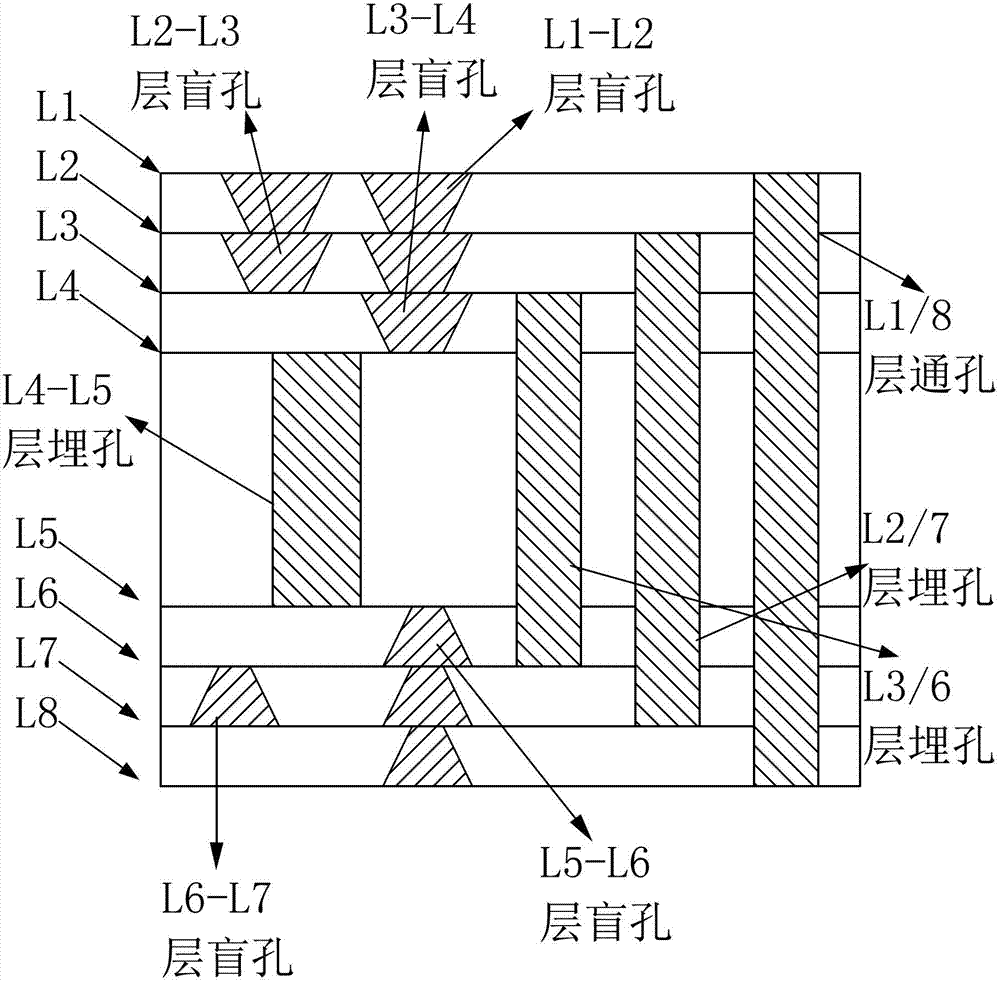

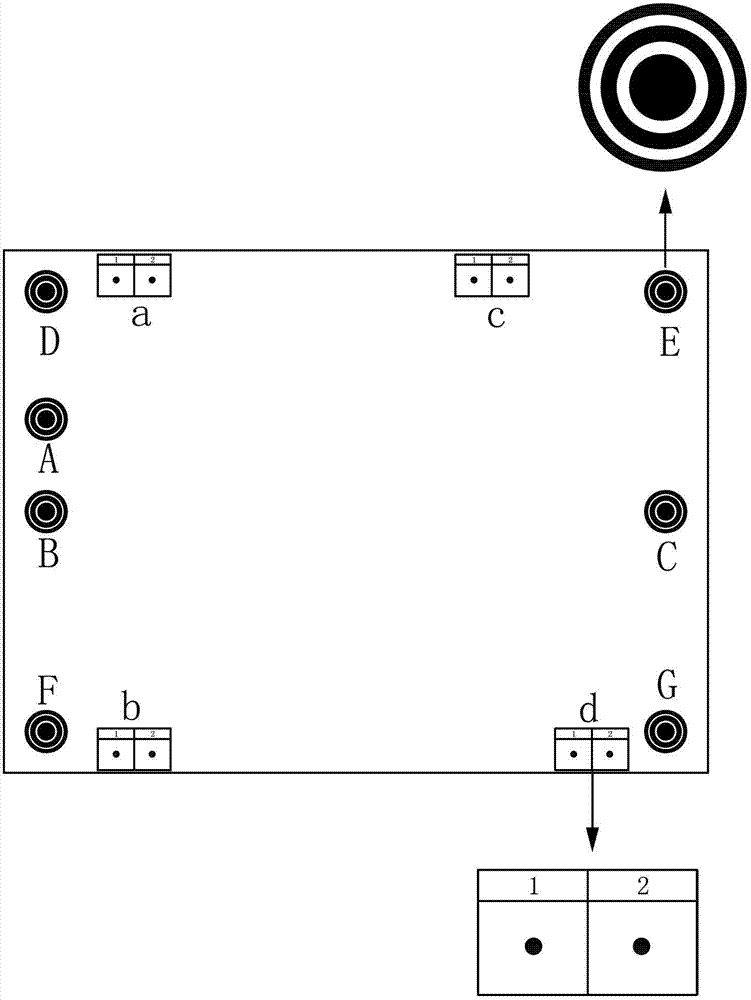

The invention discloses a manufacturing method of a high-order multistage HDI (High Density Interconnection) printed circuit board. An expansion coefficient of a cross-band veneer is pre-compensated according to a layer number, a dead hole stacking number and an engineering pre-designed lamination structure of a product, a press frequency and a material characteristic; a reference target coordinate, a shape, a size, a process aligning manner and the like are aligned for design demands for systematizing different graph levels and production positioning reference points, so that the alignment matching index and the expansion alignment precision among different levels and different components can be achieved; all the alignment problems caused by various factors in a production process of a three-stage HDI printing circuit can be considered; the alignment problems among a series of important PCB (Printed Circuit Board) processes, such as an inner layer graph, a secondary outer layer circuit, a secondary outer layer buried hole, an outer layer circuit, a mechanical through hole, a radiation dead hole and solder resistance of a one-stage HDI product, a two-stage HDI product and a three-stage HDI product, can be solved; and meanwhile, the hole overlapping precision of micro dead holes and the alignment precision matching indexes of the dead holes, the through hole and a circuit graph can be ensured.

Owner:MEIZHOU ZHIHAO ELECTRONICS TECH

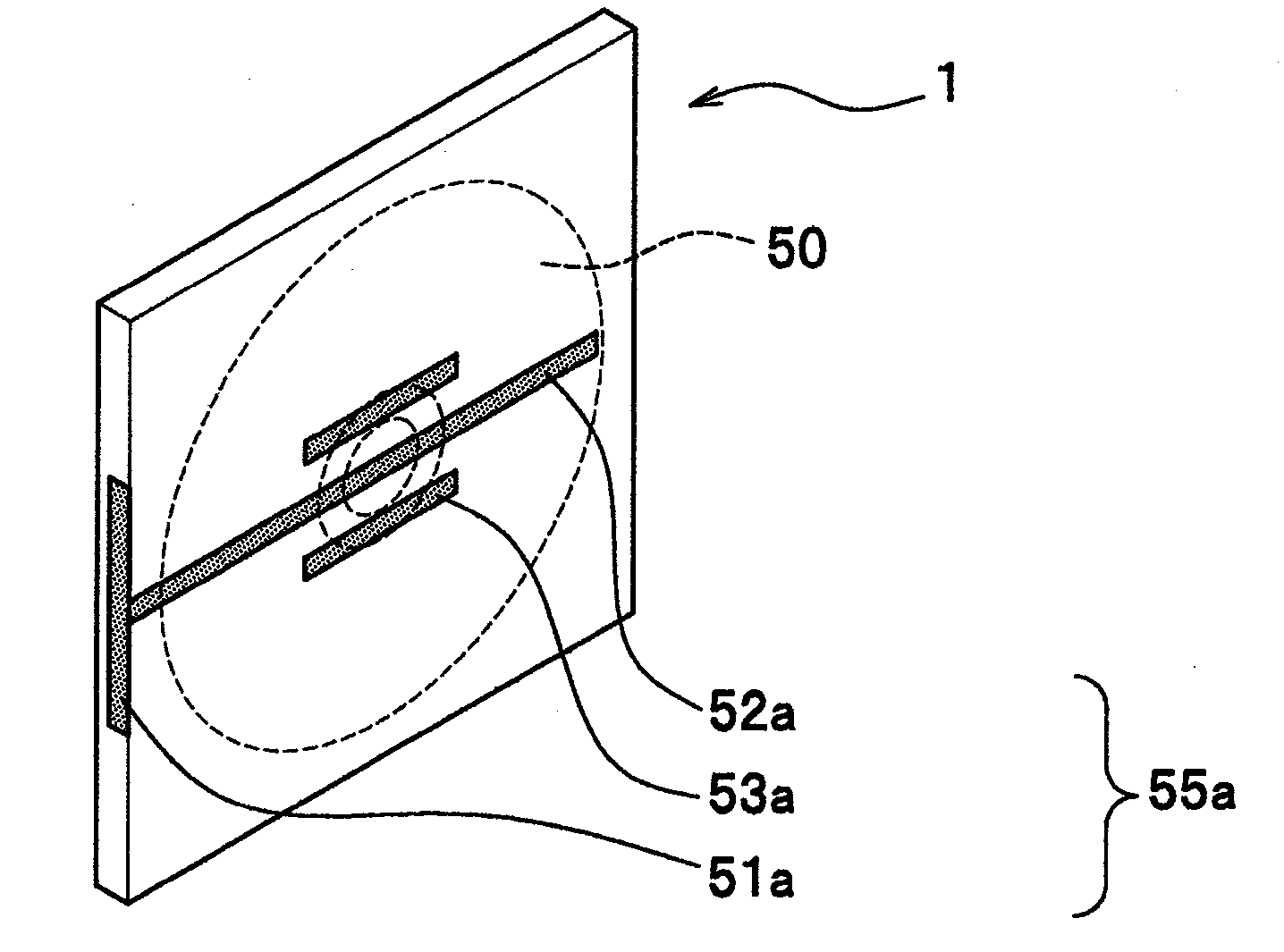

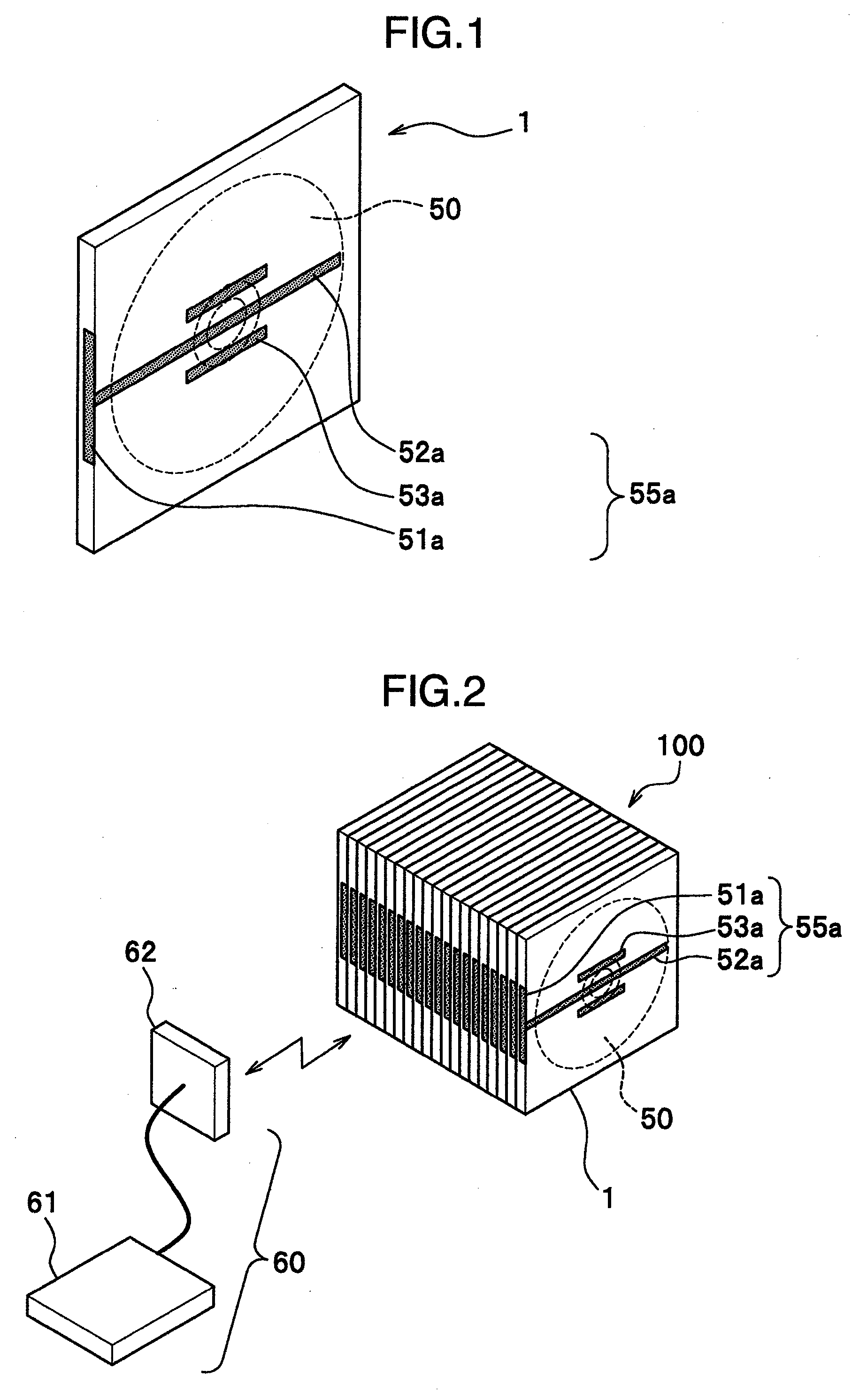

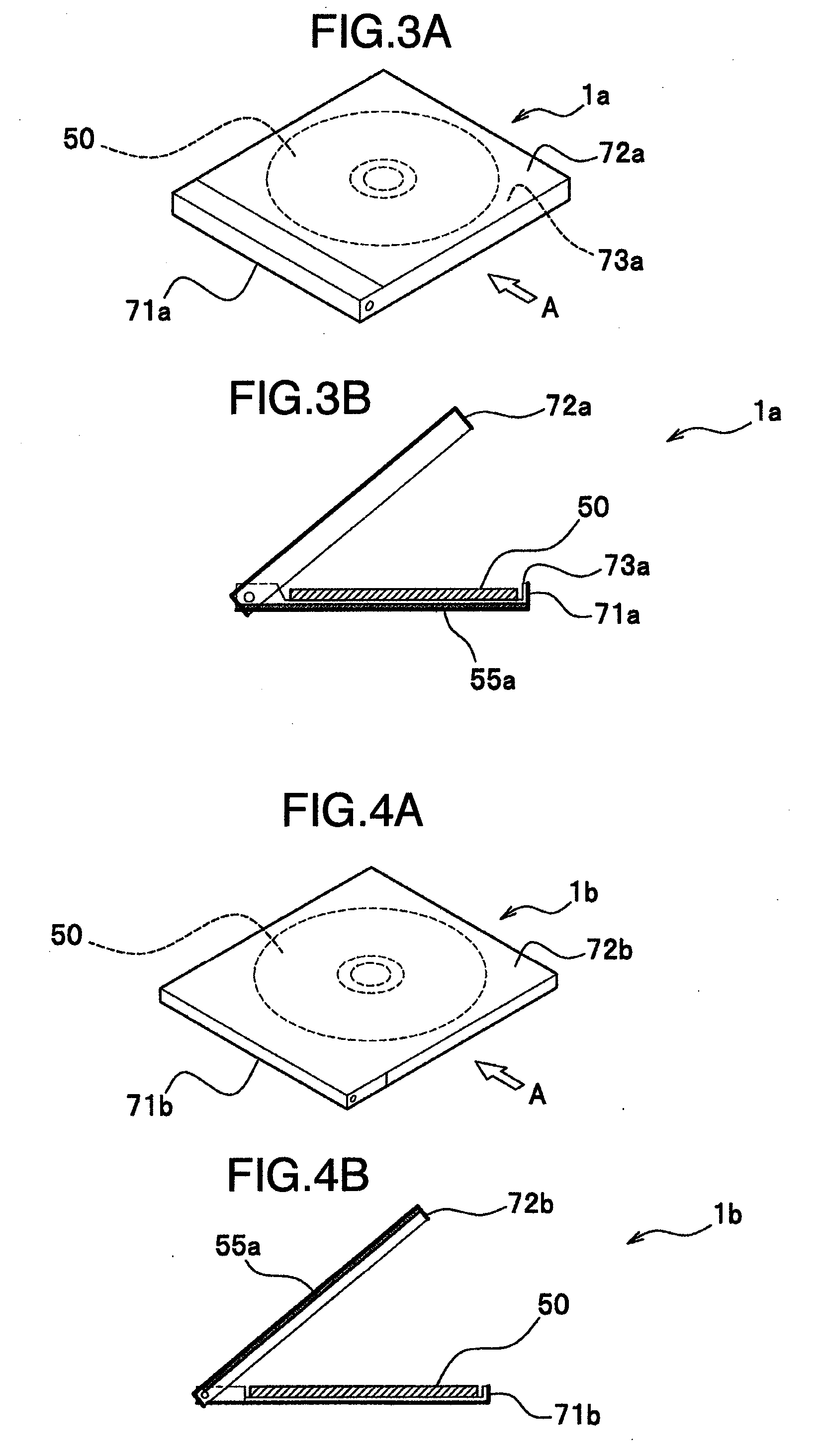

Media case and circuit pattern sheet

InactiveUS20080246616A1Simple configurationHighly dense collectionAccessories for auxillary signalsAntenna supports/mountingsResonanceEngineering

A media case and a circuit pattern sheet with a simple configuration is provided that allows highly dense collection and reliable recognition of housed disk media.The media case 1 can house disk media 50 provided with an RFID tag (not illustrated in the drawing). This media case 1 includes an antenna element 51a being formed on its back plane to exchange an electromagnetic wave signal with the outside of the media case 1; a waveguide line 52a formed in the vicinity of its center therethrough along the disk media 50 from the antenna element 51a to guide high-frequency signals representing the electromagnetic wave signals to the antenna element 51a; and a resonance element 53a being formed adjacent to this waveguide line 52a and electromagnetically induced by the high-frequency signal.

Owner:HITACHI LTD

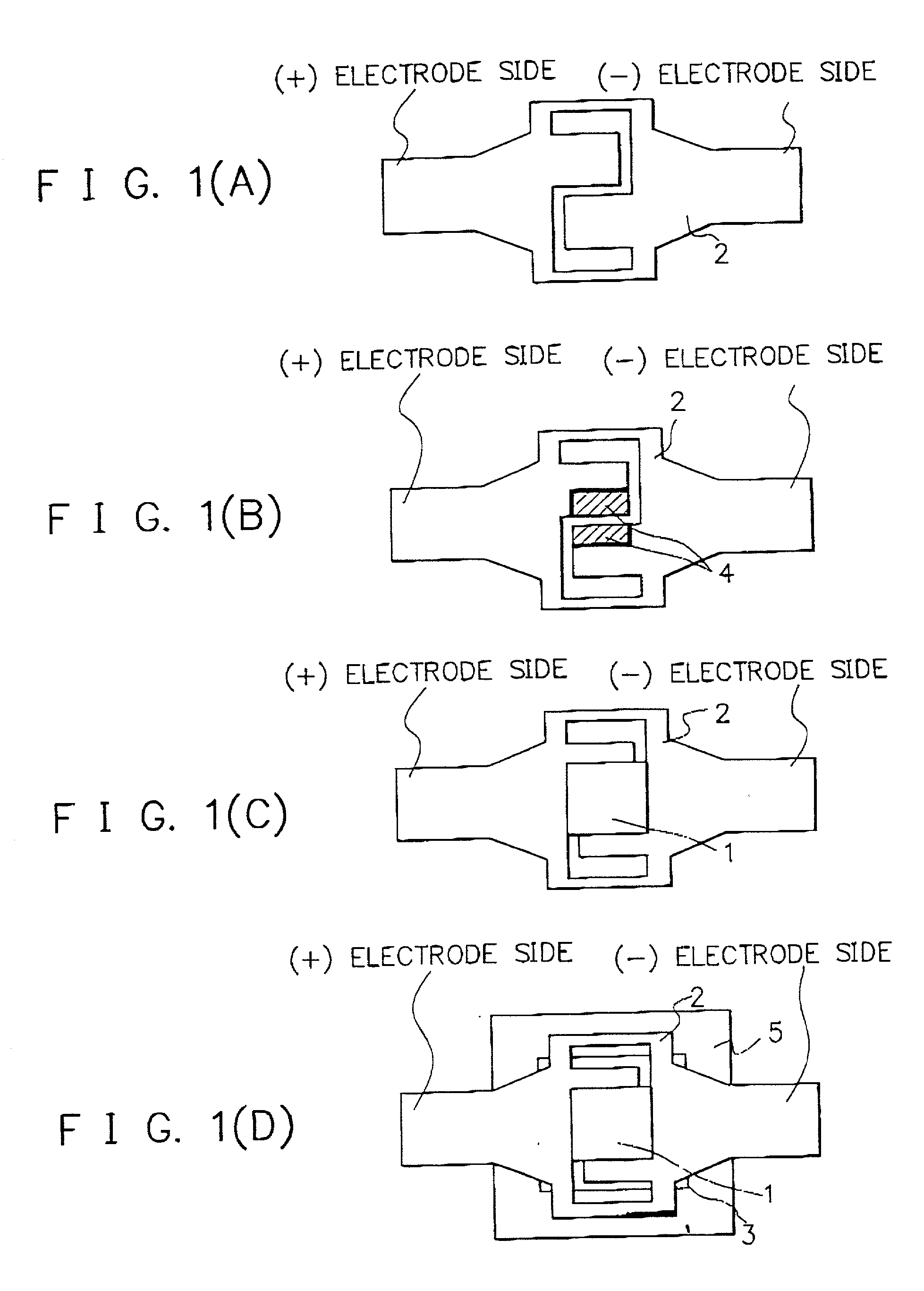

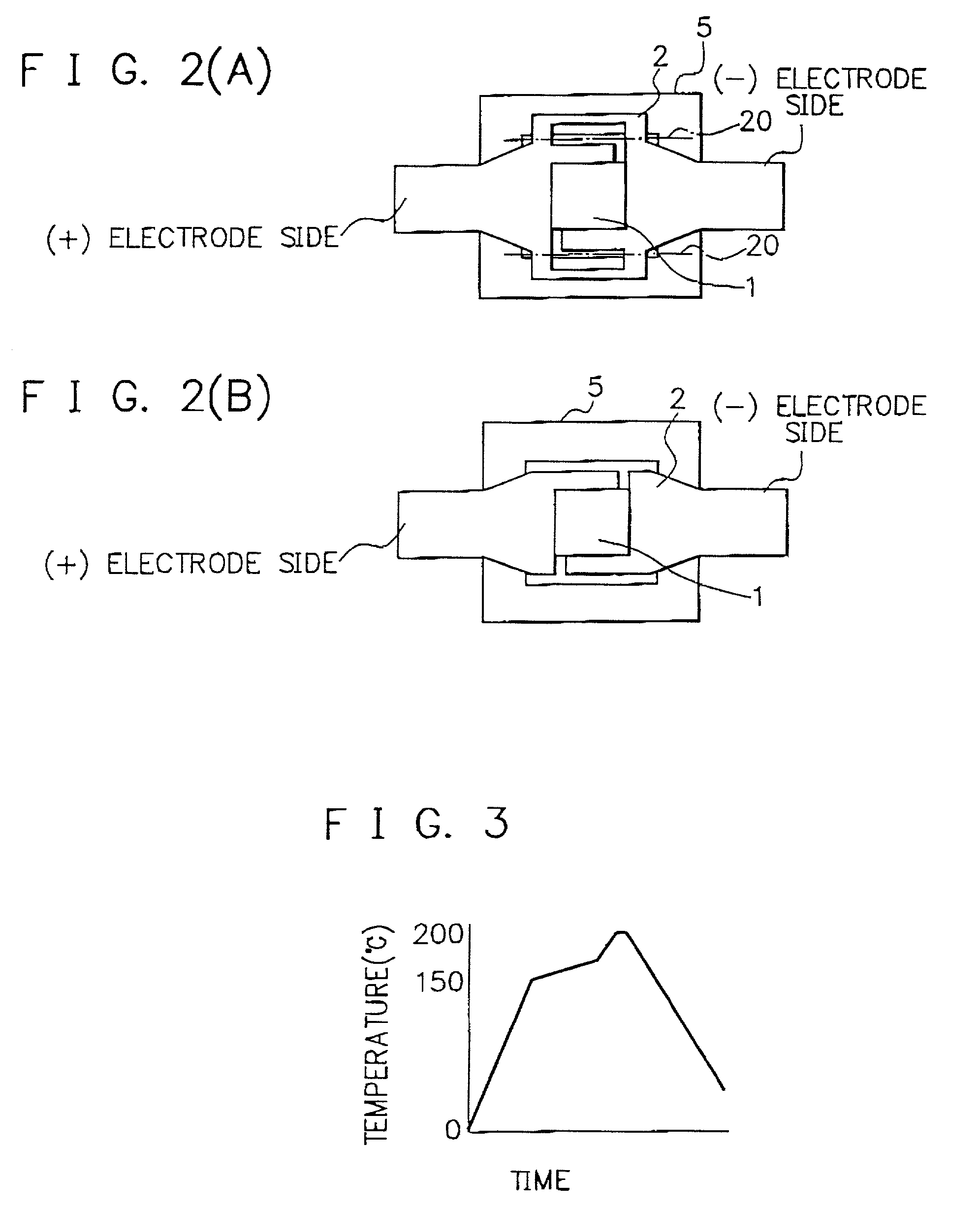

Mounting structure and mounting method of a photovoltaic element, mounting substrate for mounting a semiconductor element and method for mounting said semiconductor element on said mounting substrate

A mounting structure in which a photovoltaic element is mounted together with a metal body for outputting a power generated by said photovoltaic element to the outside, said photovoltaic element having a light receiving face and a non-light receiving face and having a pair of electrodes on said non-light receiving faces said metal body having a first surface and a second surface opposite said first surface, wherein said photovoltaic element is joined to said first surface of said metal body and an electrically insulative joining material is joined to said second surface of said metal body. A semiconductor element-mounting substrate for mounting a semiconductor element thereon, said mounting substrate comprising a retaining substrate having a circuit pattern for said semiconductor element, said circuit pattern having an electrode-joining portion for joining an electrode portion of said semiconductor element and an external terminal-fixing portion for fixing an external terminal and a groove being provided between said electrode-joining portion and said external terminal-fixing portion.

Owner:CANON KK

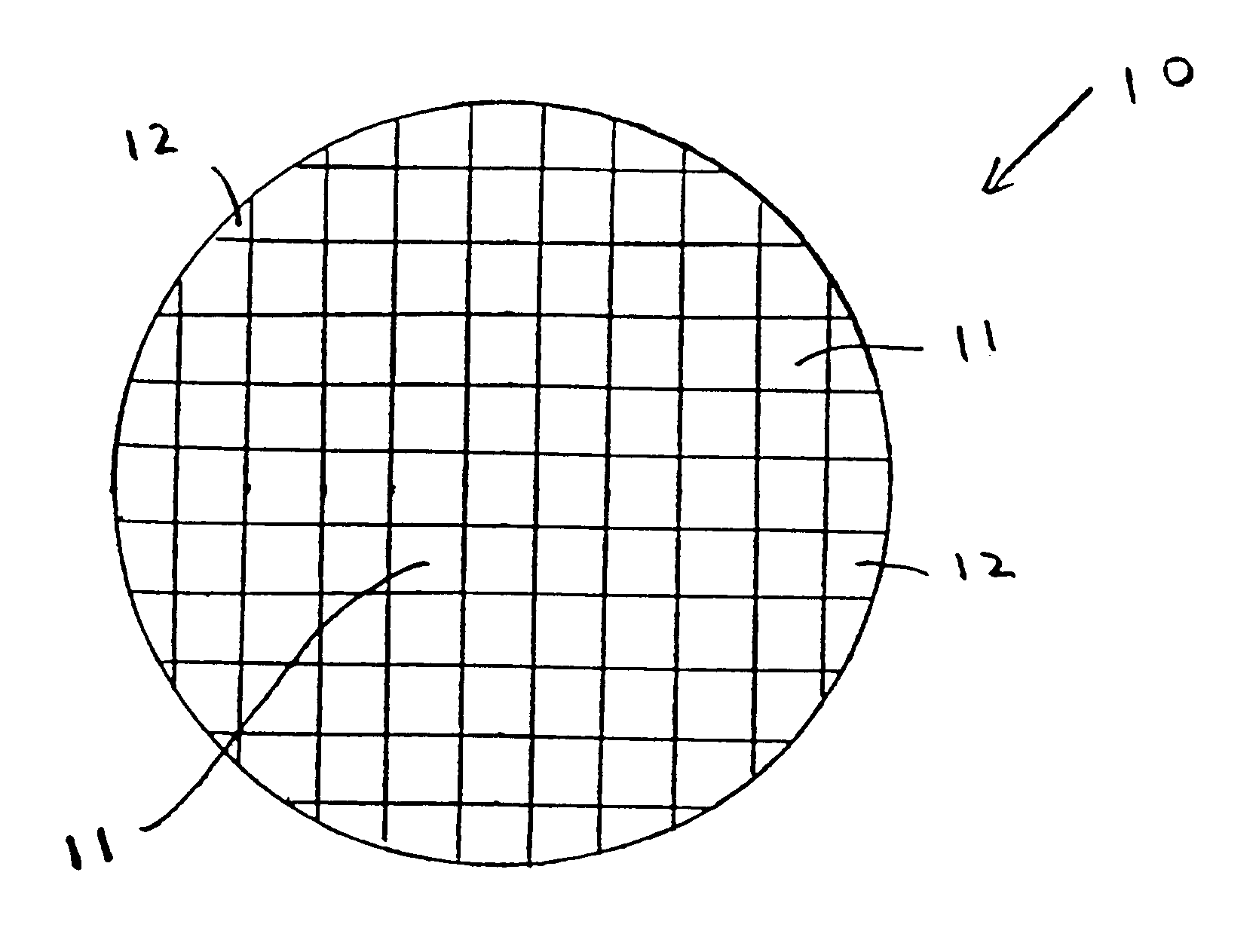

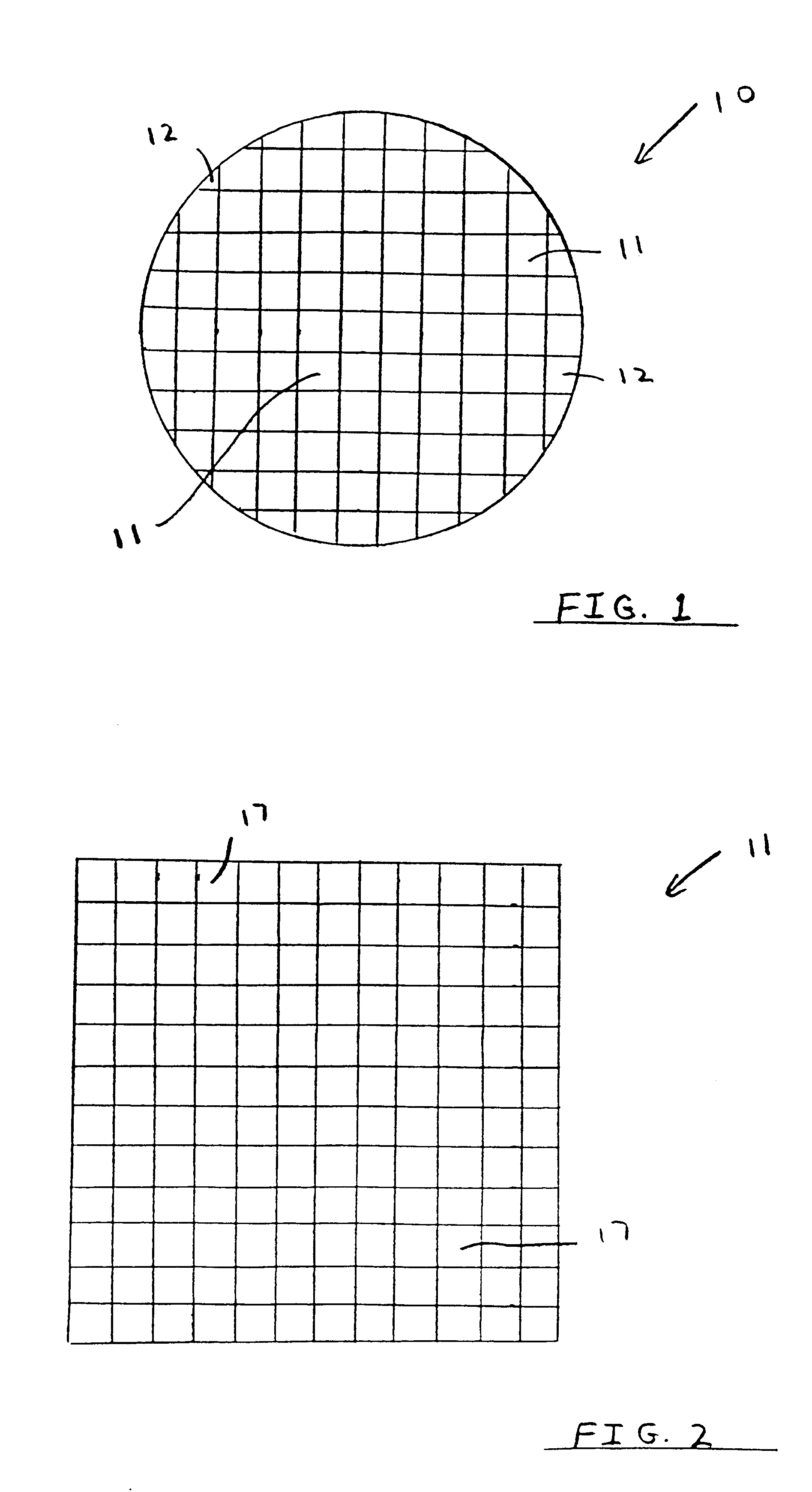

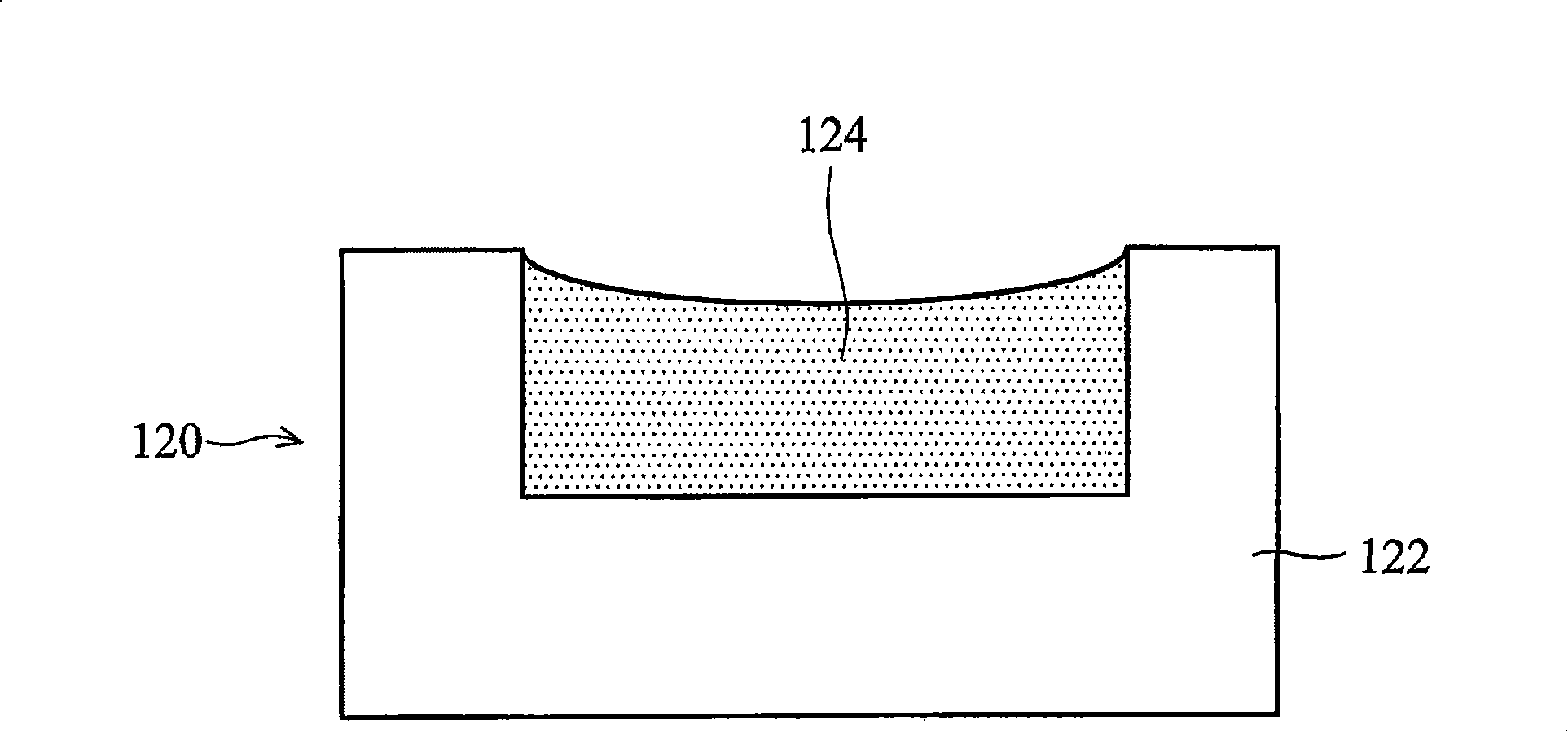

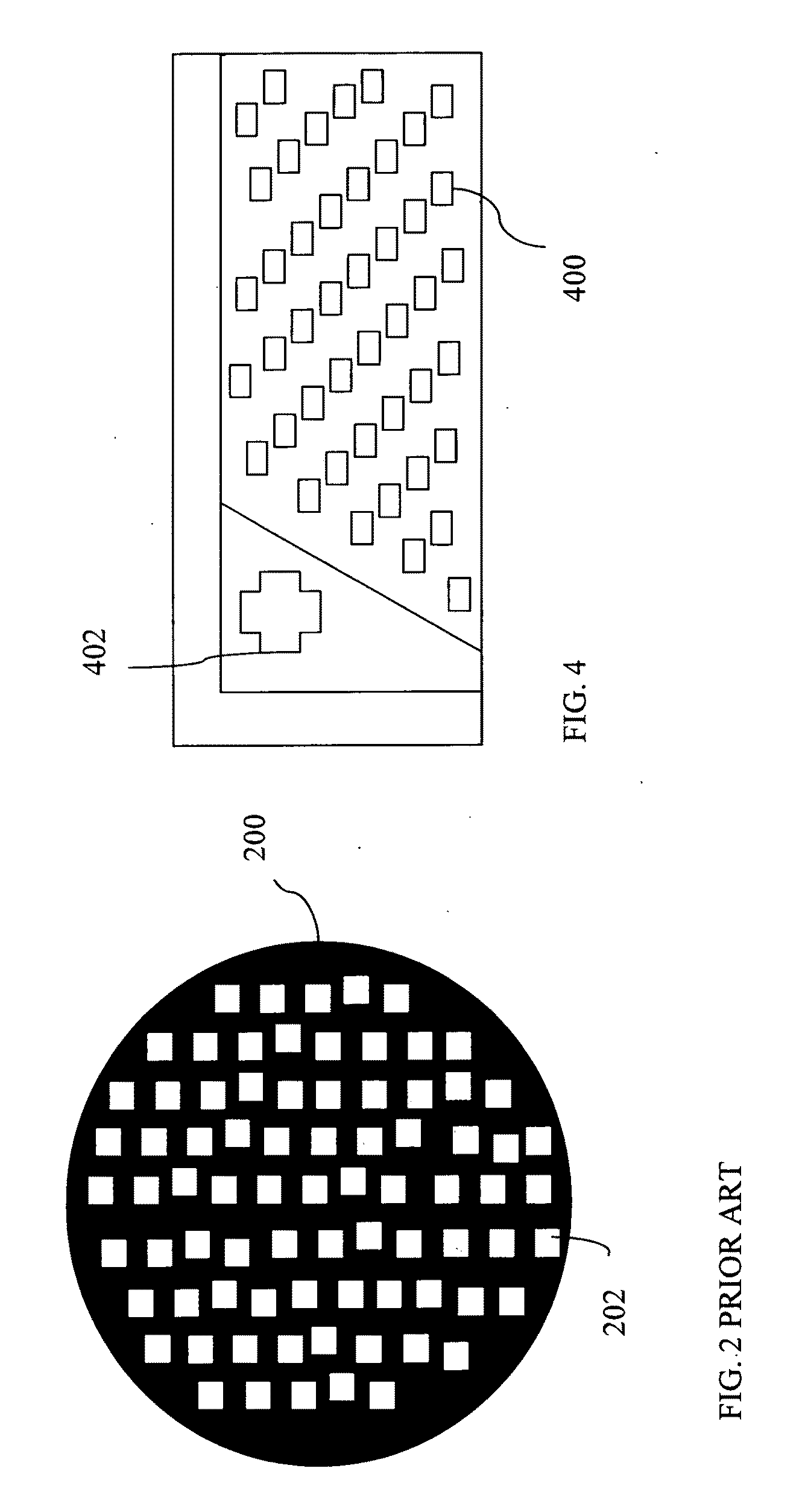

Dummy patterns for aluminum chemical polishing (CMP)

InactiveUS6344409B1Decreases difference in pattern factorReduce the differenceSemiconductor/solid-state device manufacturingPlane surface grinding machinesCompound (substance)Engineering

A method and apparatus is provided for planarizing damascene metallic circuit patterns of a plurality of discrete integrated circuit chips on a metal coated silicon wafer wherein the circuitry on the chips on the wafer are either designed to be within a defined high metal density circuit range and low density metal circuit range and / or to provide dummy circuitry in the damascene process to provide a substantially uniform circuit density over the chip and the wafer surface. It is preferred that each chip on the surface of the wafer be divided into a plurality of regions and that each region be provided with dummy metallization, if necessary, to provide a relatively uniform circuit density in that region and consequently on the wafer surface. The invention also contemplates adding dummy circuitry to the periphery of the wafer in areas which are not formed into chips (chip fragments). The invention also provides semiconductor wafers made using the method and / or apparatus of the invention.

Owner:QIMONDA

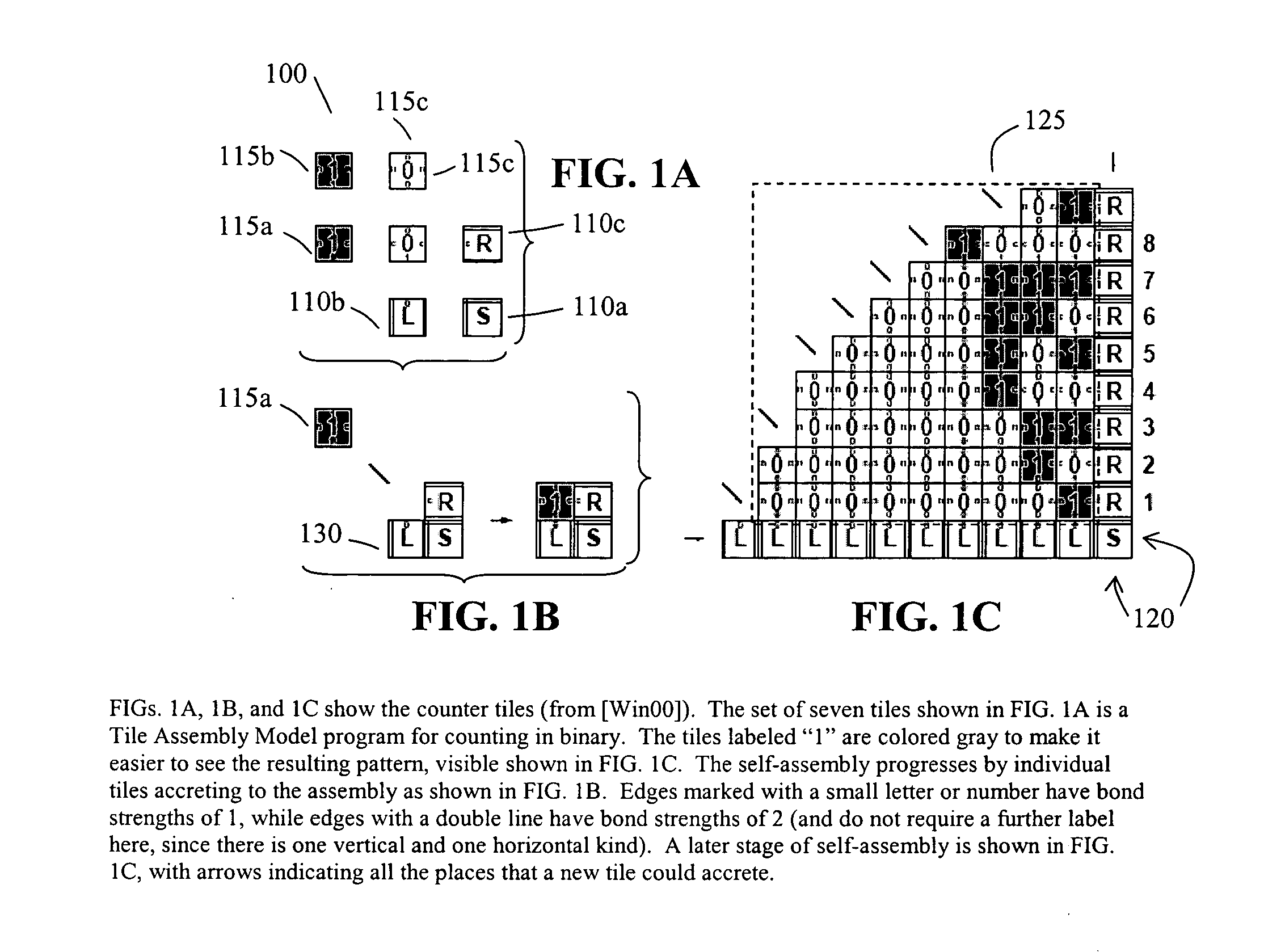

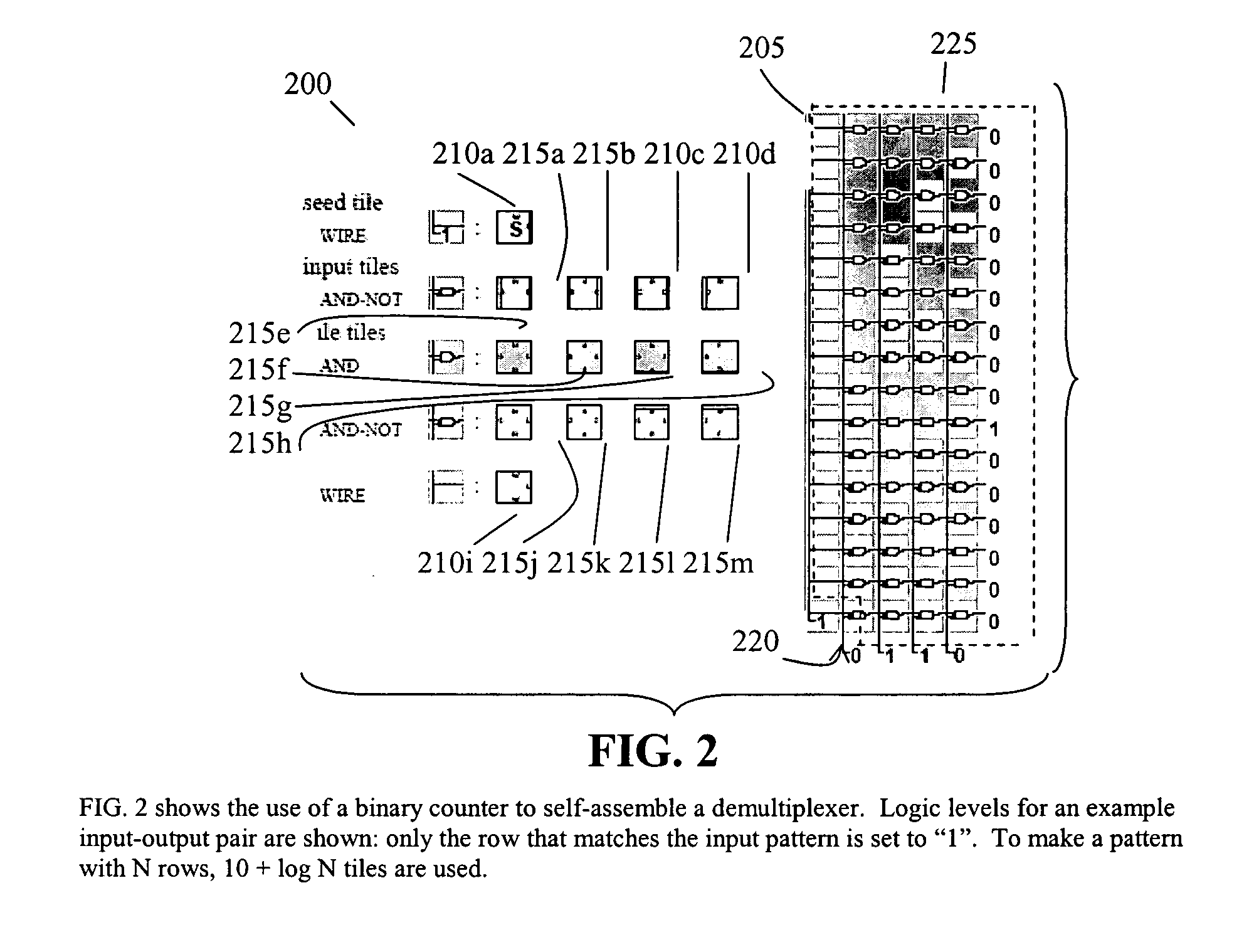

Self-assembled circuits and circuit patterns

InactiveUS20050112614A1Easy to attractConvenient bindingMicrobiological testing/measurementNanoinformaticsAlgorithmSelf-assembly

A self-assembly method for circuit patterns includes generating a set of tiles, each of the tiles corresponding to a segment of molecules, the set of tiles comprising a set of rule tiles and a set of boundary tiles, each tile having one or more binding regions; assigning a label from a set of labels to each binding region; self interacting, with attractive forces, one or more of the tiles with one or more other tiles among the set of tiles; associating using selective interaction of at least one boundary tile from the set of boundary tiles with at least one rules tile from the set of rules tiles based upon at least a label from the one boundary tile and at label from the one rules tiles; and bonding at least one binding region of the one boundary tile with at least one binding region of the one rules tile.

Owner:CALIFORNIA INST OF TECH

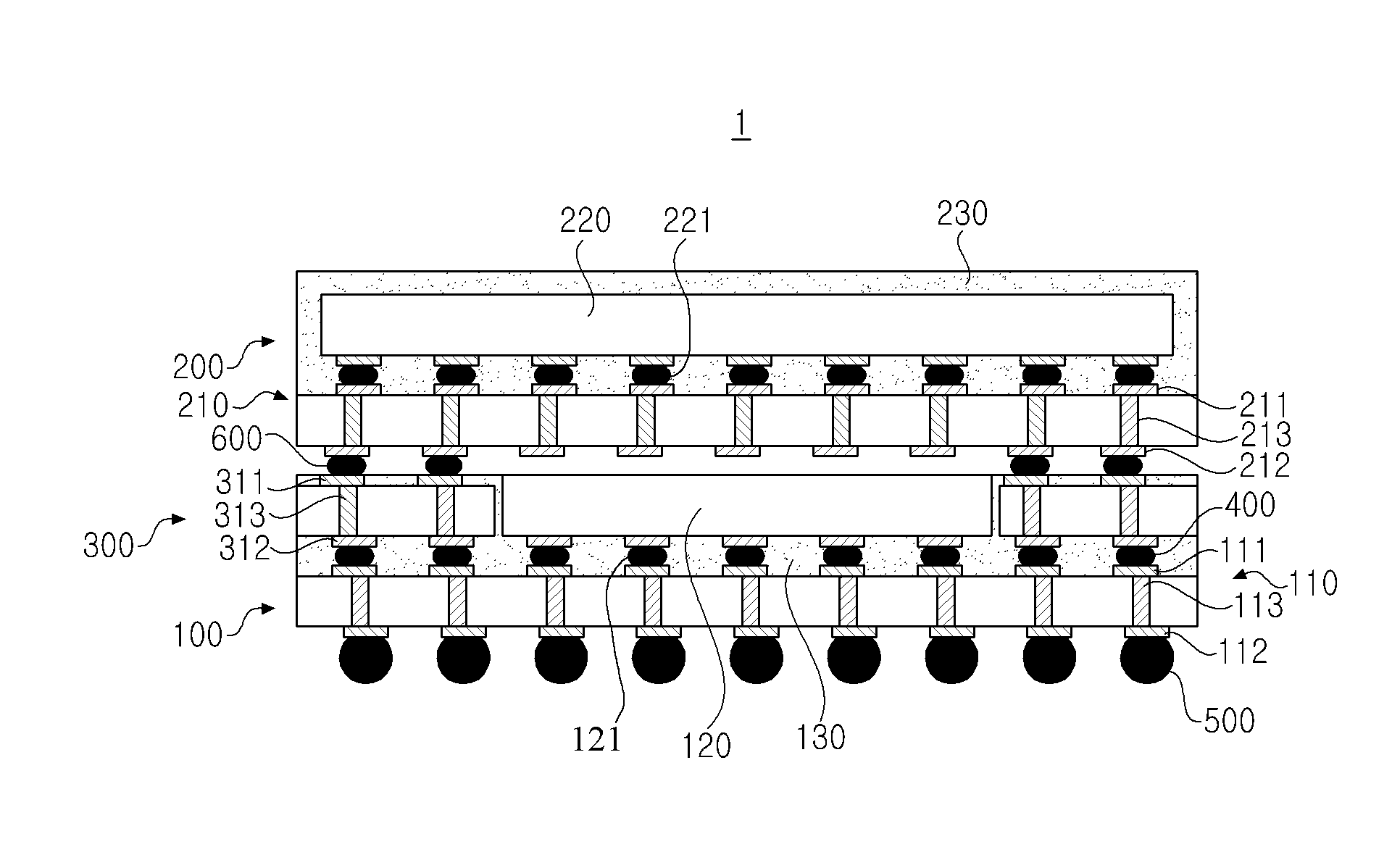

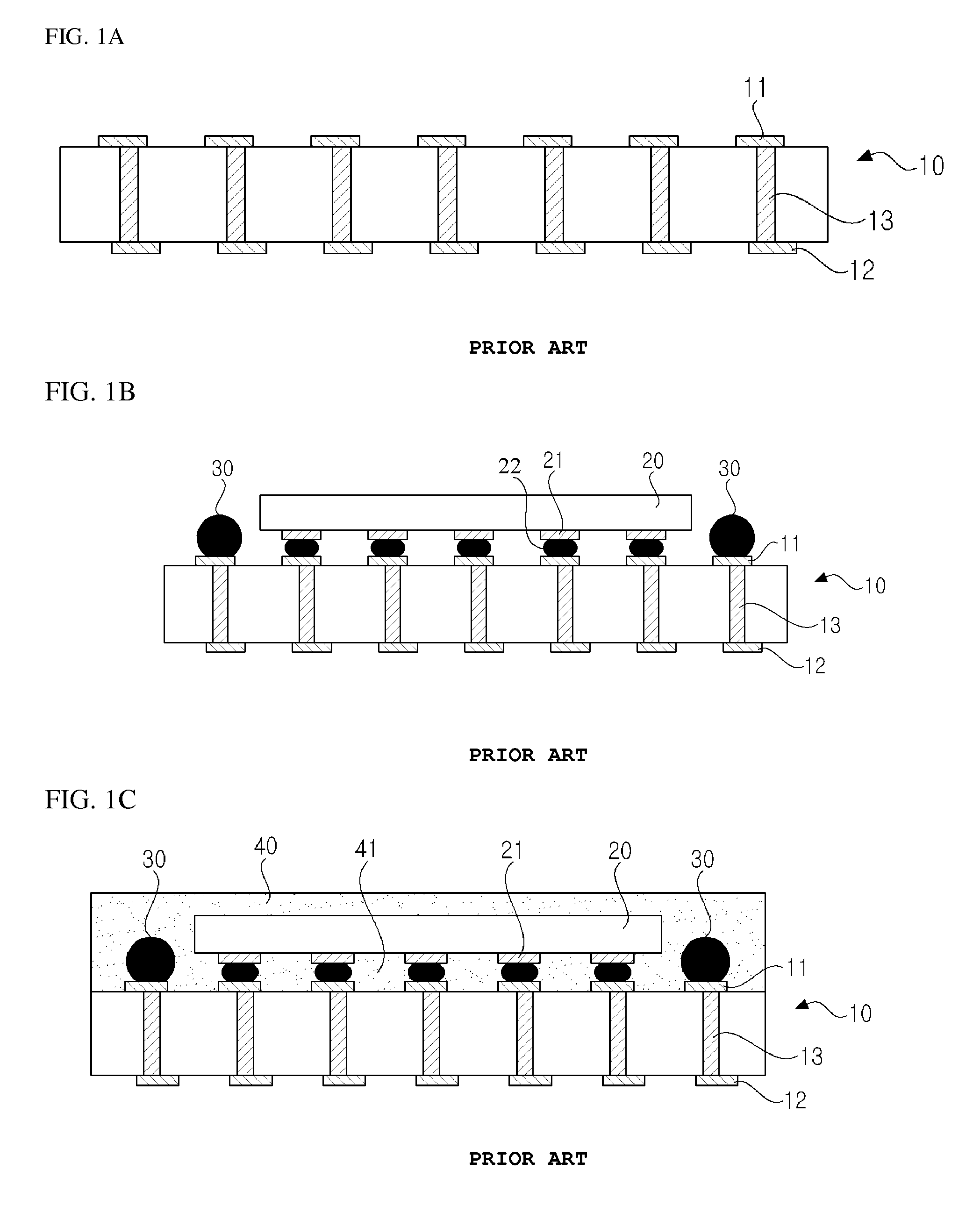

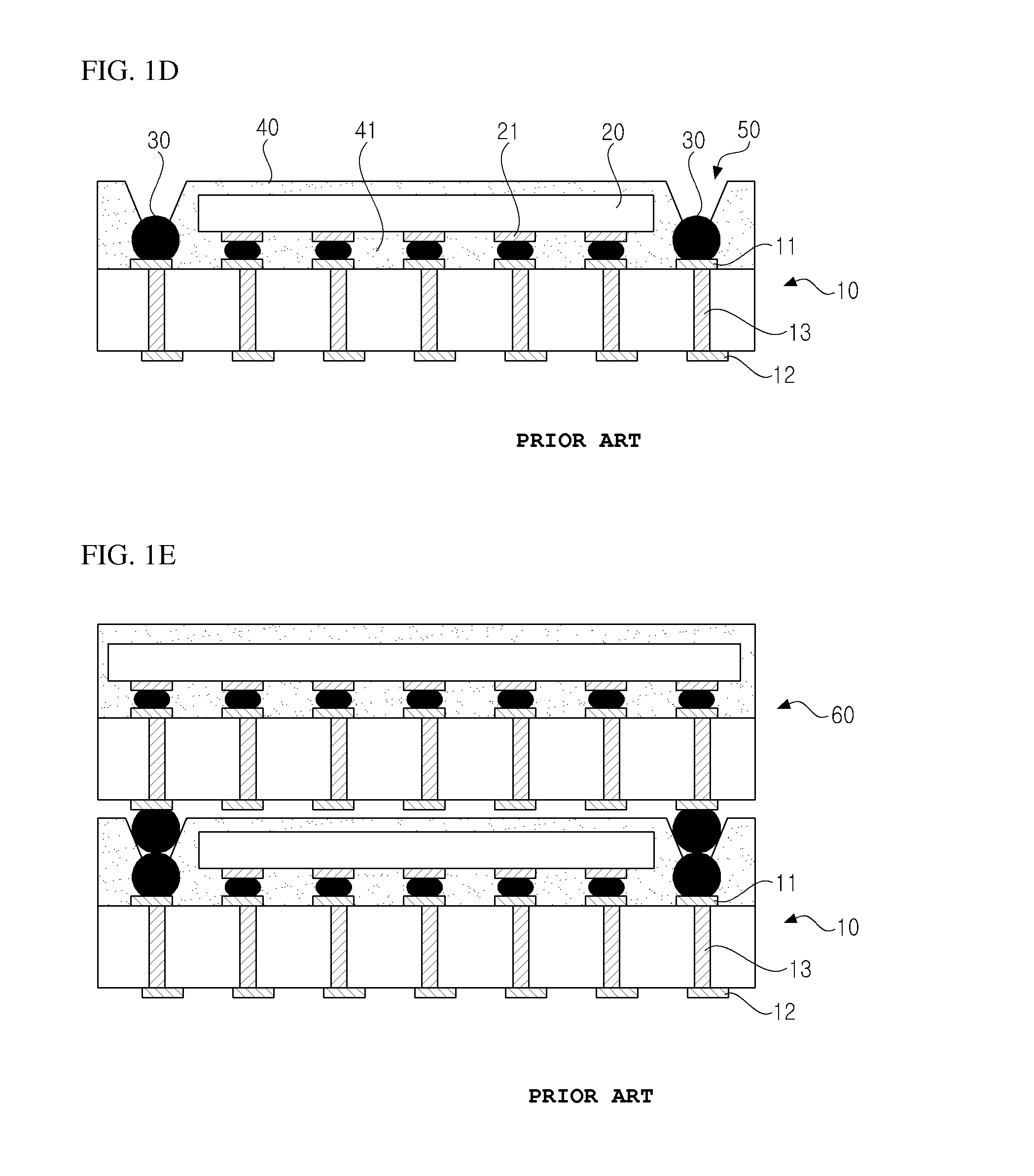

Integrated circuit package and method for manufacturing the same

InactiveUS20140312481A1Problem be addressIncrease the number ofSemiconductor/solid-state device detailsSolid-state devicesSemiconductor chipInterposer

A stacked integrated circuit package and a method for manufacturing the same are provided.The stacked integrated circuit package includes a first integrated circuit package comprising a first substrate, a first semiconductor chip, and a first molding portion, an interposer mounted on the first substrate to be electrically connected to the circuit pattern of the first substrate by a first solder bump, the interposer being provided with an opening to accommodate the first semiconductor chip, and a second integrated circuit package stacked on the first integrated circuit package and the interposer and electrically connected to the interposer by a second solder bump, the second integrated circuit package comprising a second substrate, a second semiconductor chip, and a second molding portion.

Owner:STS SEMICON & TELECOMM

Second-order ladder groove bottom graphical printed board and processing method thereof

The invention relates to the printed circuit board technology field, especially relating to a processing method of a second-order ladder groove bottom graphical printed board. The method comprises the following steps: carrying out a pretreatment on a first daughter board which reserves a plug-in hole, a second daughter board provided with a circuit graph and a third daughter board provided with a circuit graph; pressing the first daughter board and the second daughter board to obtain a first motherboard; carrying out distressing, hole drilling, copper deposition, internal layer figure transfer, and etching resistance metal protective layer plating treatments on the first motherboard to obtain a second motherboard; pressing the third daughter board and the second motherboard to obtain a third motherboard; carrying out distressing, hole drilling, copper deposition, external layer figure transfer treatments on the third motherboard to obtain a finished second-order ladder groove bottom graphical printed board. According to the second-order ladder groove bottom graphical printed board prepared by the method, each ladder can be subjected to wiring and plug-in installation, and a usage scope of a plate is expanded. The invention also relates to the second-order ladder groove bottom graphical printed board.

Owner:珠海杰赛科技有限公司

Preparation method of ceramic circuit board

ActiveCN102695370AGood choiceImprove bindingInsulating substrate metal adhesion improvementLiquid/solution decomposition chemical coatingChemical platingHemt circuits

The invention relates to a ceramic surface modifying technology, particularly relates to a method for metalizing the surface of a ceramic profiled bar, and specifically provides a preparation method of a ceramic circuit board... The preparation method of the ceramic circuit board comprises the preparation steps of: (1) preparing a ceramic substrate; (2) engraving a required circuit pattern with laser on the surface of the ceramic substrate; (3) in chemical plating, and chemically plating copper on the ceramic substrate obtained in the step (2) to realize bottoming; and (4) chemically plating nickel or chemically plating gold or silver on the surface of a plated layer, so as to prevent copper from being oxidized. According to the preparation method of the ceramic circuit board provided by the invention, a laser engraving technology is combined with chemical copper plating, so that the ceramic board is selectively coated with copper, and the good selectivity is achieved. By using the laser engraving technology, the binding force of a conductive layer with a ceramic base body is good; production equipment is cheap and easy to obtain. Furthermore, the three-dimensional ceramic circuit board can be easily produced; the circuit pattern design is very simple; and the circuit precision is high. Moreover, compared with the other technologies, the preparation method provided by the invention has the advantage that the 'three wastes' emission in a production process is reduced.

Owner:黄石星河电路有限公司

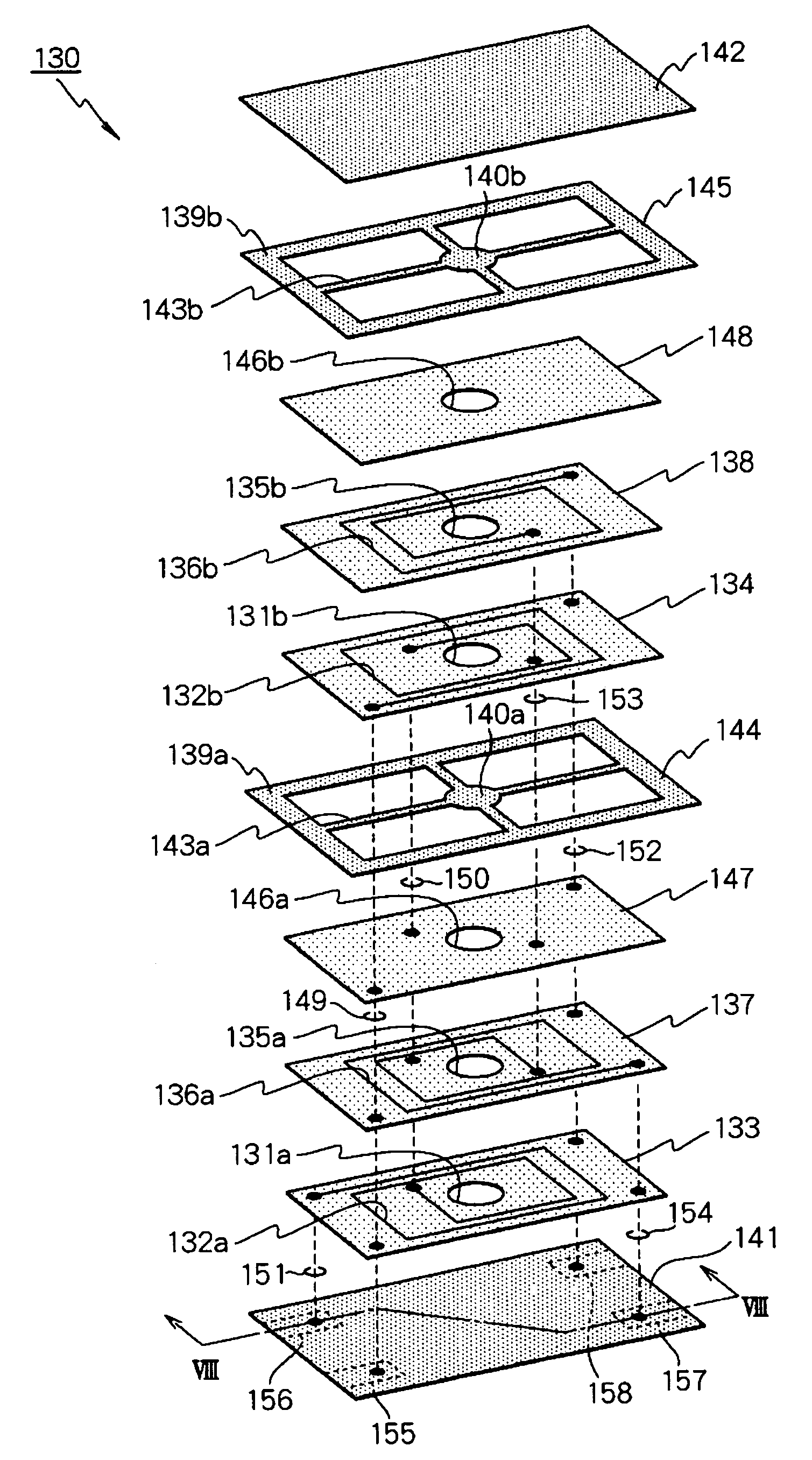

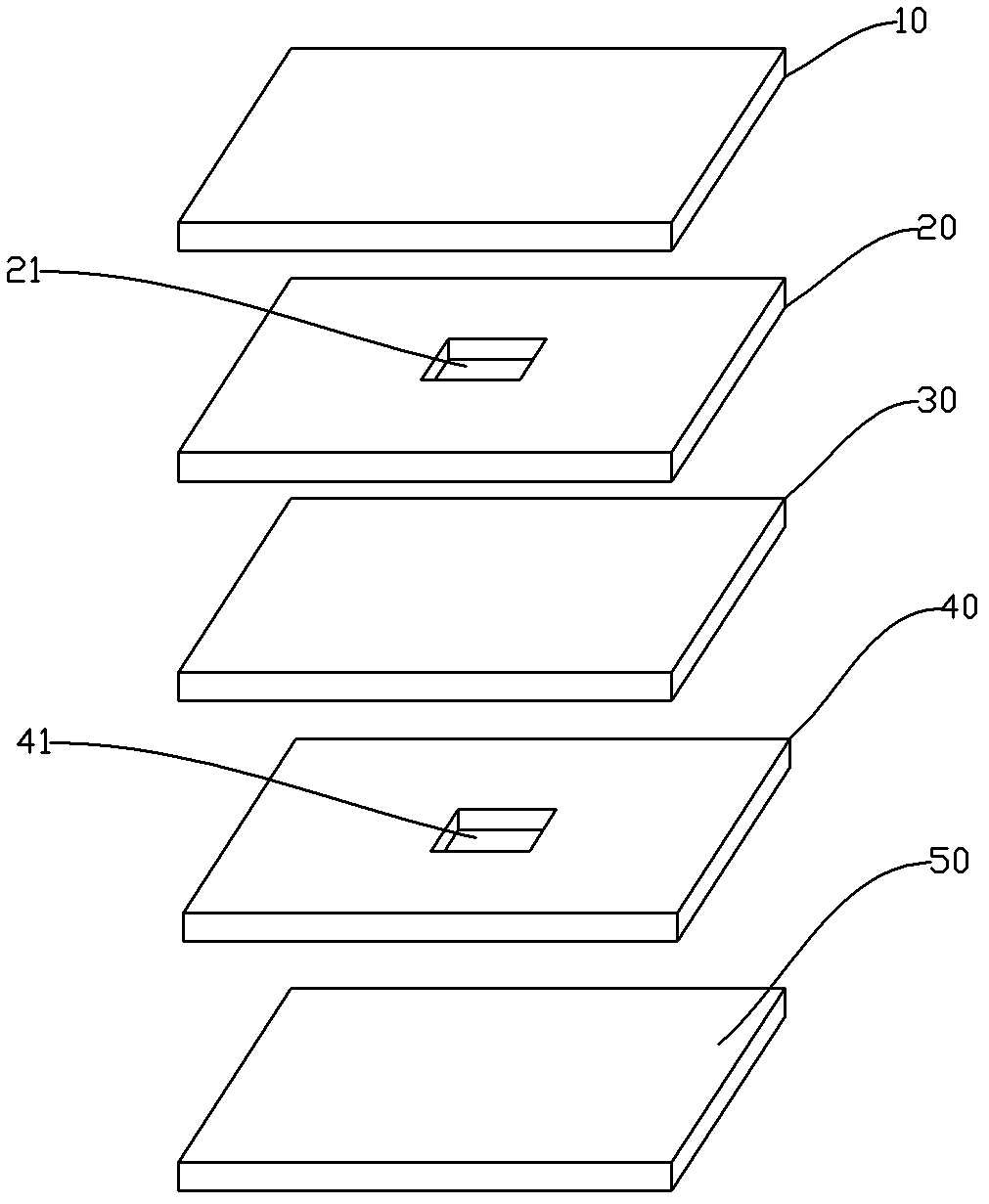

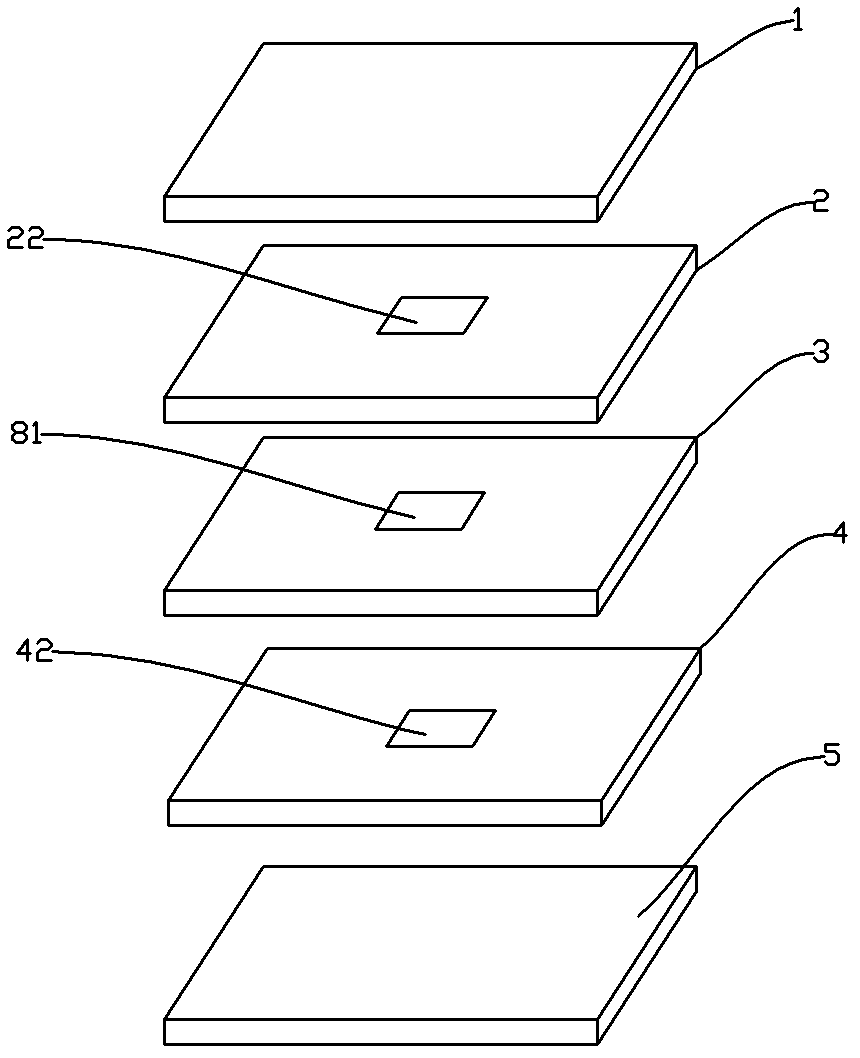

Multilayer laminated circuit board

InactiveUS7375609B2Small sizeImprove the overall coefficientTransformers/inductances coils/windings/connectionsElectrical connection printed elementsTransformerHemt circuits

A multi-layer laminated circuit board 10A of the present invention is formed by laminating together a multi-layer transformer 10, a multi-layer part sheet 30 formed with a multi-layer part, and a wiring sheet 50 formed with a circuit pattern. The multi-layer transformer 10 is incorporated into the multi-layer laminated circuit board 10A, and therefore a package for the multi-layer transformer 10 is omitted, and the wiring between the multi-layer transformer 10 and other components is reduced to a minimum.

Owner:TAMURA KK

Protective film separator in semiconductor wafer grinding process

InactiveUS20020094760A1Polishing machinesRevolution surface grinding machinesTectorial membraneEngineering

A protective film separator comprising an adsorption means and a peeling means for removing the protective film in a semiconductor wafer backside grinding process. The adsorption means uses a vacuum to separate a part of a protective film adhered to an electrical circuit patterned side of a wafer from the patterned side of the wafer. The peeling means presses each side of the part of the protective film separated from the wafer by the adsorption means, and separates unpeeled parts thereof from the patterned side of the wafer. The protective film separator of the present invention reduces costs and expenses for raw materials by eliminating the need for extra removing tape or heat-activated adhesive tape. The present invention may also improve semiconductor yields by reducing the external force applied to a wafer during removal of the protective film, thereby allowing better protection from impurities.

Owner:SAMSUNG ELECTRONICS CO LTD

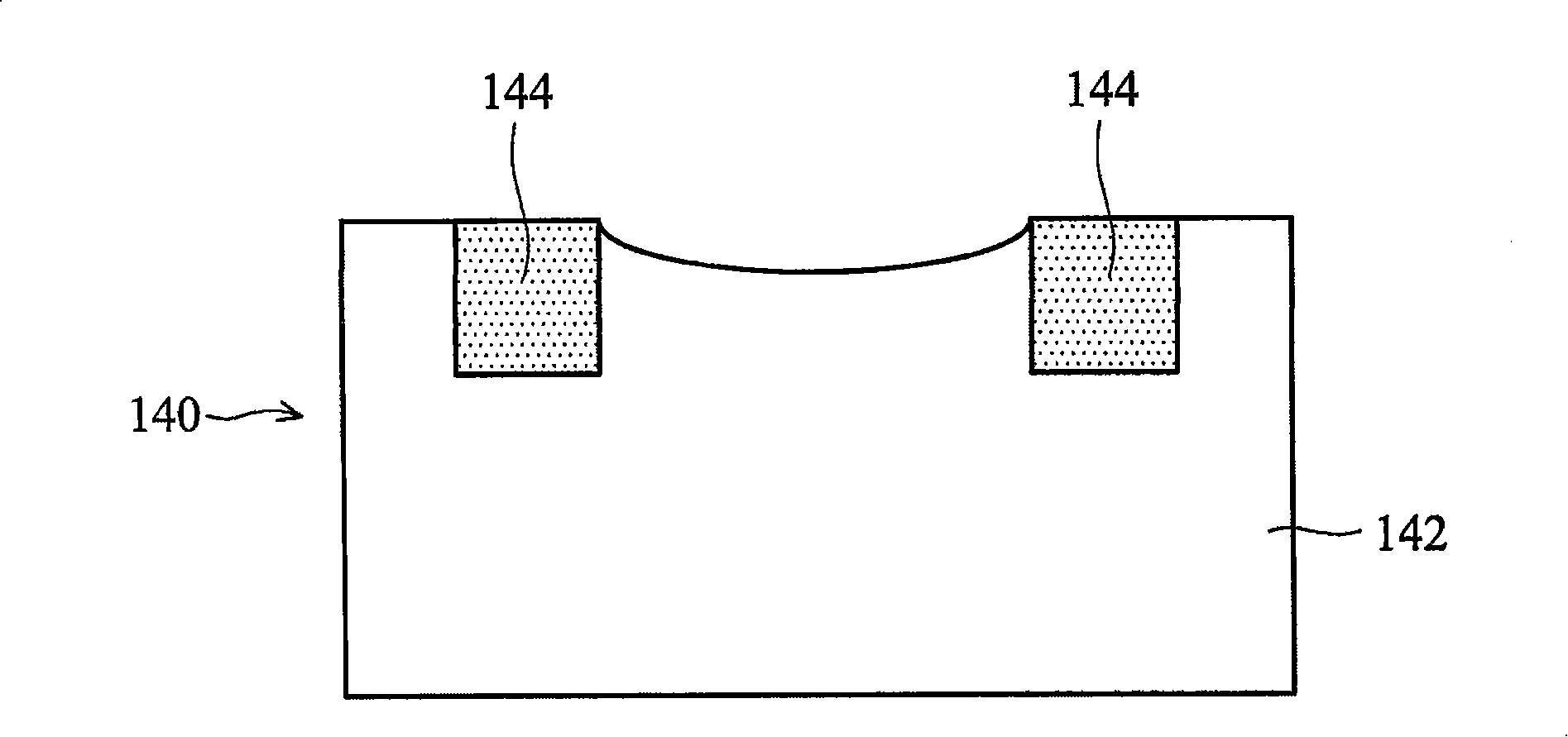

Method of filling redundancy for semiconductor manufacturing process and semiconductor device

ActiveCN101231667AReduce in quantityReduce consumptionSemiconductor/solid-state device detailsSolid-state devicesGraphicsCPU time

A dummy filling method for a semiconductor manufacturing process provides a circuit pattern and generates a density report of the circuit pattern to identify a feasible area for dummy insertion. The method also includes using the density report to simulate a planarization manufacturing process and identifying hot spots on the circuit pattern, filling virtual redundant patterns in the feasible area, and then adjusting the density report. The method simulates the planarization process using the adjusted density report until the hot spot is removed. The invention can reduce the amount of redundant metal in circuit design and save photomask time, CPU time, and signal storage memory. This will help design timing closure (time closure) faster and easier.

Owner:TAIWAN SEMICON MFG CO LTD

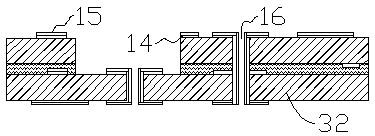

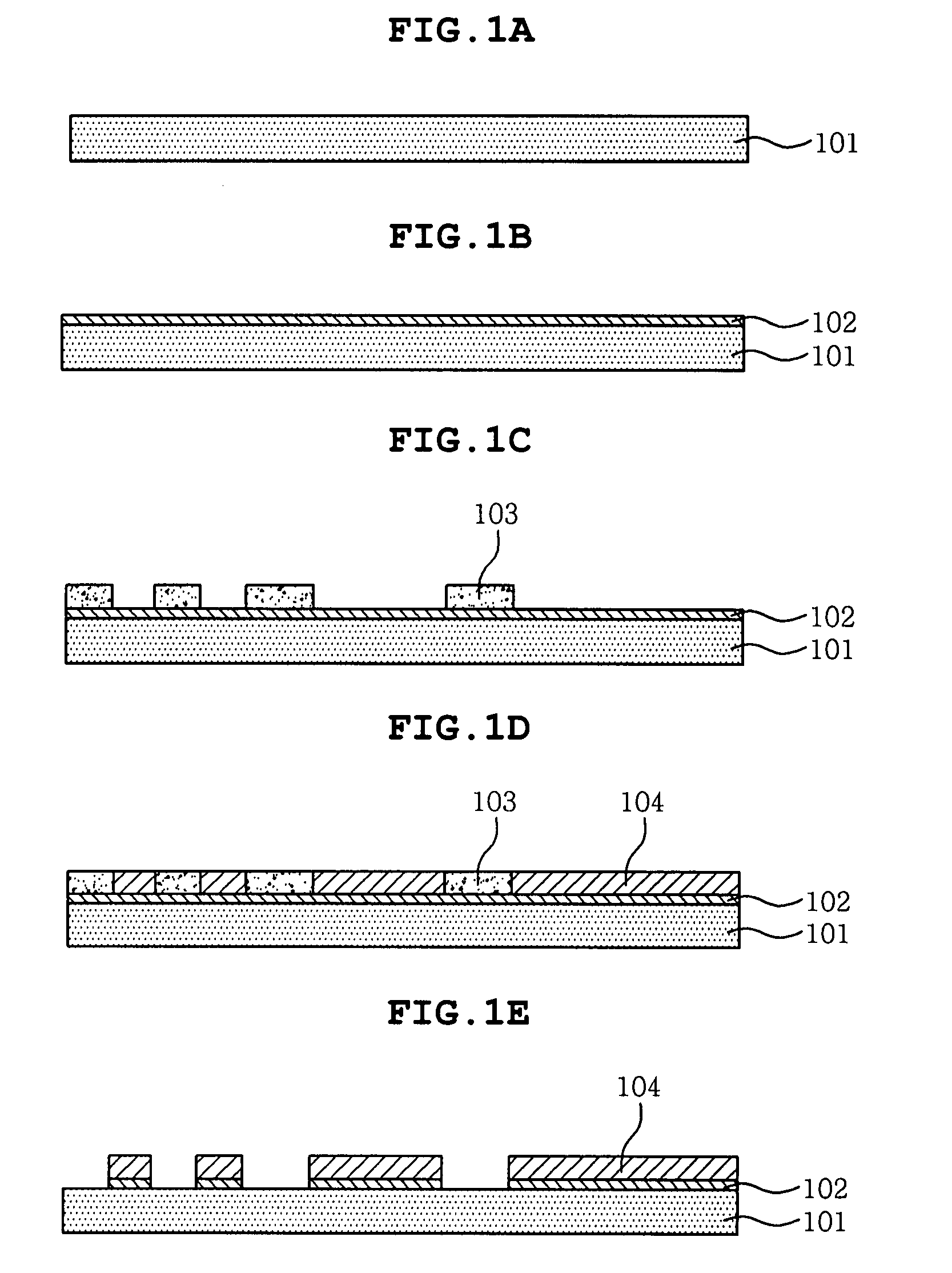

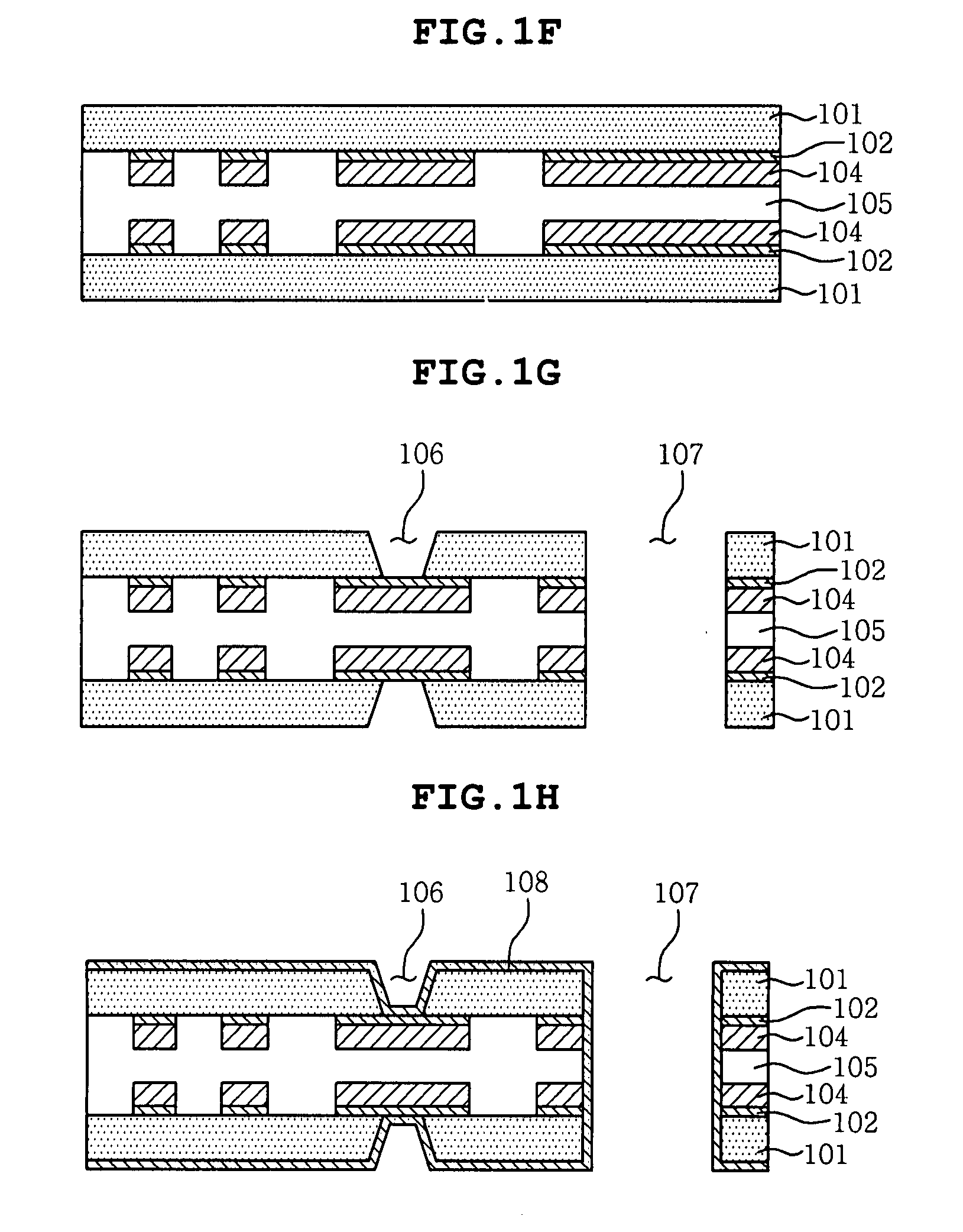

Method for making a multilayer circuit board having embedded passive components

A method for fabricating a core circuit board having passive components, such as resistors, capacitors and inductors, is disclosed, which can be used to construct a multilayer circuit board having embedded passive components. In making such as a core circuit board, a resistive film which is a continuous or non-continuous is first formed on one side of a conductive foil. Two such conductive foils are laminated onto a high dielectric layer. The electrodes for various passive components or spiral coils for the inductive components and electrical circuit pattern are finally made on the same conductive foils simultaneously. Finally, a core circuit board having passive components for further making a multilayer circuit board is thus constructed.

Owner:PHOENIX PRECISION TECH CORP

Lamination method of embedding passive components in an organic circuit board

InactiveUS20020182374A1Improve uniformityImprove reliabilityHollow non-inflatable ballsLayered productsCapacitanceHemt circuits

A method for fabricating an organic circuit board having embedded passive components, such as resistors, capacitors and inductors, is disclosed. In embedding a resistor or capacitor, a passive unit of a resistive film or a capacitive film is first made on one side of a conductive foil. In forming an inductor, a soft magnetic film is first made on one side of a conductive foil. The foil with the soft magnetic film is then introduced into the multilayer circuit board processing. The electrodes for various passive components or spiral coils for the inductive components and electrical circuit pattern are finally made on the same conductive foil simultaneously. The soft magnetic film deposited on the top of the spiral coil may be made to further improve inductor performance.

Owner:PHOENIX PRECISION TECH CORP

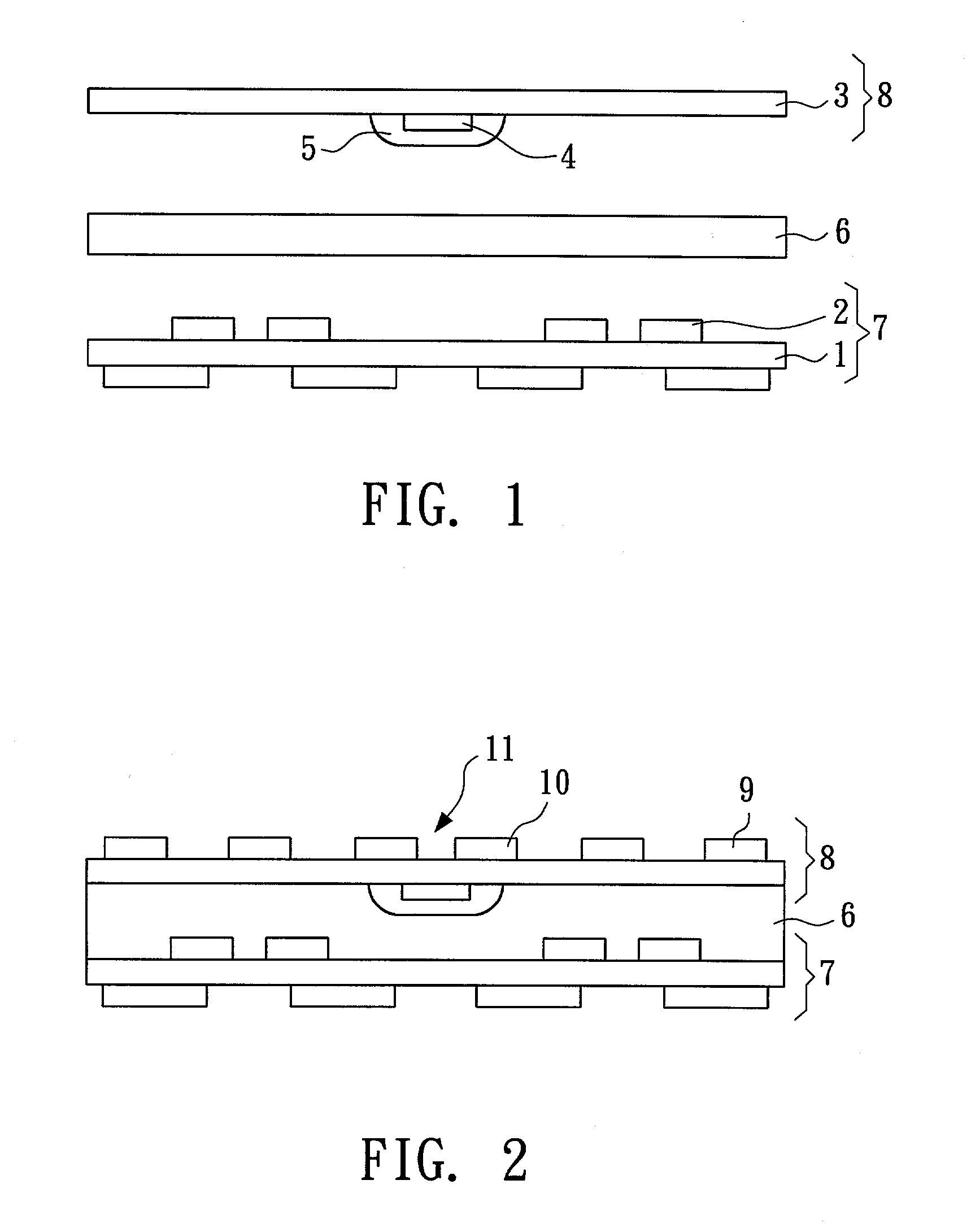

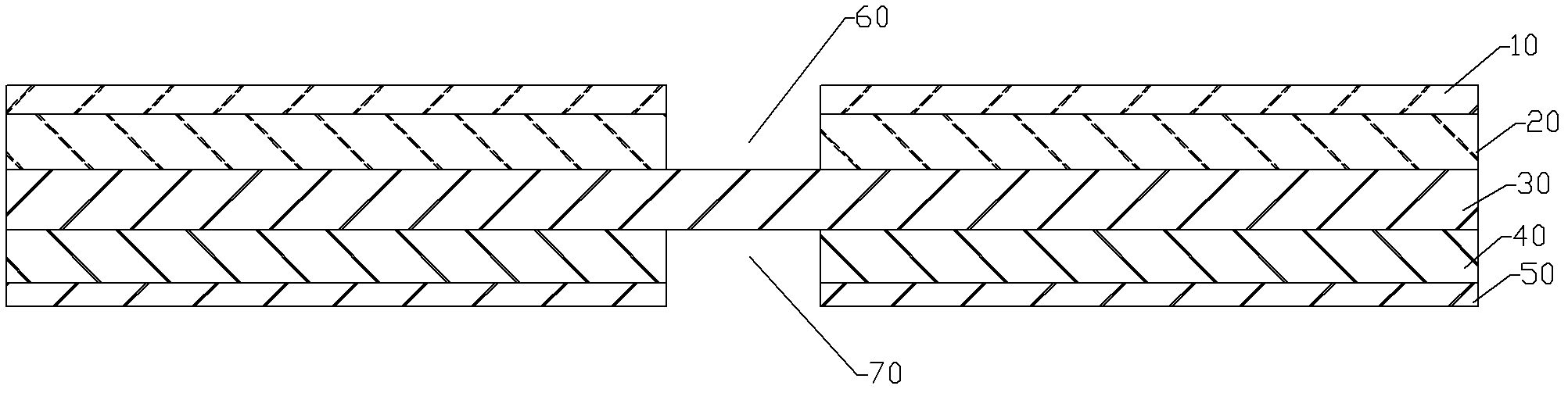

Printed circuit board and method of manufacturing the same

InactiveUS20080053688A1Function increaseHighly reliable fine circuitsDielectric materialsHigh frequency circuit adaptationsGas phaseIon beam

Disclosed herein are a thin printed circuit board, in which a pair of high-functional resin substrates having a permittivity ranging from 1.5 to 4.0, on one surface of each of which a circuit pattern is formed through ion-beam surface treatment, vapor deposition and electroplating, are layered with an insulating layer interposed therebetween, and a method of manufacturing the printed circuit board. The circuit patterns are positioned inside the substrates. Thereafter, external layers are formed through ion-beam surface treatment, vapor deposition and electroplating. According to the present invention, the adhesiveness between each of the substrates and a metal layer may be improved through the ion-beam surface treatment / vapor deposition. Furthermore, since the pair of resin substrates are layered with the insulating layer interposed therebetween, the circuit patterns may be disposed inside the pair of resin substrates, so that the total thickness of the substrate may be reduced, thereby realizing highly reliable fine circuits.

Owner:SAMSUNG ELECTRO MECHANICS CO LTD

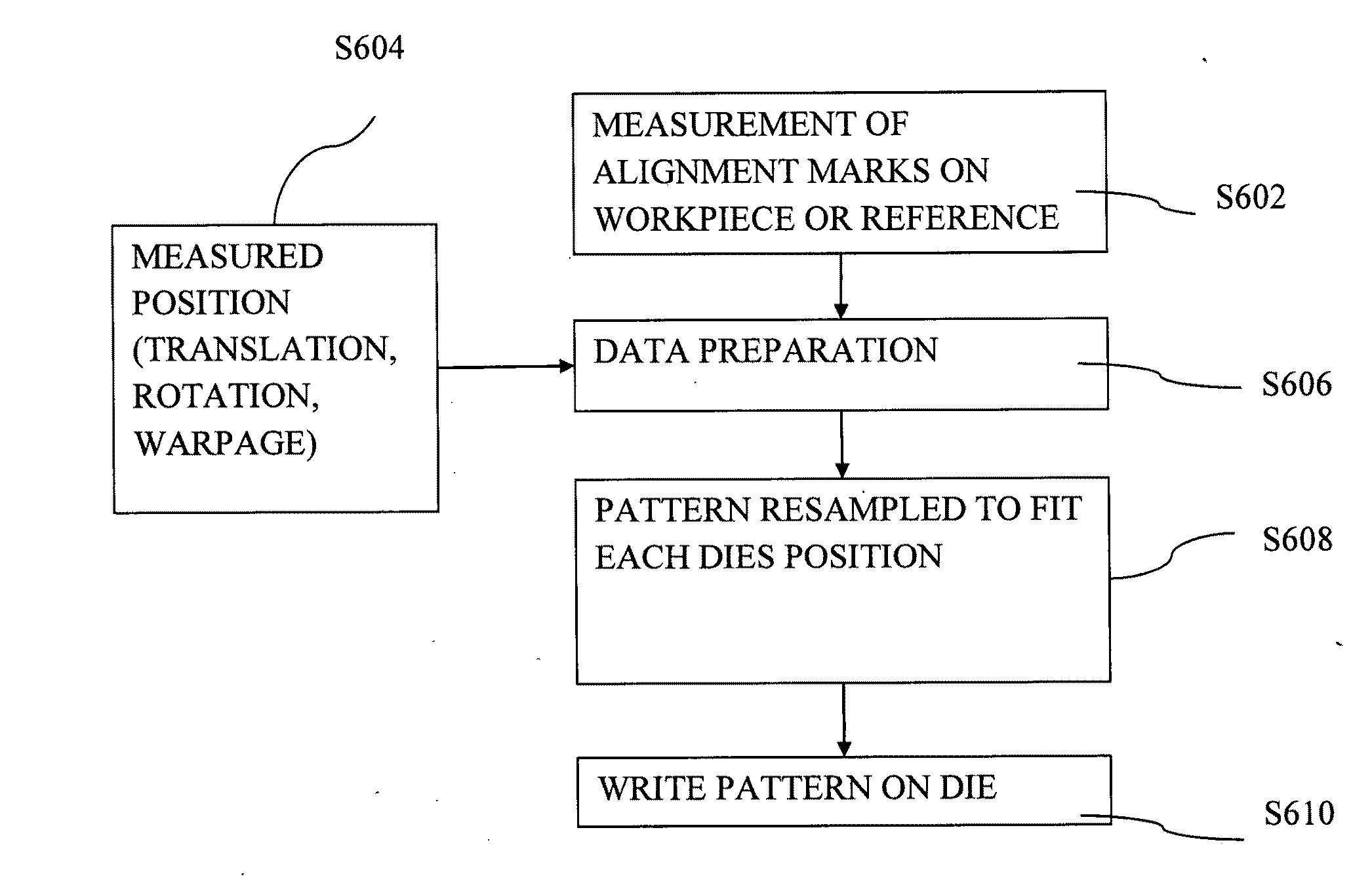

Method and apparatus for performing pattern alignment to die

ActiveUS20110213479A1Low accuracyReduce precisionPhotomechanical apparatusPrinted circuit manufactureManufacturing engineeringMechanical engineering

In a method for patterning a workpiece provided with dies in a direct write machine, pattern data associated with a selected die, or group of dies, is transformed into adjusted circuit pattern data dependent both on the original pattern data and the transformed positions, wherein the adjusted circuit pattern data represents the circuit pattern of the plurality of dies, or group of dies, such that the adjusted circuit pattern is fitted to a plurality of sub-areas of the workpiece area, and wherein each sub-area is associated with a die, or group of dies, among the plurality of dies distributed on the workpiece. A pattern is then written on the workpiece according to the adjusted circuit pattern data.

Owner:MICRONIC LASER SYST

Flat circuit board and manufacturing method thereof

InactiveCN103945644AConductiveMeet the technical requirements of surface sliding contact conductionPrinted circuit secondary treatmentConductive material chemical/electrolytical removalEngineeringMechanical engineering

The invention relates to a flat circuit board and a manufacturing process thereof. A conductive circuit graph strip is arranged on an insulation base board of the flat circuit board, the circuit graph strip is embedded in the upper surface of the insulation base board, and the outer surface of the circuit graph strip and the upper surface of the insulation base board are located on the same plane. The flat circuit board has the advantages of being high in reliability and good in smoothness. After the circuit graph strip is embedded in the insulation base board, circuit external damage is avoided, the strip is broken only when physical damage is caused to the base board, conductivity reliability is high, and the technical requirement for surface sliding contact communication is met. The flat circuit board is especially applicable to precision operation with the strict environment requirement in the fields of aerospace, aviation, military and medical treatment.

Owner:邢台市海纳电子科技有限责任公司

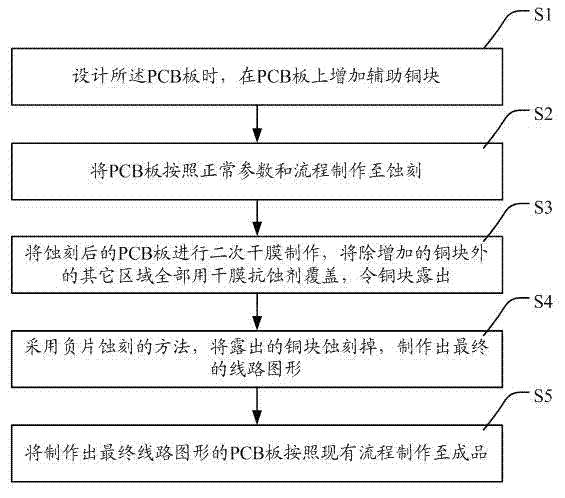

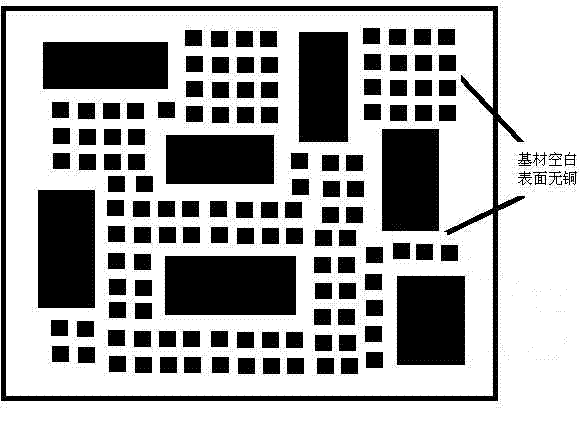

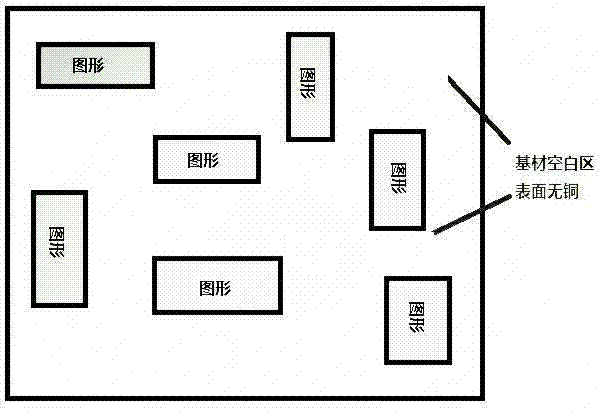

PCB electroplating method for improving electroplating uniformity

The invention discloses a flow diagram of a PCB electroplating method for improving the electroplating uniformity. The PCB electroplating method for improving the electroplating uniformity comprises the steps that firstly, an auxiliary copper block is additionally arranged on a PCB when the PCB is designed; then the PCB is manufactured and etched according to the normal parameters and process; then secondary dry film manufacturing is carried out on the etched PCB, namely all areas, except the area where the copper block is additionally arranged, of the PCB are covered with a dry film photoresist, and the copper block is exposed; the exposed copper block is removed through etching by means of a negative film etching method, and a final circuit graph is formed; the PCB where the final circuit graph is formed is processed according to an existing technological process until a finished product is obtained. By the adoption of the PCB electroplating method for improving the electroplating uniformity, the problem that electroplating and etching are difficult due to the uneven electroplating of a PCB with graphs distributed in an isolated mode is solved, the uniformity of the thickness of electroplating copper of the PCB is improved, and therefore signals can be transmitted more accurately when a user uses the PCB.

Owner:SHENZHEN KINWONG ELECTRONICS

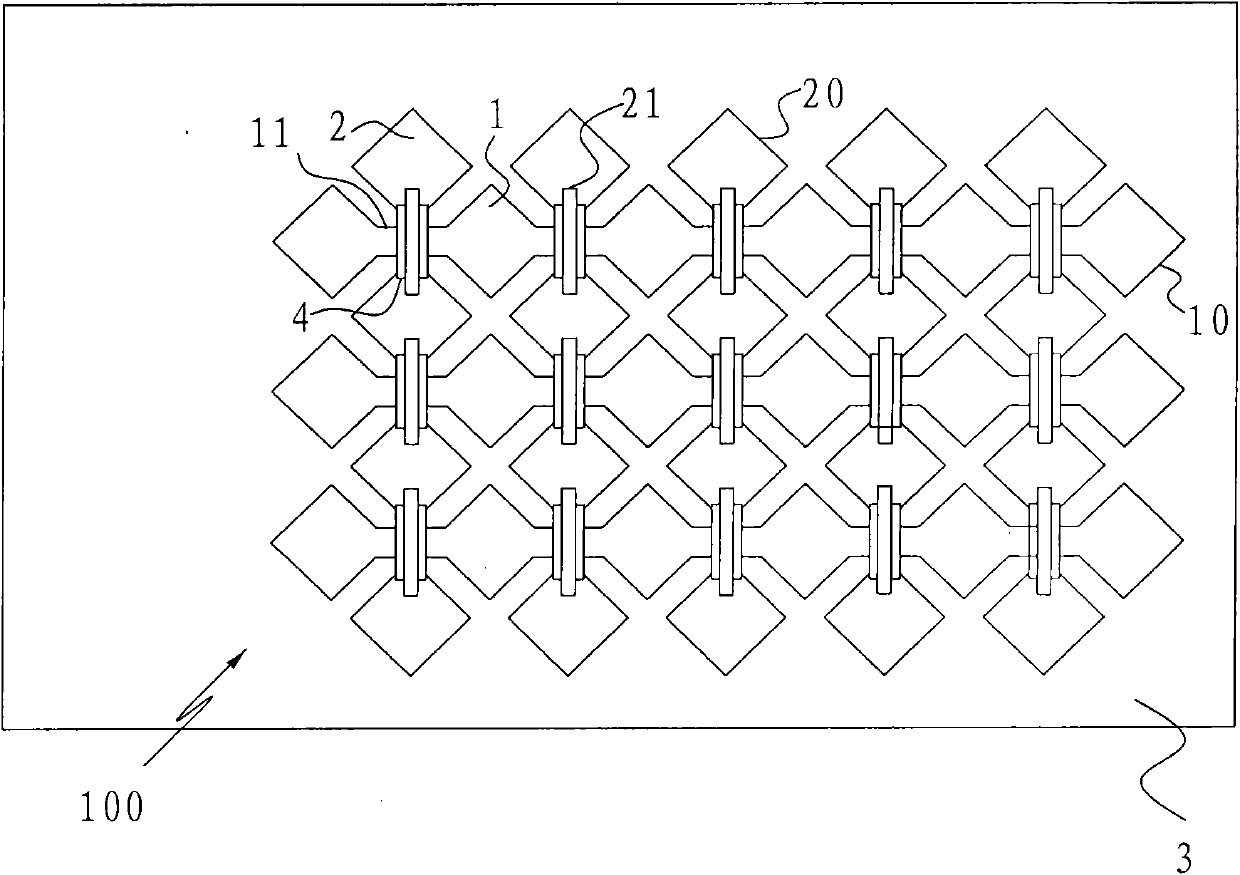

Graphic structure and manufacturing method of touch circuit, touch panel and touch display

InactiveCN102279678AReduce thicknessLower impedanceInput/output processes for data processingGraphicsTouch Senses

The present invention discloses a touch sensing circuit for capacitive touch panel formed on a substrate comprises a transparent conductive layer having a thickness of 100Å-500Å; a conductive layer having a thickness of 1000Å-5000Å; and an insulating layer having a thickness of 1µm-5µm disposed between the transparent conductive layer and the conductive layer.

Owner:TPK TOUCH SOLUTIONS (XIAMEN) INC

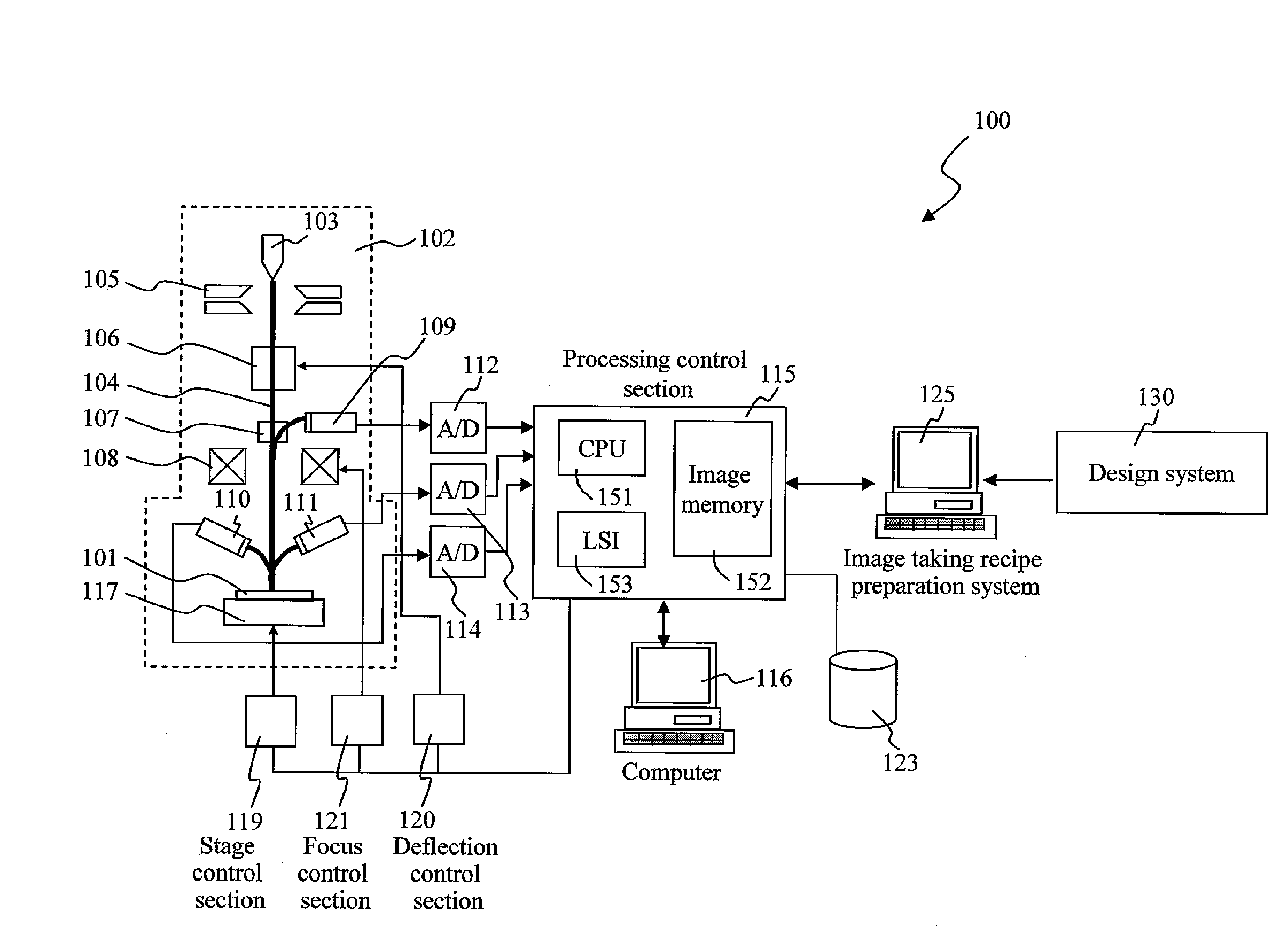

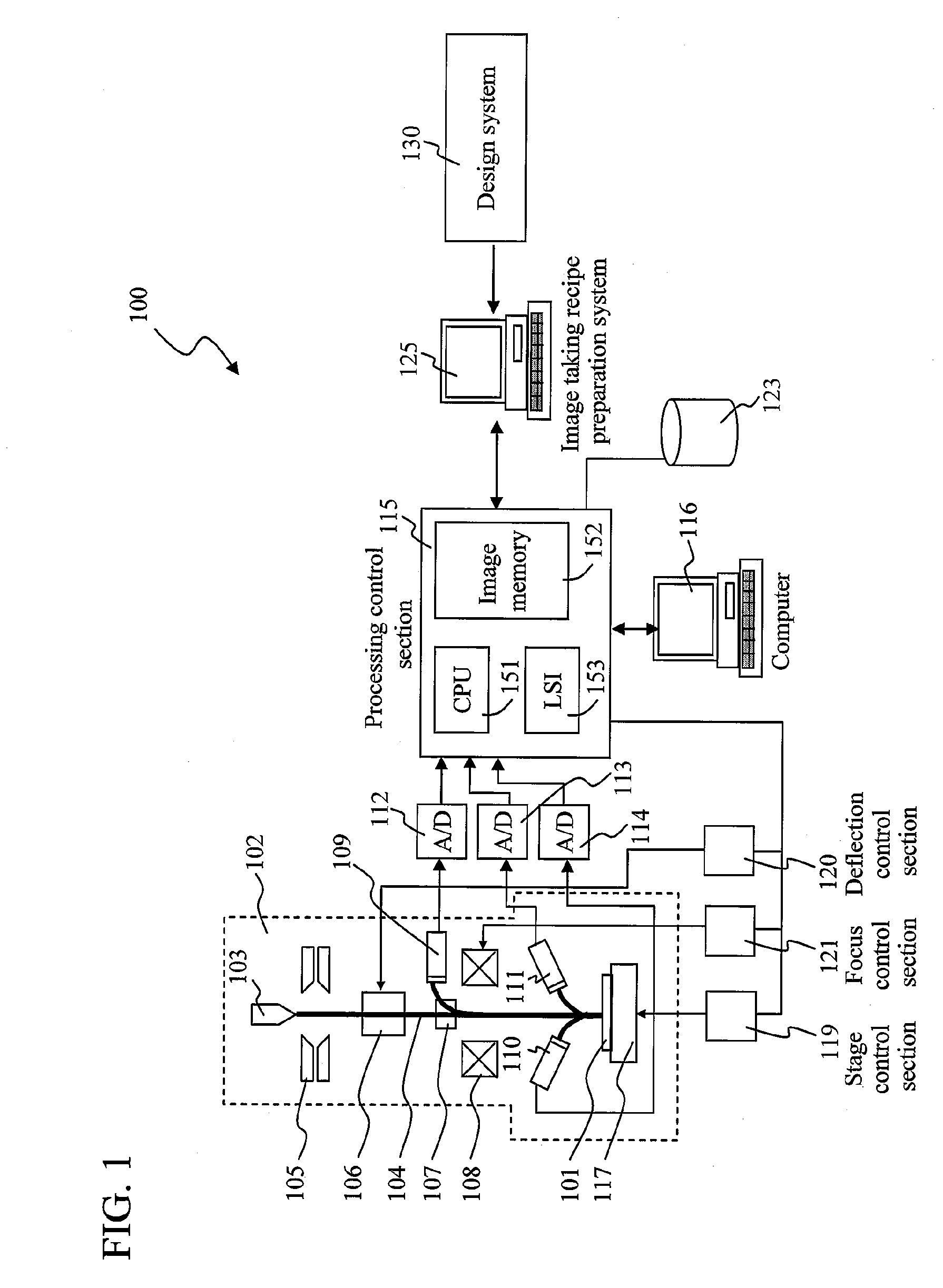

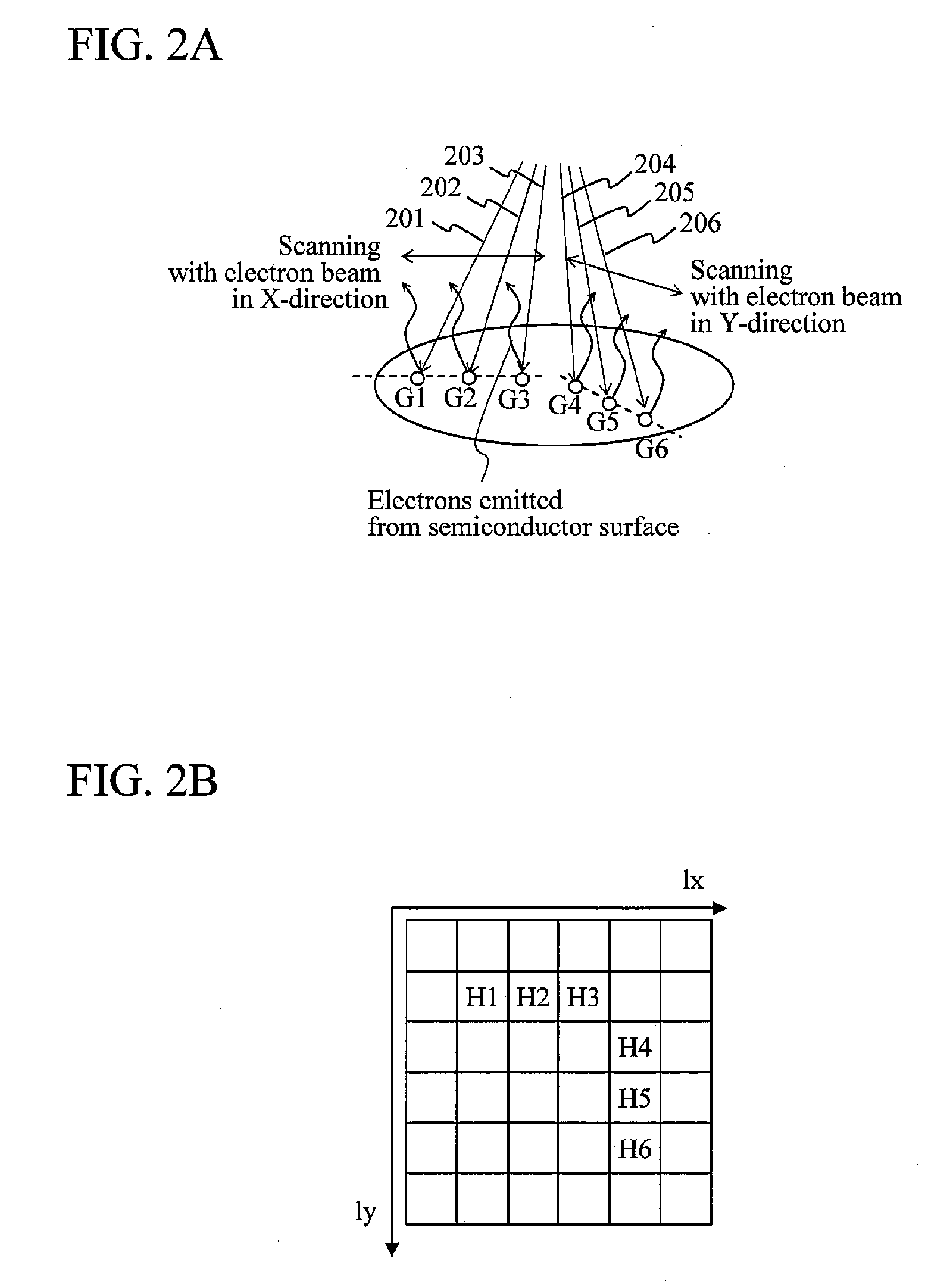

Pattern Inspection Method and Pattern Inspection System

ActiveUS20090039261A1Combined image becomes shrunkIncrease in semiconductor circuit observation timeMaterial analysis using wave/particle radiationSemiconductor/solid-state device testing/measurementPattern recognitionPattern detection

A pattern data examination method and system capable of accurately and speedily examining a circuit pattern without failing to extract pattern contour data are provided. While pattern comparison is ordinarily made by using a secondary electron image, a contour of a pattern element is extracted by using a backscattered electron image said to be suitable for observation and examination of a three dimensional configuration of a pattern element, and pattern inspection is executed by using the extracted contour of the pattern element. More specifically, pattern inspection is executed by comparing a contour of a pattern element with design data such as CAD data to measure a difference between the contour and the data, and by computing, for example, the size of the circuit pattern element from the contour of a pattern. From two or more backscattered electron images formed by detecting backscattered electrons at two or more different spatial positions, pattern contour data contained in the backscattered electron images may be obtained.

Owner:HITACHI HIGH-TECH CORP

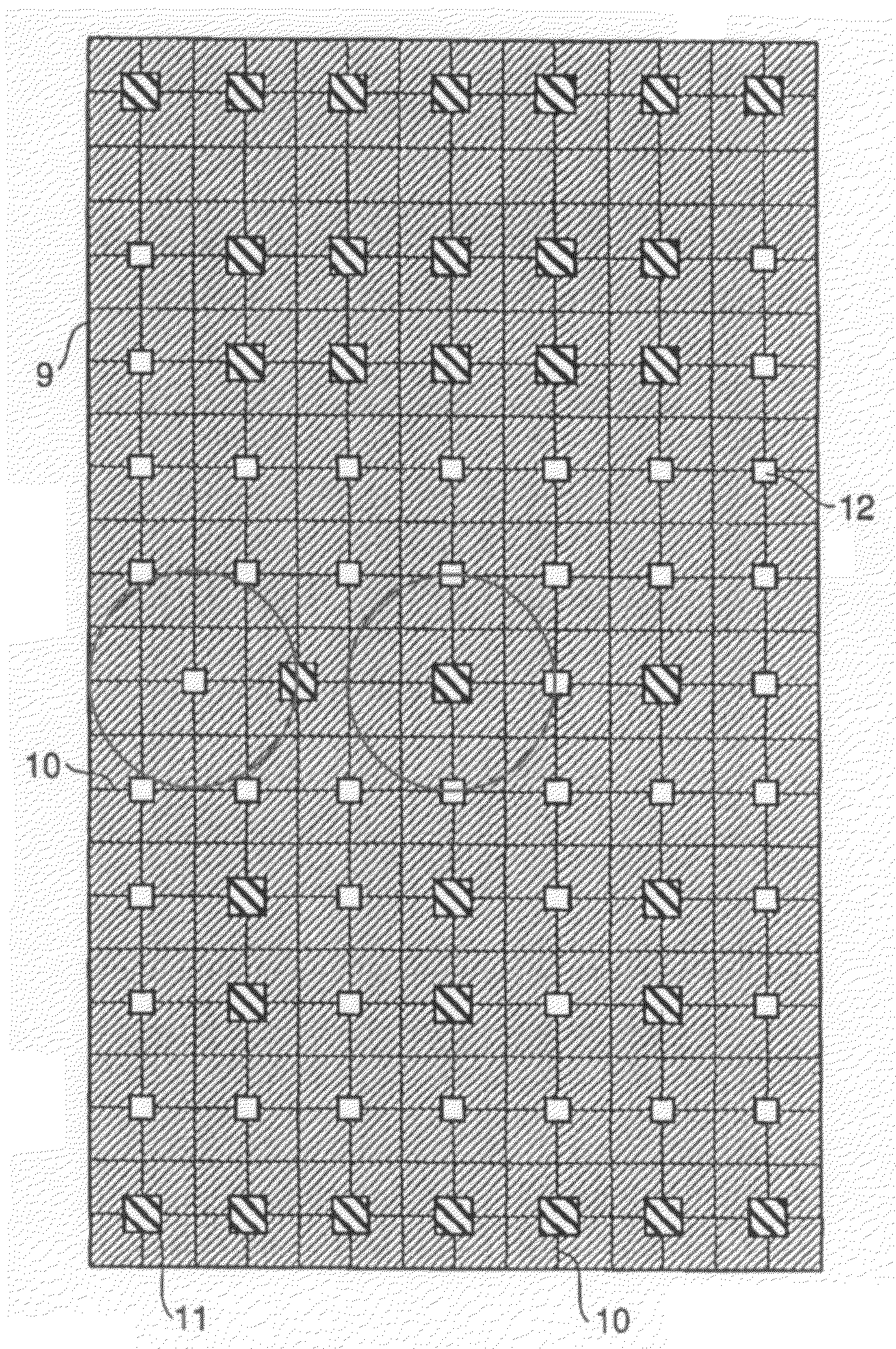

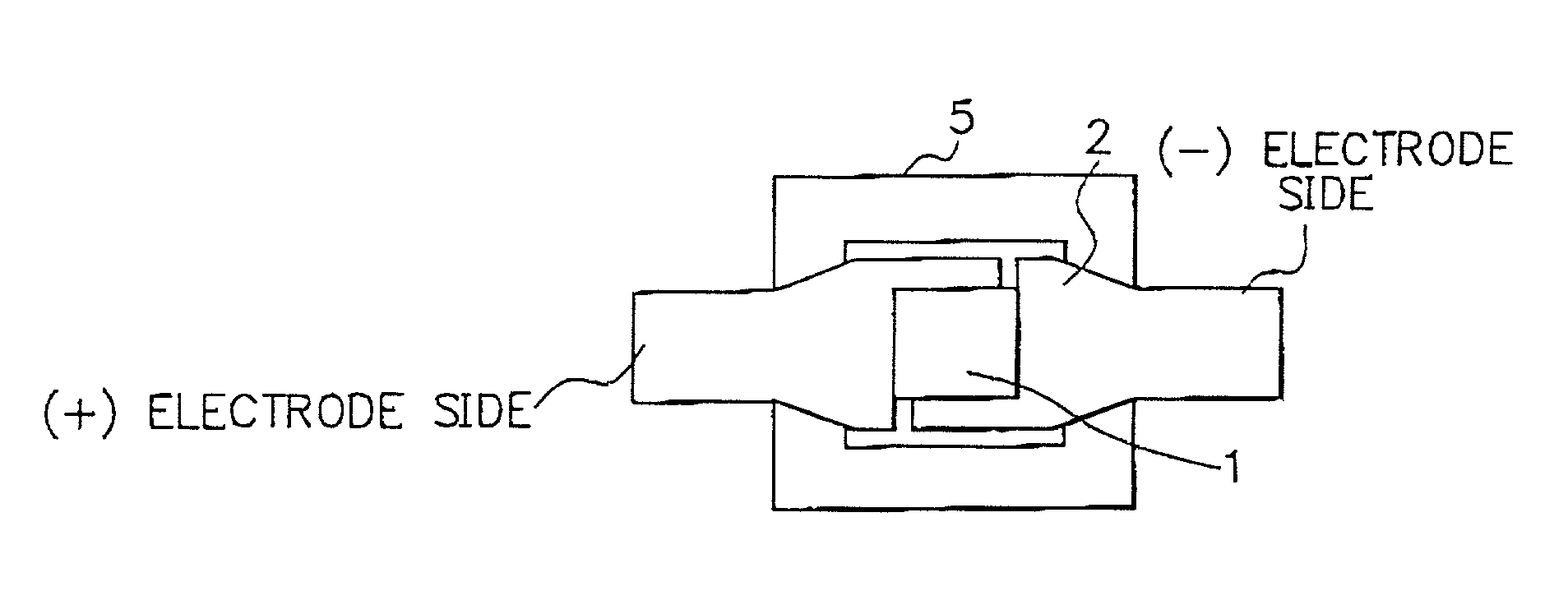

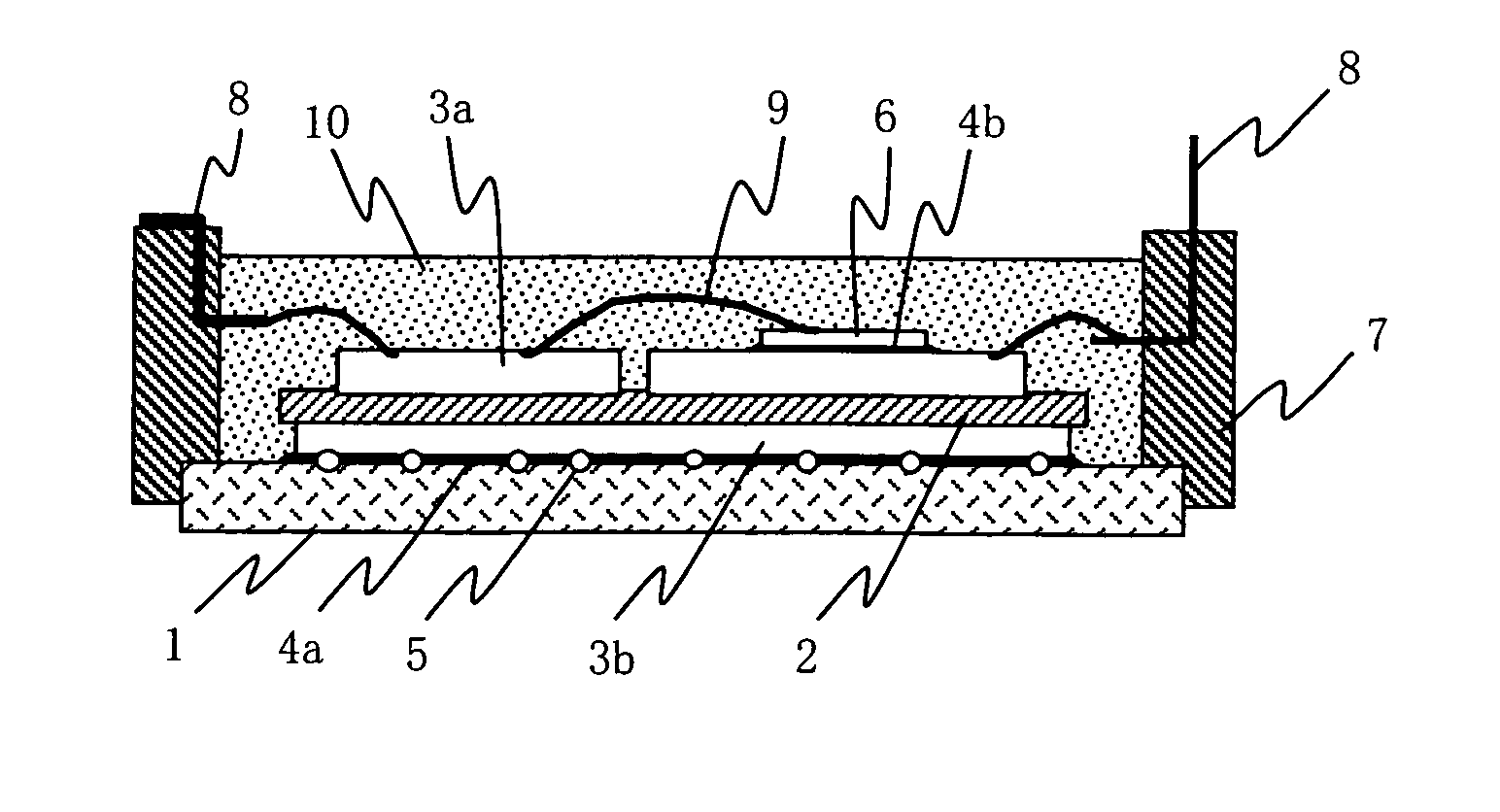

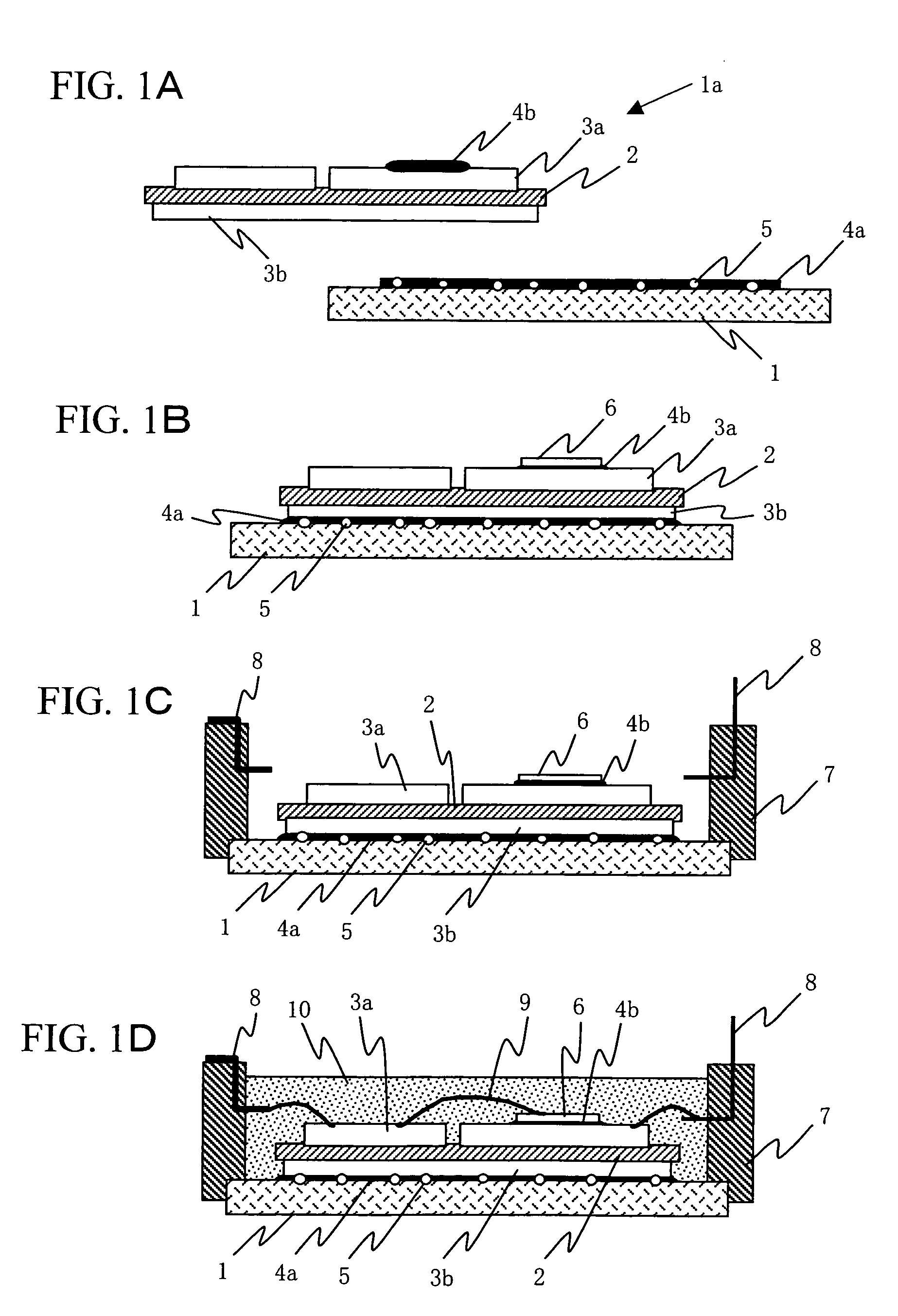

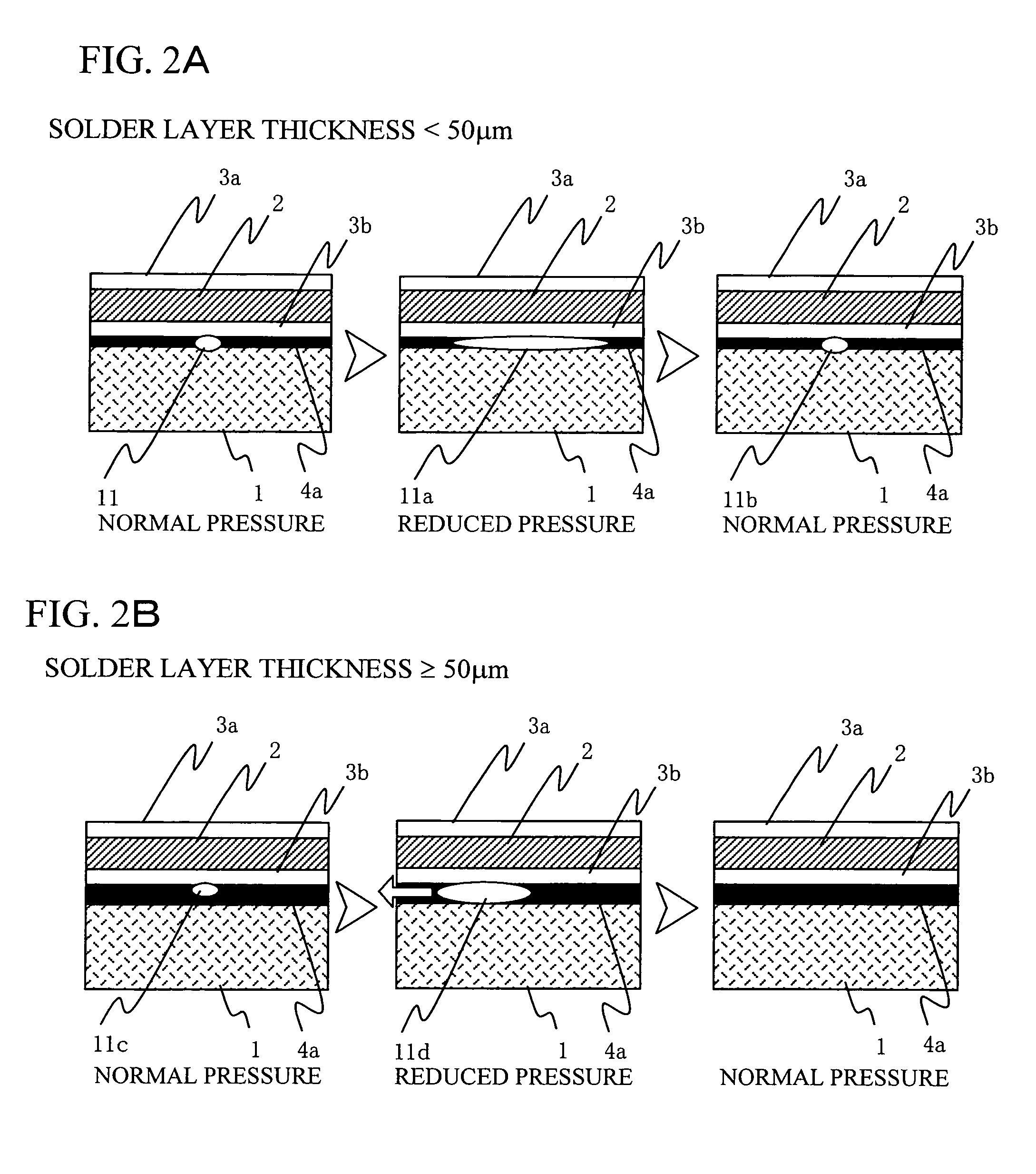

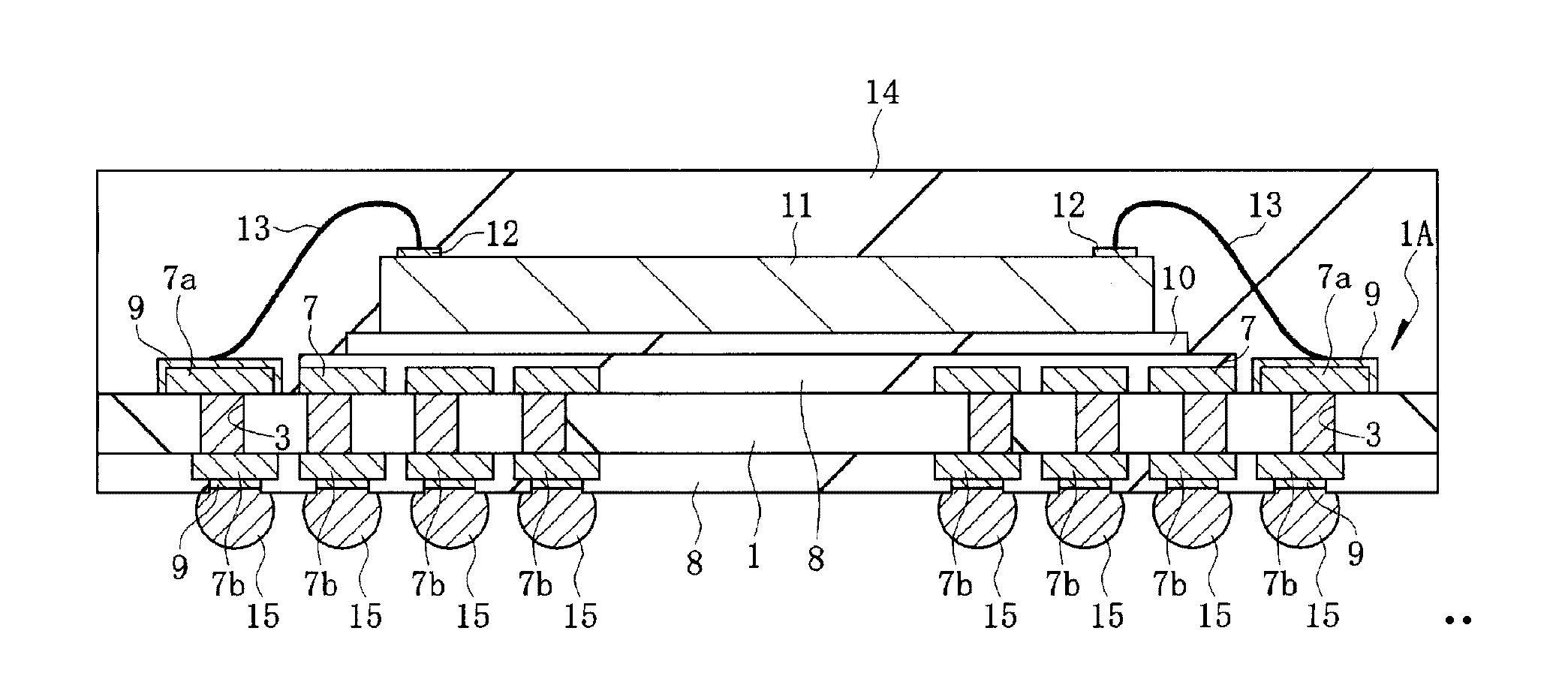

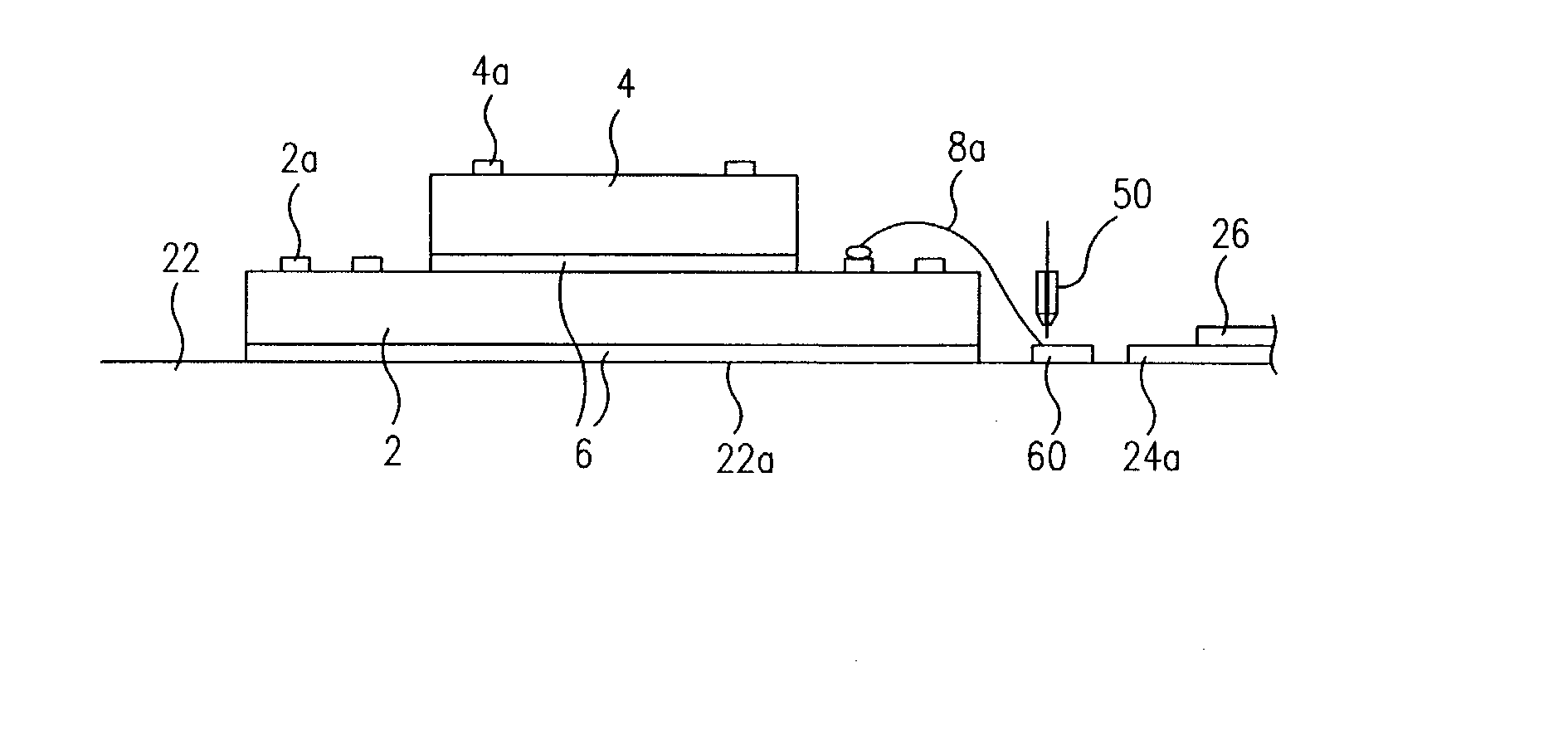

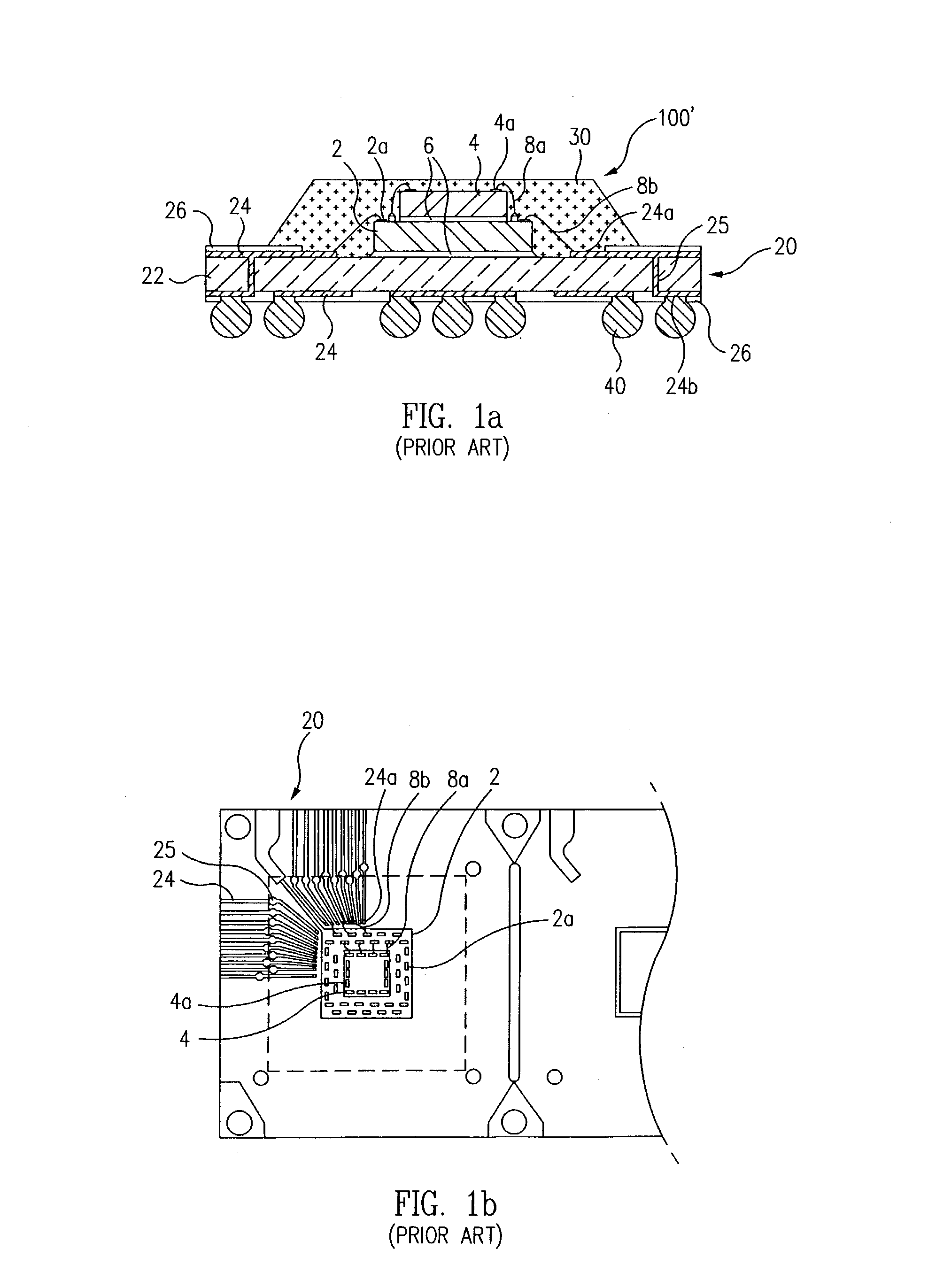

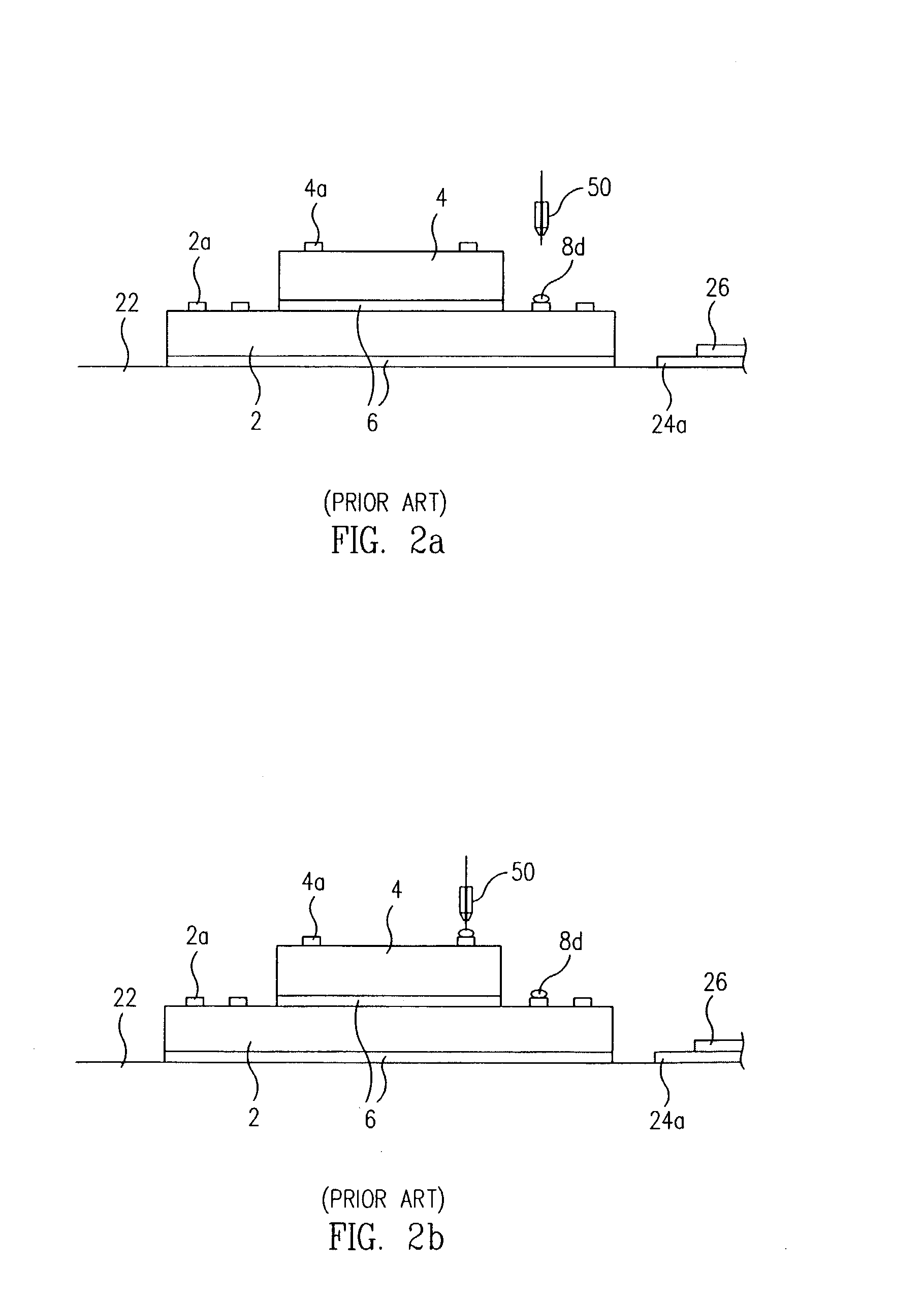

Resin encapsulated semiconductor device and the production method

ActiveUS20050221538A1Easy to moveHigh strength propertiesPrinted circuit assemblingLine/current collector detailsDevice materialSilica gel

A semiconductor device having both high strength and high thermal radiation that is capable of being applied to mounting on automobiles experiencing many thermal cycles, and a manufacturing method thereof are provided. A circuit board 1a for a resin encapsulated semiconductor module device has a configuration where a silicon nitride plate 2 with a thickness of 0.635 mm has copper plates of 1.0 mm and 0.8 mm bonded to both sides thereof via active metal. A copper plate 3a is bonded to the surface side of the silicon nitride plate 2, and a prescribed circuit pattern is formed on the copper plate 3a. Tin-silver-copper cream solder layers 4a and 4b with a thickness of 200 μm are formed at a prescribed location on the circuit pattern 3a on which a semiconductor element 6 is mounted and at a prescribed location of a base plate 1 on which the circuit board 1a is disposed. Nickel particles 5 having a maximum particle size of 100 μm and an average particle size of 70 μm are dispersed in the solder 4a on the base plate 1 of good thermal conductivity. A semiconductor element (chip) 6, the circuit board 1a, and the base plate 1 are disposed on predetermined locations. Thereafter, they are set in a reflow oven (not shown in the drawings) for reflow soldering. After the inside of the reflow oven is replaced by a nitrogen atmosphere, the reflow oven is heated to 280° C. At the time when solder is melted, the inside of the oven is decompressed to 1 Pa, nitrogen is introduced, and the reflow oven is cooled to about room temperature, thereby completing the solder bonding step. After flux is washed, an outer case 7 with an insert-molded outlet terminal 8 is adhered to the base plate 1 and a predetermined connection is conducted via an aluminum bonding wire 9. Then, silicone gel 10 is injected into a package delimited via the base plate 1 and the outer case 7, and the silicone gel 10 is heat-hardened, thereby completing a resin encapsulated semiconductor device A.

Owner:HITACHI LTD +1

Method for manufacturing large-size precise circuit board

ActiveCN104869764AAvoid the problem of line width reductionIncrease exposureMultilayer circuit manufactureGraphicsLine width

The invention relates to the field of circuit board manufacture, specifically a method for manufacturing a large-size precise circuit board. The method employs a mode of two-time exposure, and avoids a problem that a line width of a formed circuit graph is reduced because a height difference at a jointing overlapping part of two films enables the attaching with a plate to be untight. The width of an overlapped region is set as 0.2 mm, and the circuit graph, corresponding to the overlapping region, on the second circuit film is enabled to be 0.05 mm greater than a to-be-manufactured circuit graph, thereby guaranteeing that circuit graphs which are formed in the overlapping region during the first exposure and the second exposure are accurately aligned, and avoiding problems that the exposure of a circuit graph in the overlapped region is poor and the alignment is deflected. The method not only can be used for manufacturing a precise circuit board with a line distance being less than 0.1 mm, but also can be used for manufacturing a circuit board with the length being greater than 914 mm.

Owner:JIANGMEN SUNTAK CIRCUIT TECH

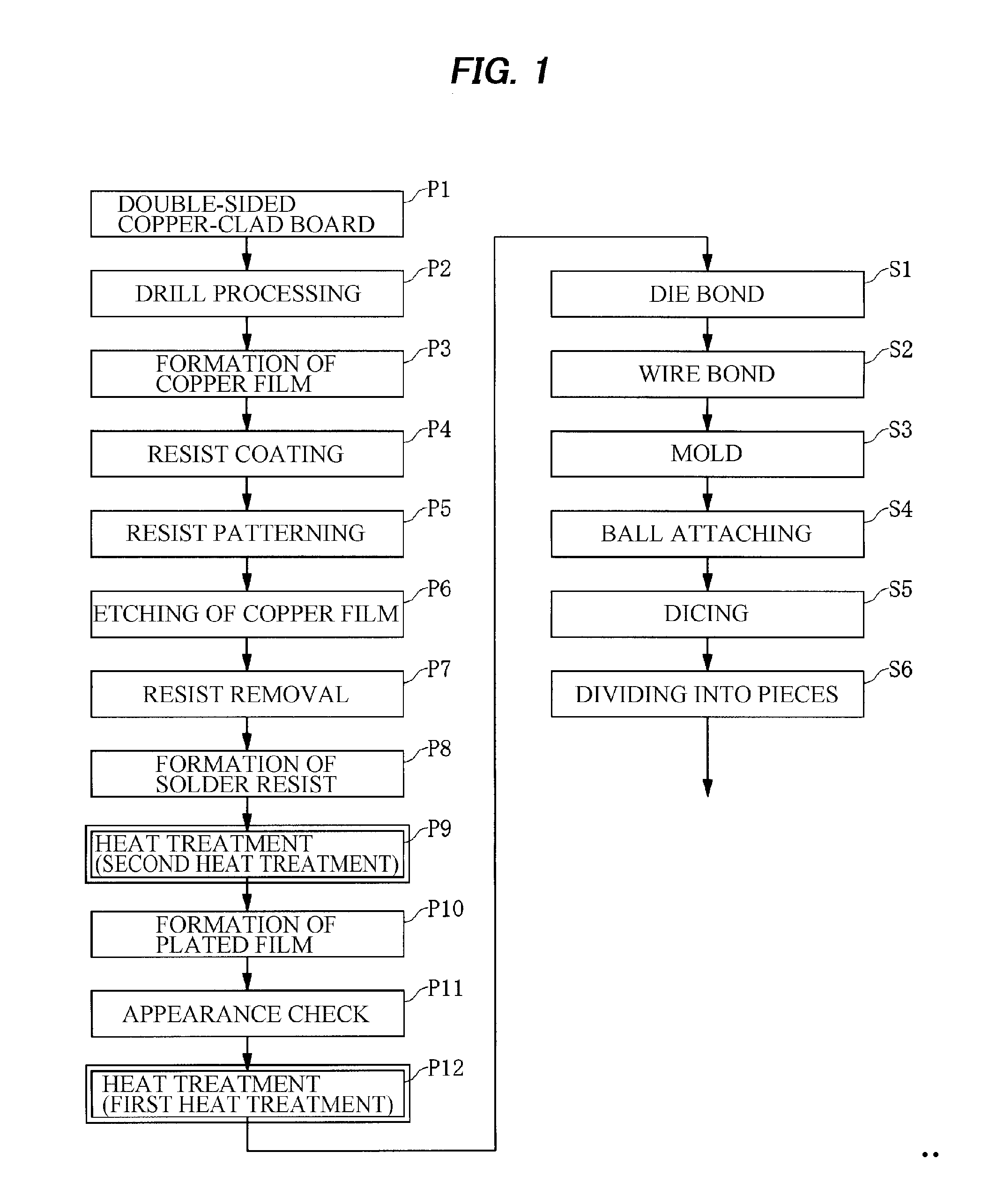

Manufacturing method of semiconductor device

InactiveUS20110201155A1Reliability is deterioratedInhibit deteriorationSemiconductor/solid-state device detailsSolid-state devicesResistOrganic solvent

To provide a technology capable of preventing the deterioration of the reliability of semiconductor devices caused by the gasification of a part of components of the material constituting a wiring substrate.A wiring layer constituting a circuit pattern is formed over each of the front and rear surfaces of a glass epoxy substrate, and after the formation of a solder resist covering the wiring layer while exposing a part of the wiring layer and prior to a heat treatment (first heat treatment) at 100° C. to 150° C. for dehumidification, a heat treatment (second heat treatment) at 160° C. to 230° C. for gasifying and discharging an organic solvent contained in the material constituting a wiring substrate is performed for the wiring substrate.

Owner:RENESAS ELECTRONICS CORP

Manufacturing method for flexible and hard combined thin PCB

ActiveCN102573328ASo as not to damageNo damagePrinted circuit assemblingTectorial membraneCopper foil

The invention discloses a manufacturing method for a flexible and hard combined thin PCB, and is characterized by comprising the steps as follows: a) a flexible board with a circuit graphs on the surface thereof is provided; b) a protective film is arranged on the surface of the flexible board provided with the circuit graphs; c) prepregs with windows are provided, the prepregs are stacked on the surface of the flexible plate, and the protective film corresponds to the position of the windows of the pregregs; d) hard boards are provided and stacked on the surfaces of the prepregs, and the prepregs are located among the flexible board and the hard boards; e) the laminating is carried out; and f) the parts of the hard boards corresponding to the position of the protective film are removed. The invention has the benefits that a first hard board and a second hard board located on the most outer layers of the thin PCB can only adopt copper foil, and the problem that an etching solution provided by the copper foil damages the circuit graphs on the flexible board is solved, so that the manufacturing of thinner PCBs is achieved; and after manufacturing the flexible plate, a protective layer is not required before manufacturing the flexible and hard combined thin PCB, and the procedure of the manufacturing is simplified.

Owner:SHANGHAI MEADVILLE ELECTRONICS

Wire bonding method for a semiconductor package

InactiveUS20030199118A1Semiconductor/solid-state device detailsSolid-state devicesLead bondingSemiconductor chip

Owner:AMKOR TECH SINGAPORE HLDG PTE LTD