Wafer test system and method for TOF chip

A wafer testing and chip technology, which is used in radio wave measurement systems, electronic circuit testing, electrical measurement, etc., and can solve problems such as large redundancy in functions, complex hardware and software structures, and inextensibility.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0039] In order to make the purpose, technical solution and advantages of the present application clearer, the present application will be further described in detail below in conjunction with the accompanying drawings and embodiments. It should be understood that the specific embodiments described here are only used to explain the present application, and are not intended to limit the present application.

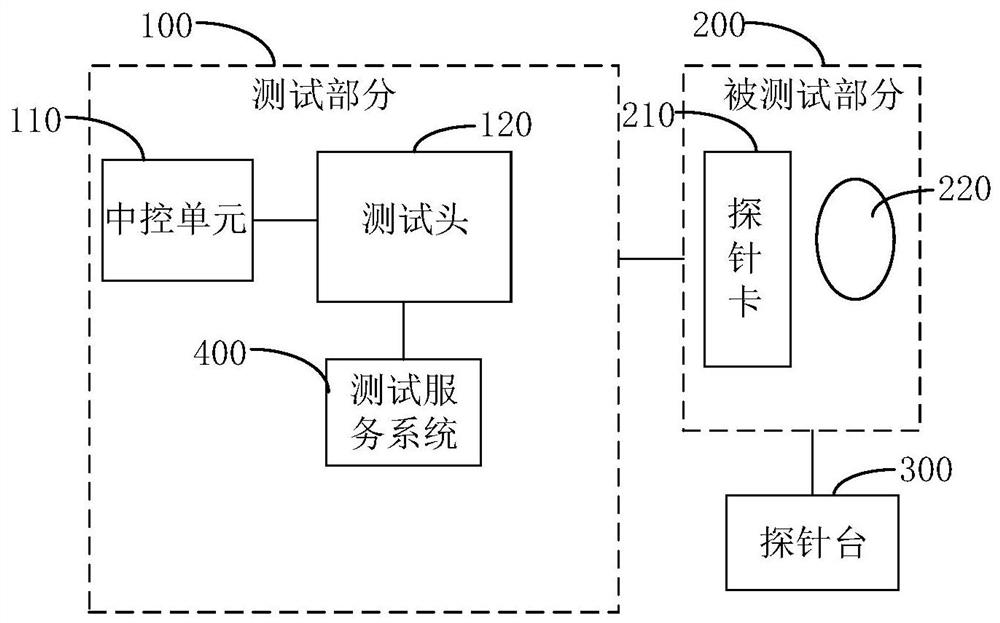

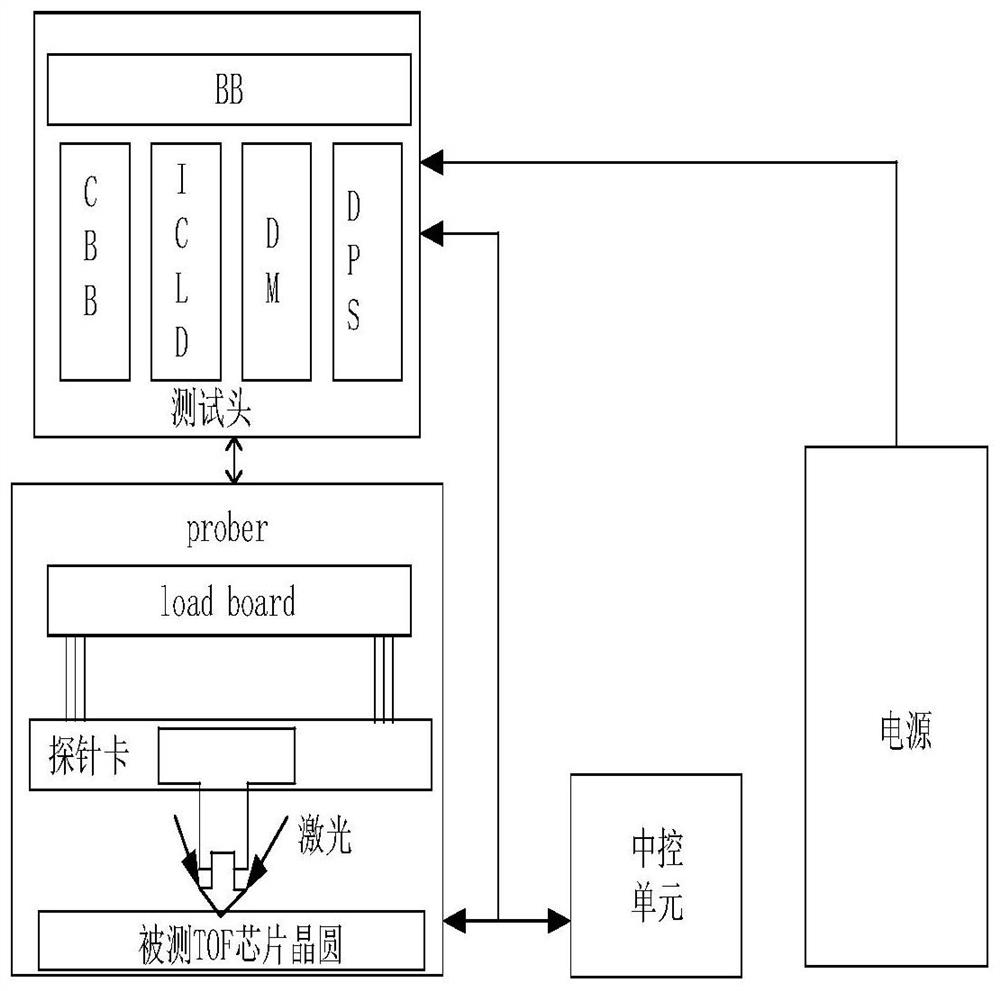

[0040] In one embodiment, such as figure 1 As shown, a wafer testing system for a TOF chip provided by the present invention mainly includes: a testing part 100, a tested part 200, and a probe station 300; wherein, the testing part 100 may include a central control unit 110 and a testing head 120; The tested part 200 may include a probe card 210 and a tested TOF chip wafer 220 .

[0041] Wherein, the probe card 210 can be connected with the probe station 300, and several contacts can be arranged on the probe card 210. Specifically, the number of contacts on the probe card...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More