Interconnection system

A technology of interconnection system and interconnection interface, applied in the direction of response error generation, resource allocation, program control design, etc., can solve problems such as bandwidth inconsistency, data congestion, transmission bandwidth not being fully utilized, etc., and achieve low latency , high space utilization, and high bandwidth utilization

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0042] The following description lists various embodiments of the present invention, but is not intended to limit the content of the present invention. The actual scope of the invention is defined by the scope of the patent application.

[0043] In the various embodiments listed below, the same or similar elements or components will be denoted by the same reference numerals.

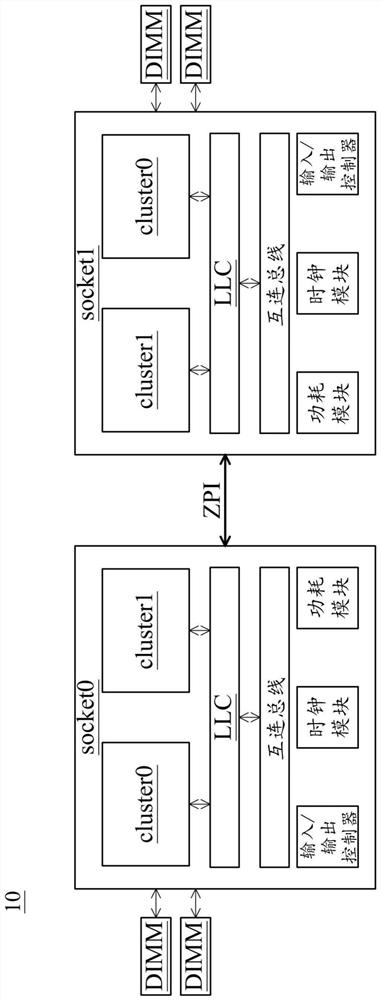

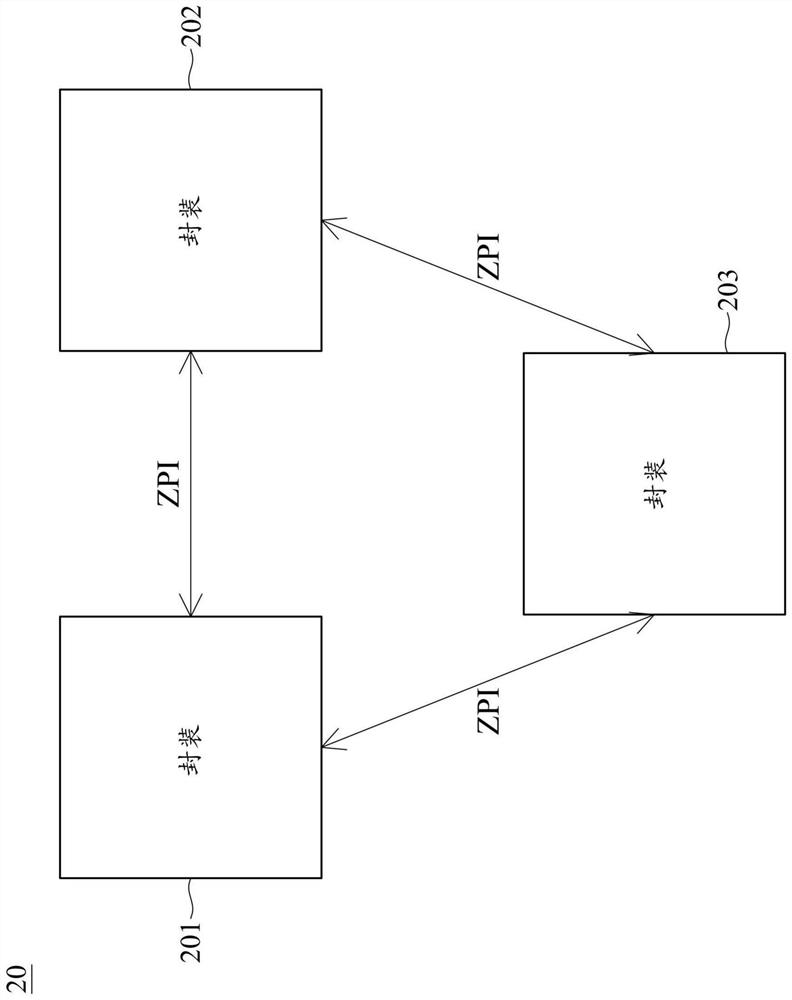

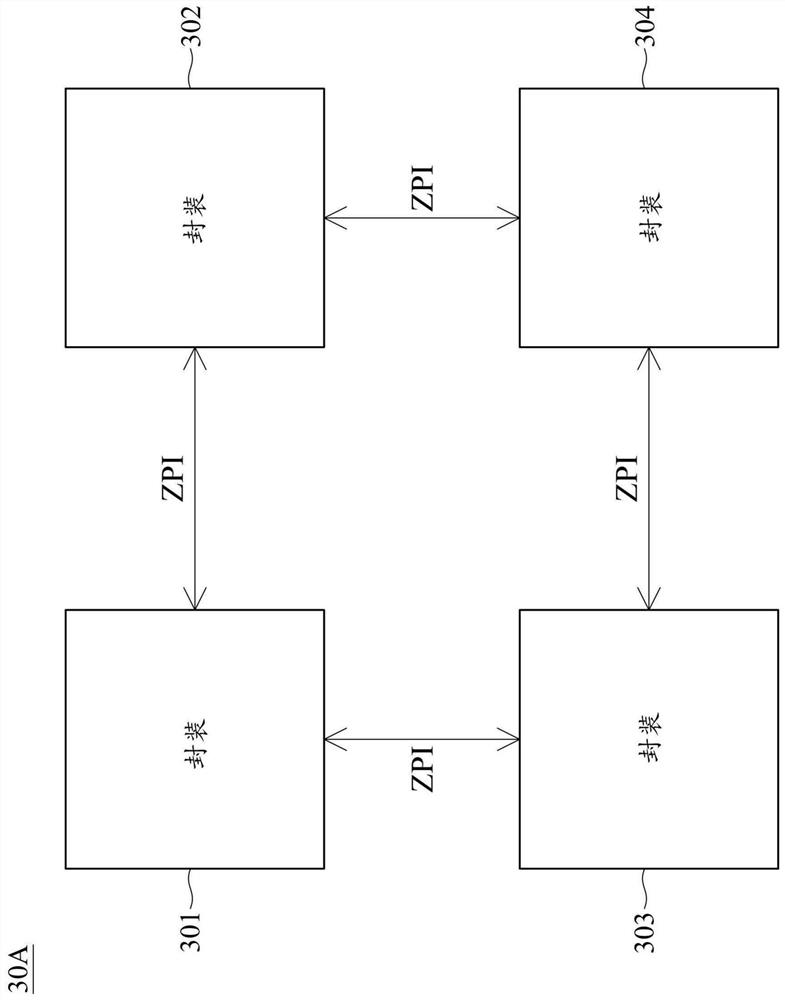

[0044] The invention discloses a cross-chip interconnection system, which includes a plurality of packages and interconnection interfaces between the packages, and the packages are arranged to communicate with each other through the first interconnection interface. The following description will refer to the first interconnection interface as ZPI.

[0045] figure 1 It is a structural schematic diagram of an example system 10 shown according to an embodiment of the present invention. Such as figure 1 As shown, system 10 contains two packages: socket0 and socket1, and a ZPI between them. Encapsulation...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com