Device and method for realizing cross-clock-domain time domain convolution calculation based on FPGA (Field Programmable Gate Array)

A technology across clock domains and computing devices, applied in the application field of programmable devices, can solve problems such as high delay and low real-time performance, and achieve the effect of reducing delay and improving real-time performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

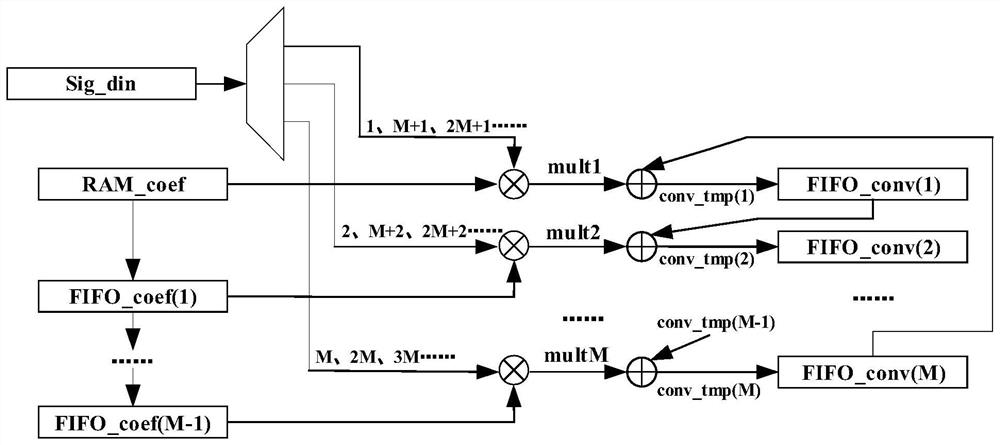

[0046] This embodiment proposes an FPGA-based time-domain convolution calculation device across clock domains.

[0047] The convolution calculation principle is:

[0048]

[0049] In the formula, h[n] is the convolution coefficient, and x[n] is the signal to be convolved. It can be seen from the formula:

[0050] 1) The convolution calculation process is mainly multiplication and addition calculations.

[0051] 2) Each signal to be convolved will perform a multiplication calculation with all coefficients.

[0052] 3) The current output value is related to the historical input value.

[0053] In order to achieve the maximum number of multiplexing of multipliers and adders, it is necessary to complete the multiplication and addition of a signal at the fastest speed. After the multiplier and adder complete the calculation of a signal, they can be used to complete the calculation of other signals. . At the same time, in order to reduce the accumulation of intermediate calcul...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com