Semiconductor structure and forming method thereof

A technology of semiconductor and metal interconnection structure, applied in the direction of semiconductor device, semiconductor/solid-state device manufacturing, semiconductor/solid-state device components, etc., can solve the problems affecting the electrical performance of the device and so on

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

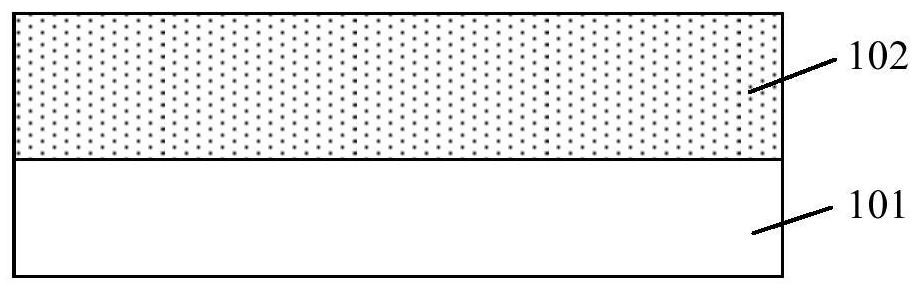

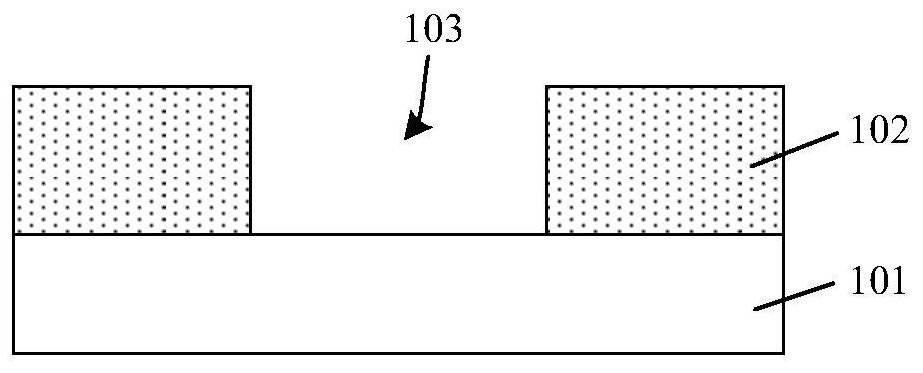

[0053] The specific implementation manners of the present application will be described in detail below in conjunction with the accompanying drawings. When describing the embodiments of the present application in detail, for the convenience of explanation, the schematic diagrams will not be partially enlarged according to the general scale, and the schematic diagrams are only examples, which should not limit the protection scope of the present application. In addition, the three-dimensional space dimensions of length, width and depth should be included in actual production.

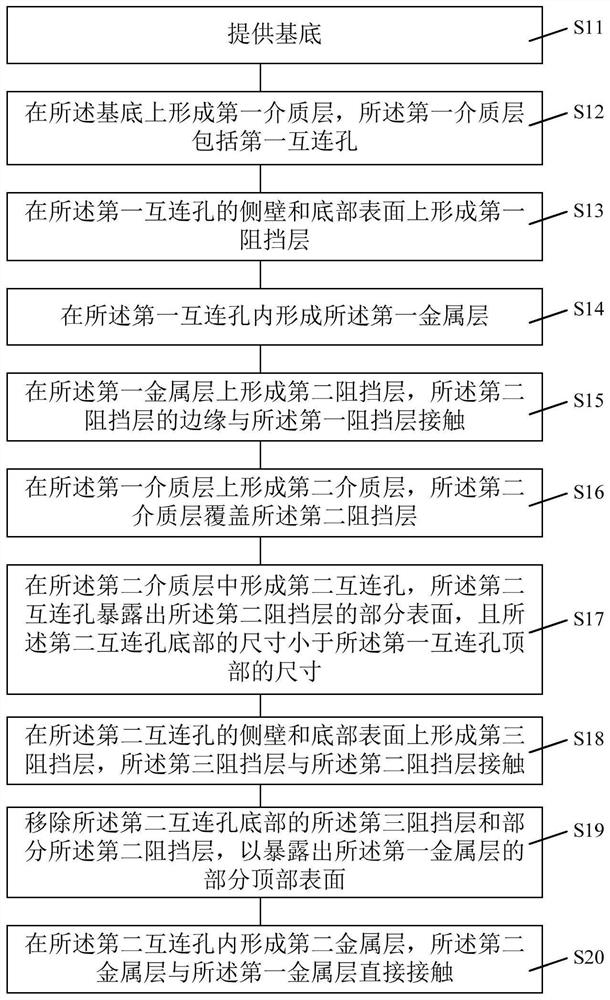

[0054] refer to figure 1 , some embodiments of the present application provide a method for forming a semiconductor structure, including the steps of:

[0055] Step S11, providing a substrate;

[0056] Step S12, forming a first dielectric layer on the substrate, the first dielectric layer including first interconnection holes;

[0057] Step S13, forming a first barrier layer on the sidewall and bottom ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More