Anti-interference channel demodulation accelerator suitable for satellite baseband processing chip

A baseband processing and channel demodulation technology, applied in radio transmission systems, electrical components, transmission systems, etc., can solve the problem of lack of baseband accelerators for discrete multi-subcarrier anti-interference channel demodulation tasks, and achieve resource saving and low power consumption. Effects of balancing requirements, performance, and resource optimization

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

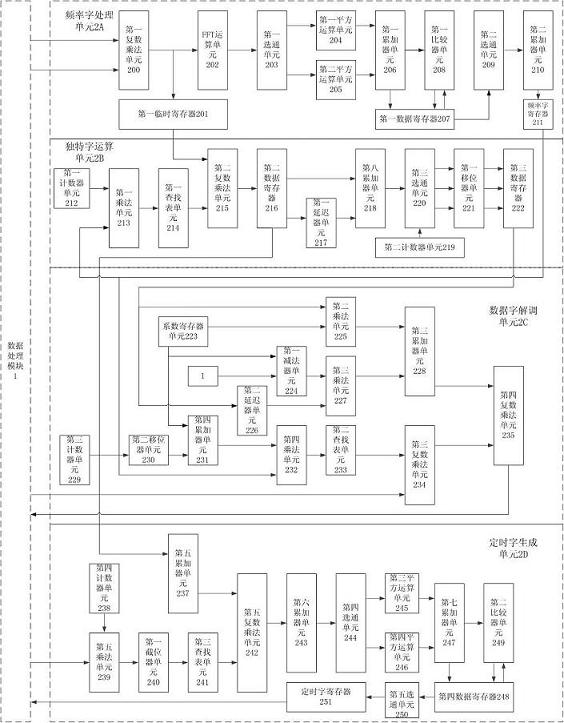

[0030] Below in conjunction with accompanying drawing, the present invention is further explained and illustrated.

[0031] Such as figure 1 As shown, an anti-interference channel demodulation accelerator suitable for satellite baseband processing chips includes a data processing module 1, an algorithm processing module 2, a control information register 3 and a data information register 4;

[0032] The data processing module 1 is used to analyze the multi-user control parameters sent by the control information register 3 under the control of the accelerator integrated controller, complete parameter processing, channel identification and data formatting operations, generate local data, and analyze the data information The multi-user data information sent by the register 4 is accessed, and the user data extracted on demand, locally generated data and formatted control information are output to the algorithm processing module 2; The demodulation results and timing word results a...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More