Packaging structure and packaging method of semiconductor chip

A packaging structure and packaging method technology, applied in the direction of semiconductor devices, semiconductor/solid-state device manufacturing, semiconductor/solid-state device components, etc., can solve the problem of affecting the strength and durability of the metal wire layer structure, and increase the stress concentration of the metal wire layer. , destroying the reliability of the chip packaging structure, etc., to ensure the structural strength and durability, reduce the number of inflection points, and ensure the functionality and service life.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

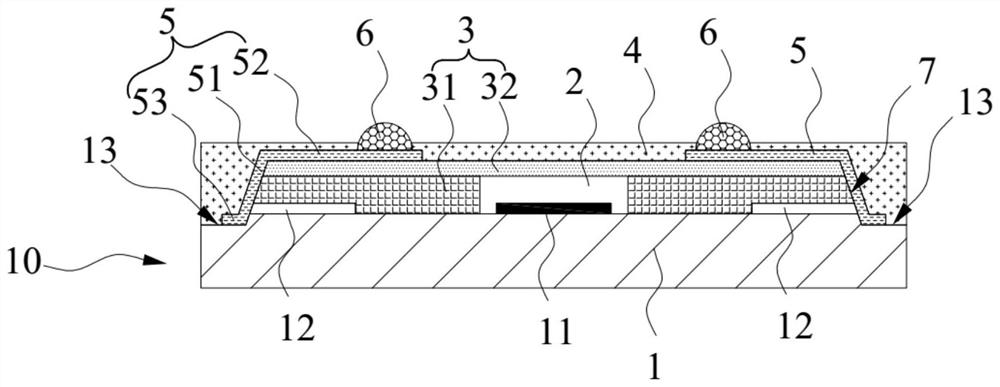

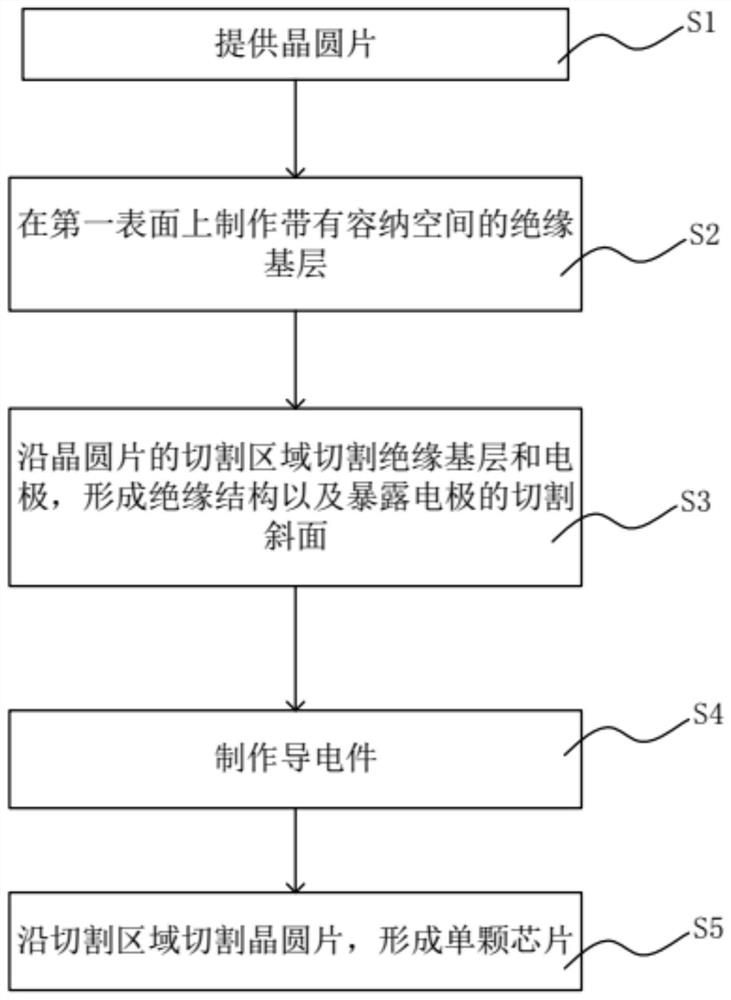

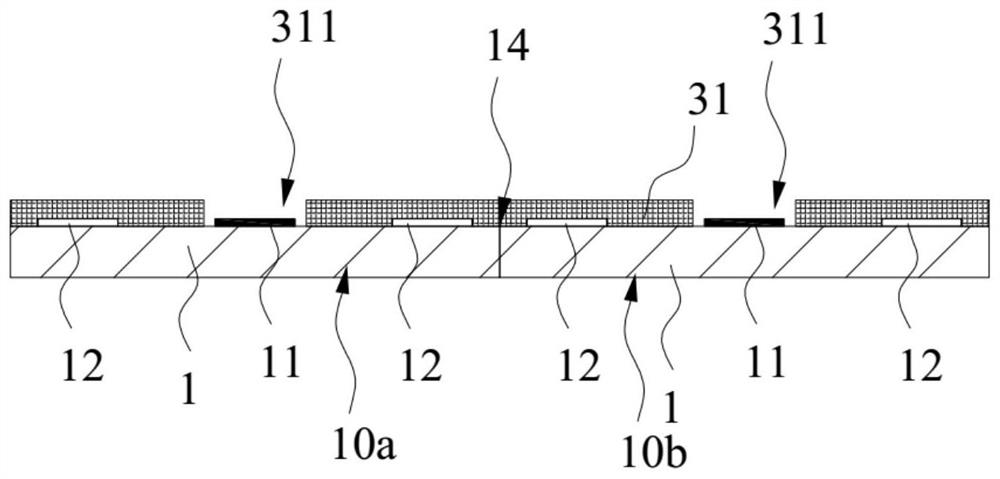

Embodiment Construction

[0047]In order to make the technical problems solved by the present invention, the technical solutions adopted and the technical effects achieved clearer, the technical solutions of the embodiments of the present invention will be further described in detail below in conjunction with the accompanying drawings. Obviously, the described embodiments are only the technical solutions of the present invention. Some, but not all, embodiments. Based on the embodiments of the present invention, all other embodiments obtained by those skilled in the art without making creative efforts belong to the protection scope of the present invention.

[0048] In the description of the present invention, unless otherwise clearly specified and limited, the terms "connected", "connected" and "fixed" should be understood in a broad sense, for example, it can be a fixed connection, a detachable connection, or an integrated ; It can be a mechanical connection or an electrical connection; it can be a di...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| height | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More