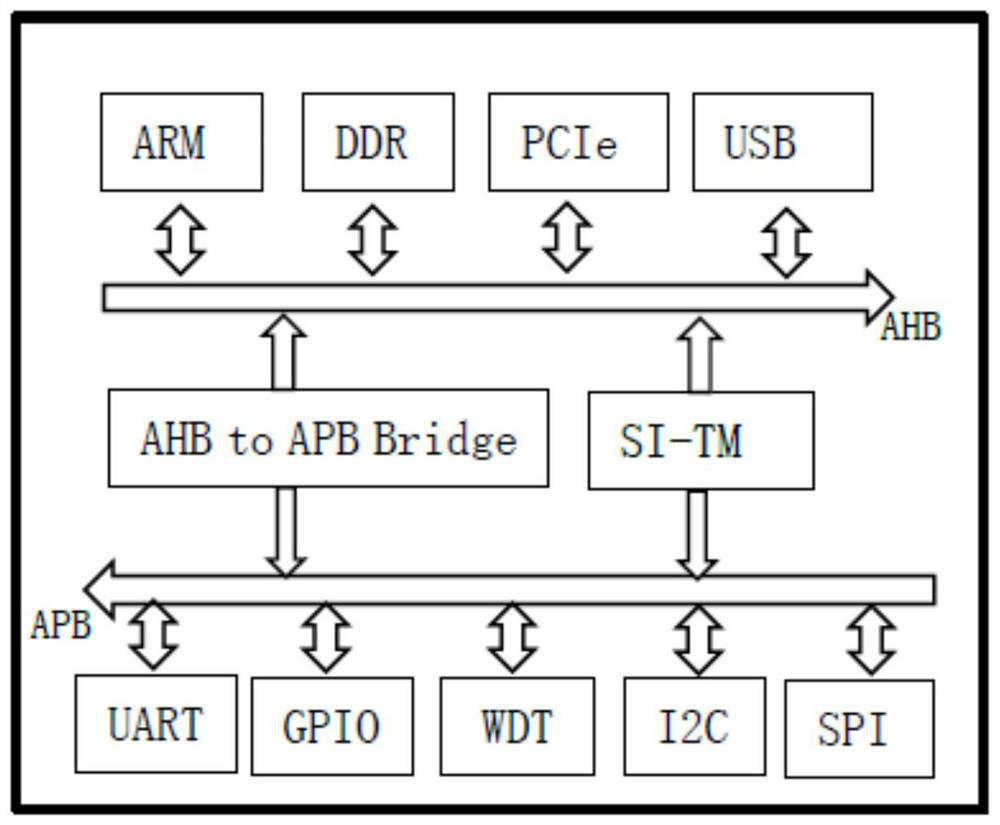

Chip architecture and signal integrity test method

A signal integrity and chip technology, used in digital circuit testing, electronic circuit testing, architecture with a single central processing unit, etc., can solve the problem caused by the inability to determine the signal integrity of the chip, the inability to check whether there is a problem inside the chip, and the inability to adjust problems such as external motherboard links, to achieve the effect of low test cost, ensure signal integrity, and simple and fast process

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

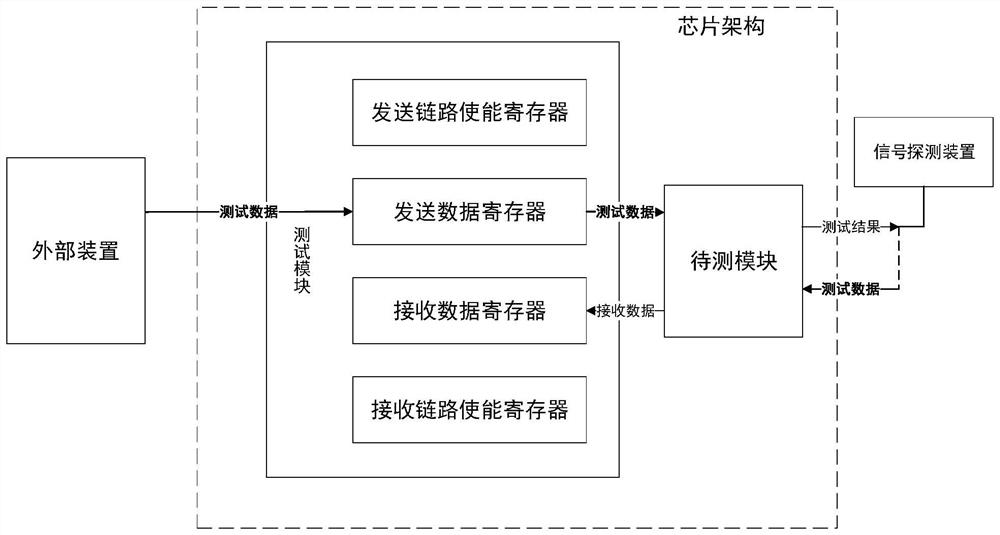

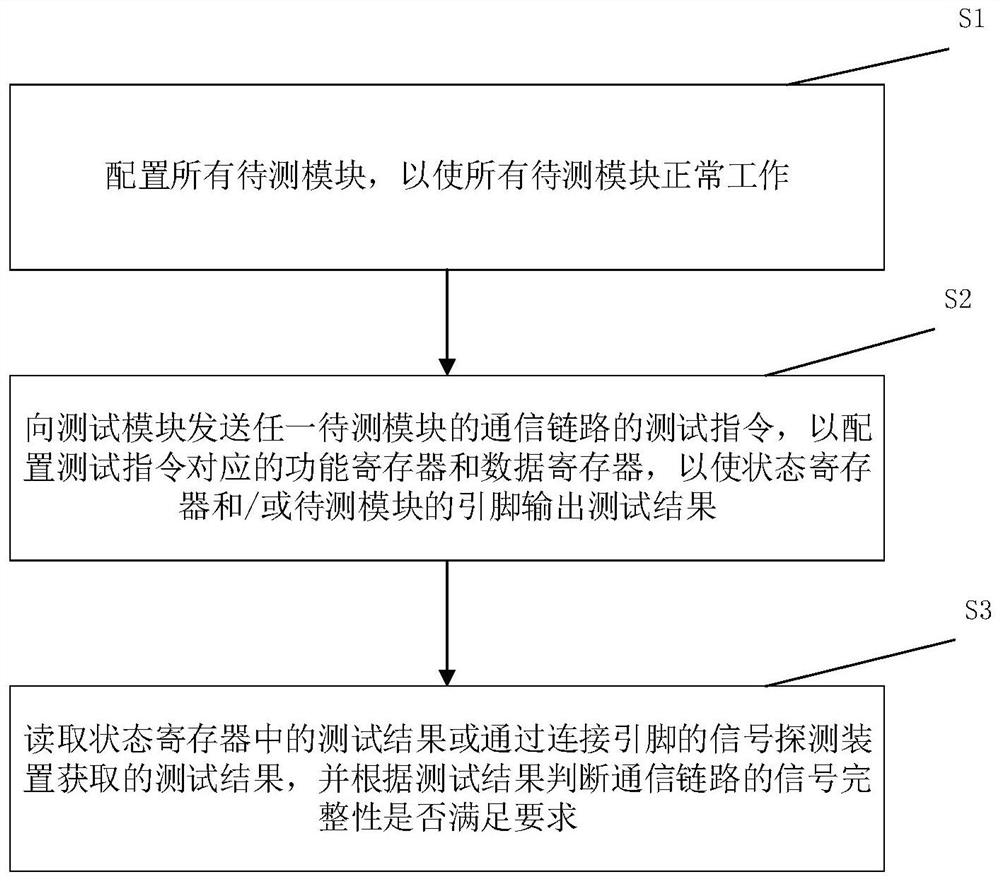

[0045] The following will clearly and completely describe the technical solutions in the embodiments of the present invention with reference to the accompanying drawings in the embodiments of the present invention. Obviously, the described embodiments are only some, not all, embodiments of the present invention. Based on the embodiments of the present invention, all other embodiments obtained by persons of ordinary skill in the art without making creative efforts belong to the protection scope of the present invention.

[0046] Signal integrity testing is different from wafer testing and FT testing. Generally, the entire link is tested during chip operation after the chip is installed on the motherboard. This test method relies on the mutual support between the motherboard and the chip, but since the range of the communication link obviously extends beyond the scope of the original chip, even if there is a problem with the communication link, it is impossible to determine wheth...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More