Test method of memory device implemented in multi-chip package (MCP) and method of manufacturing MCP including test method

A chip mounting and memory controller technology, applied in semiconductor/solid-state device testing/measurement, information storage, static memory, etc., can solve the problems of reduced productivity of MCP testing

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

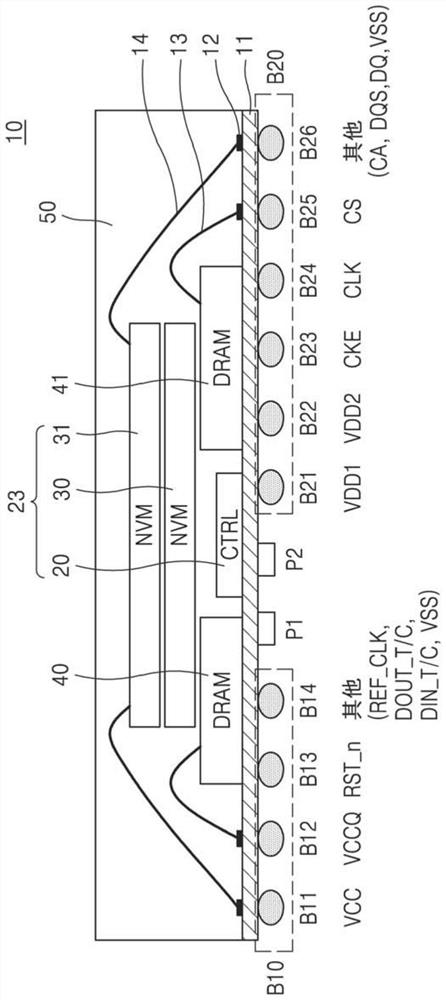

[0025] figure 1 is a diagram illustrating an example of implementing a memory device in a multi-chip package (MCP) 10 according to an embodiment of the inventive concept. Hereinafter, the terms "MCP 10" and "storage device 10" may be used interchangeably.

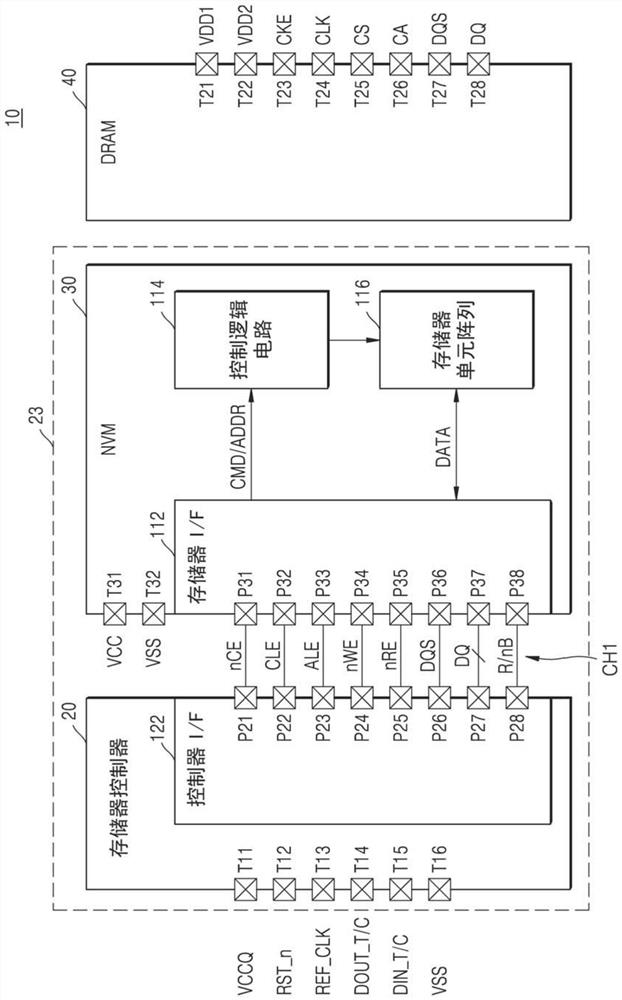

[0026] refer to figure 1 , the MCP 10 includes a package substrate 11, a memory controller chip 20, non-volatile memory (NVM) chips 30 and 31, DRAM chips 40 and 41, first wires 13, second wires 14, external connection terminals B11 to B14, P1 and P2 and B21 to B26 , and the molding layer 50 . Here, the external connection terminals B11 to B14, P1 and P2, and B21 to B26 may be referred to as package terminals or package balls. exist figure 1 In the MCP 10, two NVM chips 30 and 31 and two DRAM chips 40 and 41 are shown, but the inventive concept is not limited thereto, and other configurations are also possible. For example, MCP 10 can include 2 n NVM chips (n is a natural number equal to or greater than 0) and one or m...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More