Mean noise reduction rapid processing circuit and method suitable for image sensor

An image sensor and processing circuit technology, applied in the field of image sensors, can solve problems such as motion afterimages, time difference, and time growth, and achieve the effects of improving image quality, reducing frame selection, and fast processing

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

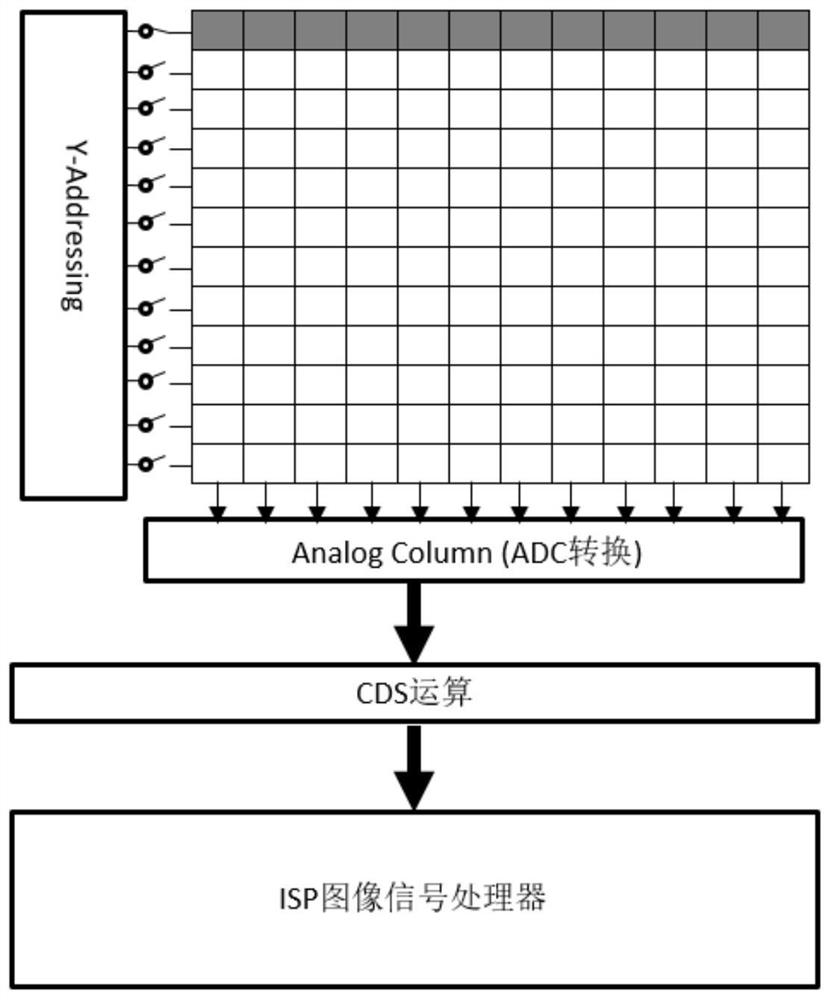

[0060] Such as Figure 1 to Figure 8 As shown, the present invention is suitable for an average noise reduction fast processing circuit of an image sensor, comprising a CDS operation circuit for controllable addition and subtraction, the input end of the CDS operation circuit for controllable addition and subtraction is connected to an ADC conversion circuit, The first output end of the CDS operation circuit of the controllable addition and subtraction is connected to the input end of the CDS operation circuit of the controllable addition and subtraction, and the second output end of the CDS operation circuit of the controllable addition and subtraction is connected to the to the ISP image signal processor;

[0061] The CDS operation circuit of the controllable addition and subtraction method is used to realize the form of cyclic addition and subtraction operation combination to realize the sum of multiple sampling CDS voltage differences when a frame of image pixels is read o...

Embodiment 2

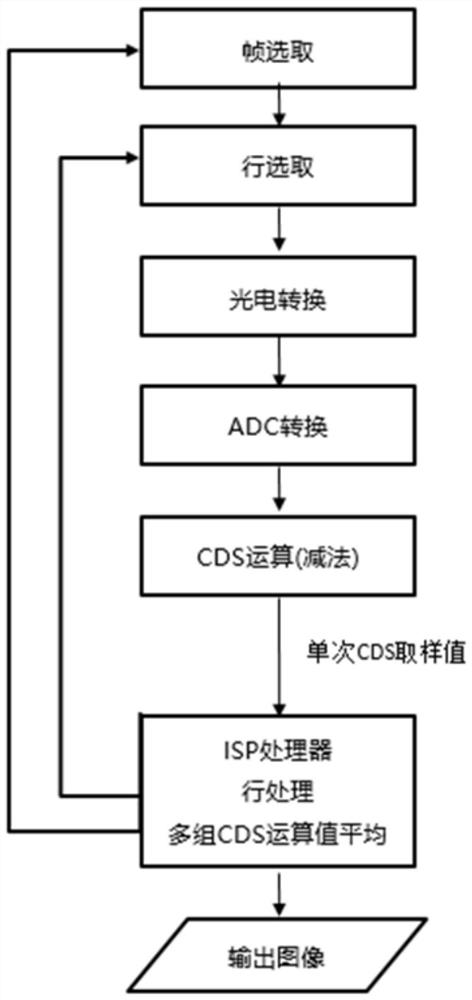

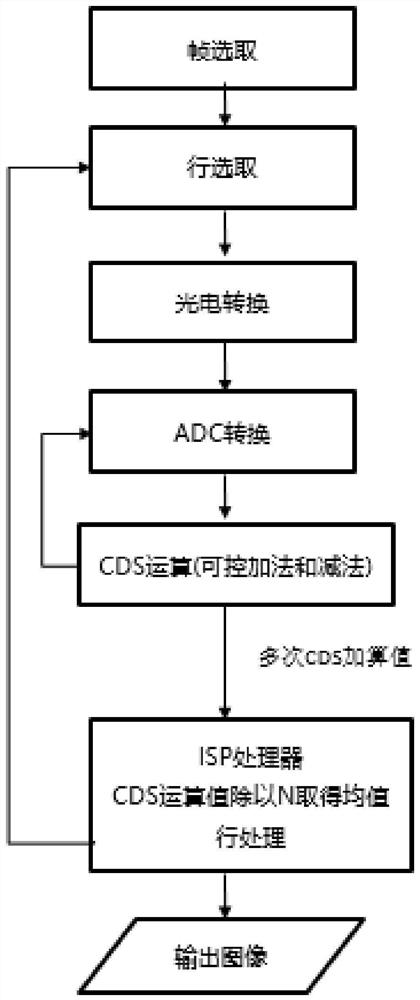

[0096] Such as Figure 1 to Figure 8 As shown, the difference between this embodiment and Embodiment 1 is that this embodiment provides a fast processing method for mean value noise reduction suitable for image sensors, such as image 3 As shown, the method includes:

[0097] Use the image sensor for frame selection to obtain a frame of image;

[0098] Line selection is carried out from a frame of image acquired, and for a line of pixels, the controllable addition and subtraction CDS operation circuit is used to realize the form of cyclic addition and subtraction operation combination, so that multiple sampling CDS voltages can be obtained when the same line of pixels is read out The sum of differences; wherein, the CDS operation circuit of the controllable addition and subtraction adopts a fast processing circuit for mean value noise reduction suitable for image sensors described in Embodiment 1;

[0099] According to the obtained sum of multiple sampling CDS voltage differ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More