Semiconductor memory cell fabrication method

A technology of storage unit and manufacturing method, which is applied in semiconductor/solid-state device manufacturing, semiconductor devices, transistors, etc., and can solve the problems that the field oxide film endangers the isolation characteristics of devices, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0027] A method of manufacturing a semiconductor memory cell of the present invention will now be described with reference to the accompanying drawings.

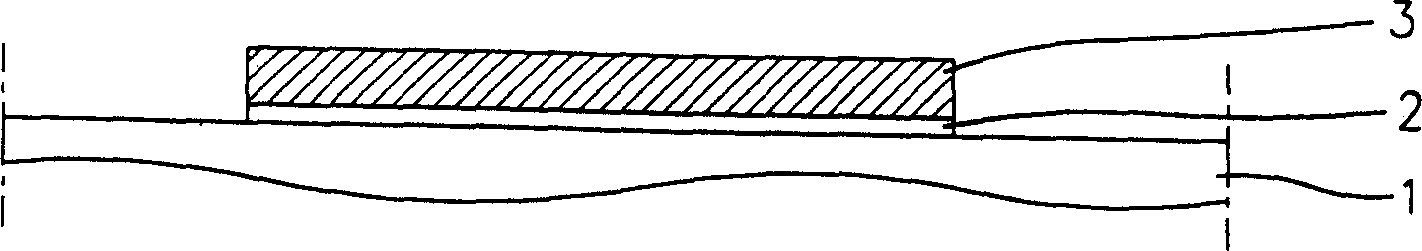

[0028] First, if Figure 3A As shown, a base oxide film 12 and a nitride film 13 are sequentially deposited on a semiconductor substrate 11 and patterned.

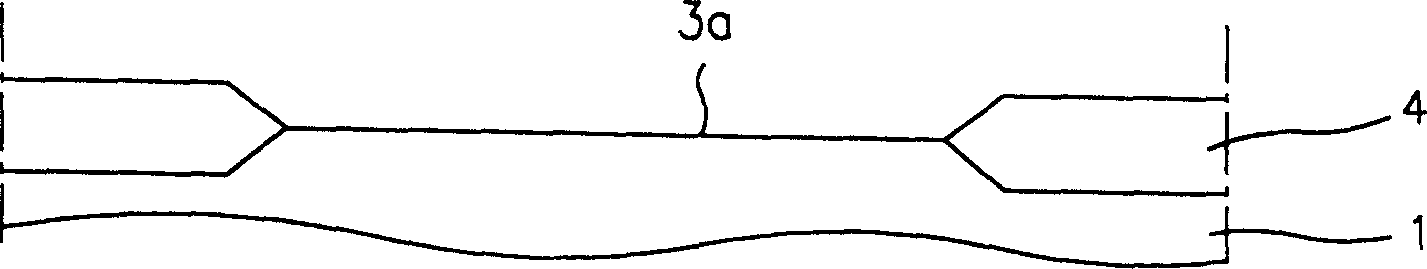

[0029] Such as Figure 3B As shown, using the patterned oxide film 12 and nitride film 13 as a mask, the field oxide film 14 is formed by using the LOCOS method, and then the patterned oxide film 12 and nitride film 13 are removed to expose the active region 13a , the field oxide film 14 has a beak portion adjacent to the active region.

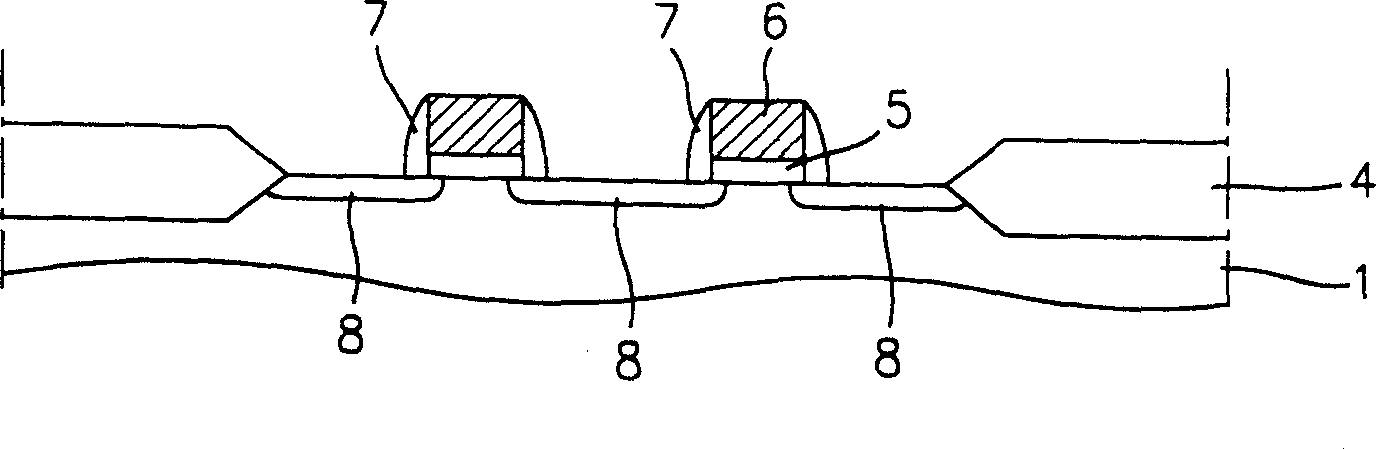

[0030] see Figure 3C , implanted N into the semiconductor substrate 11 - ions to form a through-hole stop region 11a and a field stop region 11b inside the substrate 1, respectively. Then, the bird's beak portion 14a of the field oxide film 14 is removed by wet etching. Next, a gate oxide film 15 and gate polysilicon are deposite...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com