Ethernet exchange chip output queue management and dispatching method and device

A technology for outputting queues and switching chips, applied in data exchange networks, data exchange through path configuration, transmission systems, etc., can solve problems affecting queue resource usage, inability to provide service quality, data frame selection and discarding, etc., to improve practicality. The effect of low cost, low cost and mutual influence reduction

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0043] Below according to accompanying drawing and embodiment the present invention will be described in further detail:

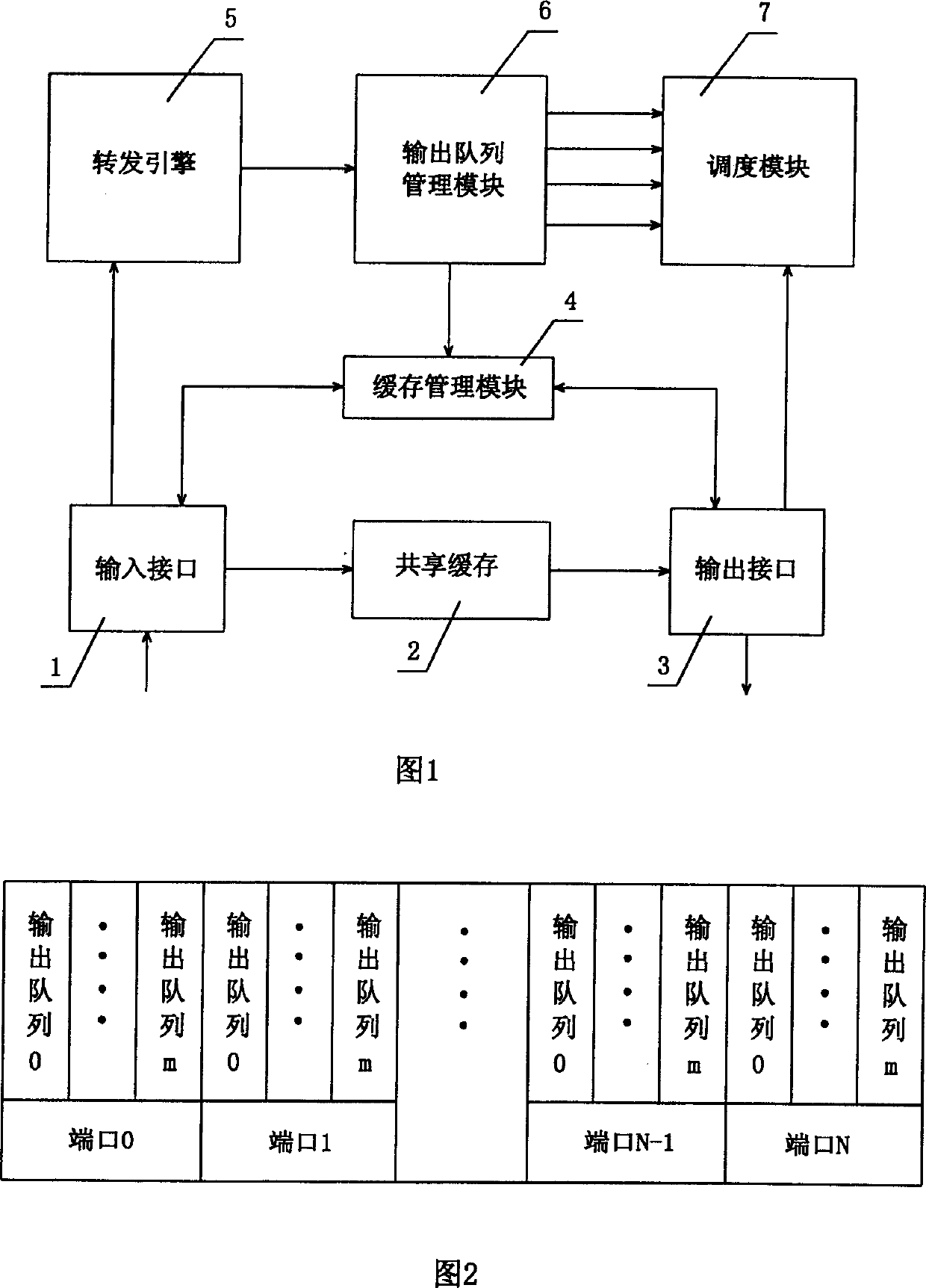

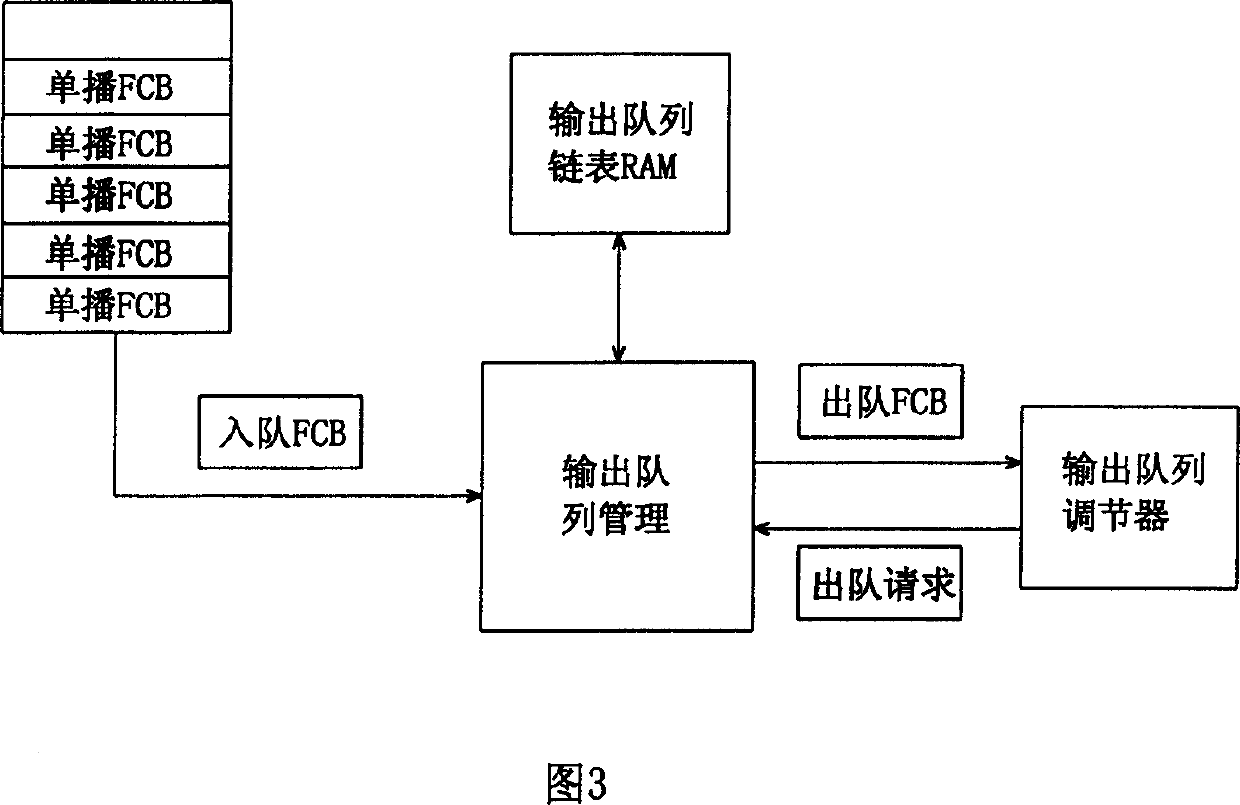

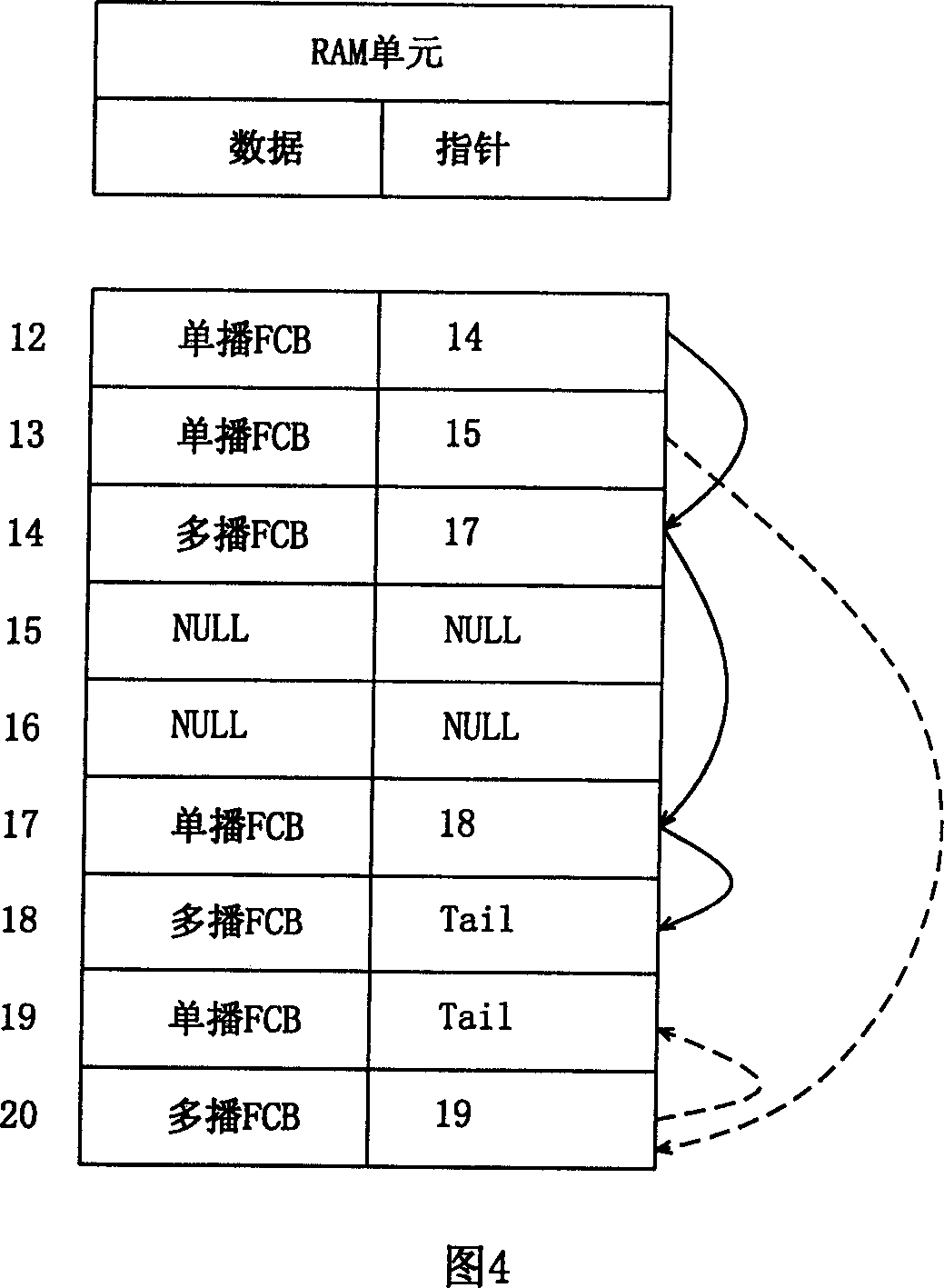

[0044] According to Fig. 6, Fig. 7, Fig. 8 and Fig. 9, with reference to Fig. 1, in the Ethernet switch chip, including input interface 1, shared cache 2, cache management module 4 and output interface 3, when data frames are written into the cache, the input Interface 1 extracts the information for forwarding the frame from the data frame, and sends it to the forwarding engine 5 together with the address of the data frame in the cache, and the forwarding engine 5 outputs the frame control block FCB to the output queue management module 6, and outputs Include a unicast / multicast message control separation module 61 in the queue management module 6 and frame control block FCB is output queue by the mode of unicast and multicast separation of every port, as shown in Figure 9, unicast data frame control block FCB passes through single Arbitration 62 for enter...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More