Patents

Literature

105results about How to "Easy to parallelize" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

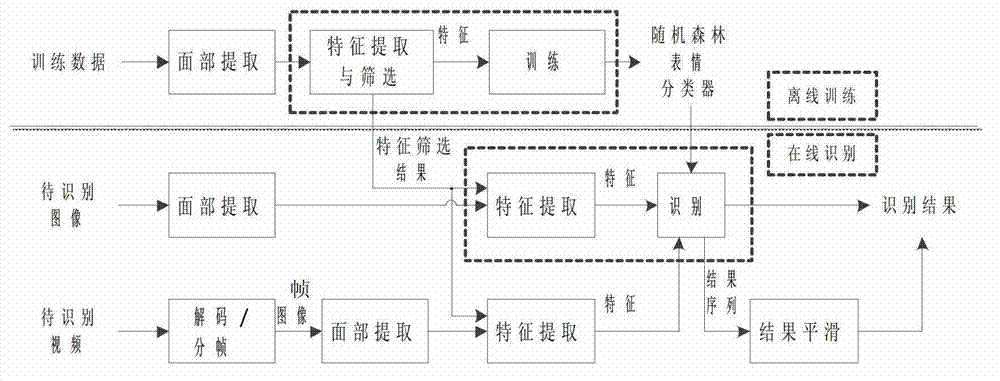

Method for identifying multi-class facial expressions at high precision

InactiveCN102831447AFast recognitionImprove accuracyCharacter and pattern recognitionGraphicsPersonal computer

The invention relates to a method for identifying multi-class facial expressions at a high precision based on Haar-like features, which belongs to the technical field of computer science and graphic image process. Firstly, the high-accuracy face detection is achieved by using the Haar-like features and a series-wound face detection classifier; further, the feature selection is carried out on the high-dimension Haar-like feature by using the Ada Boost. MH algorithm; and finally, the expression classifier training is carried out by using the Random Forest algorithm to complete the expression identification. Compared with the prior art, the method can reduce training and identifying time while increasing the multi-class expression identification rate, and can implement the parallelization conveniently to increase the identification rate and meet the requirement of real-time processing and mobile computing. The method can identify the static image and the dynamic image at a high precision, is not only applicable to the desktop computer but also to the mobile computing platforms, such as cellphone, tablet personal computer and the like.

Owner:BEIJING INSTITUTE OF TECHNOLOGYGY

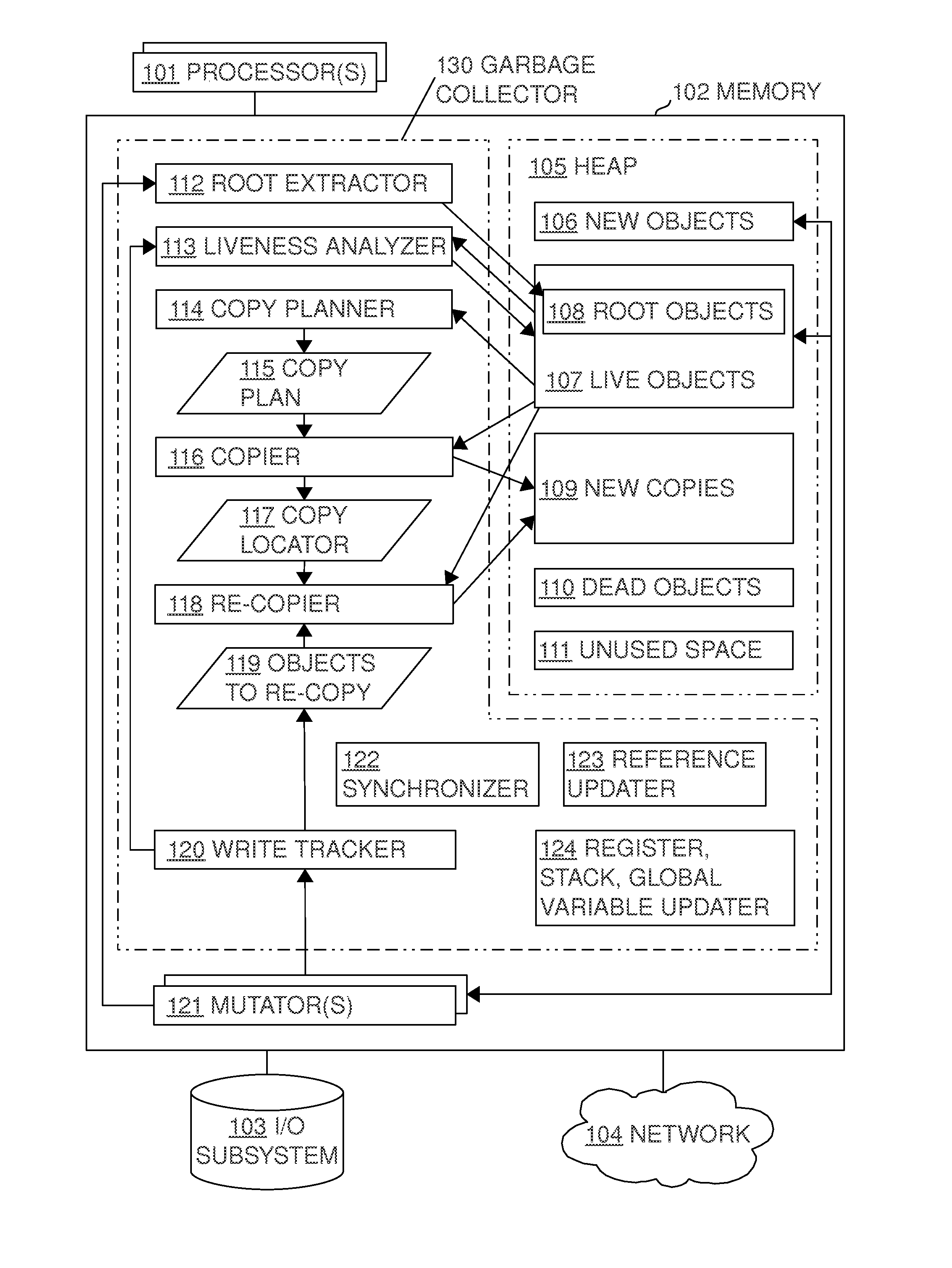

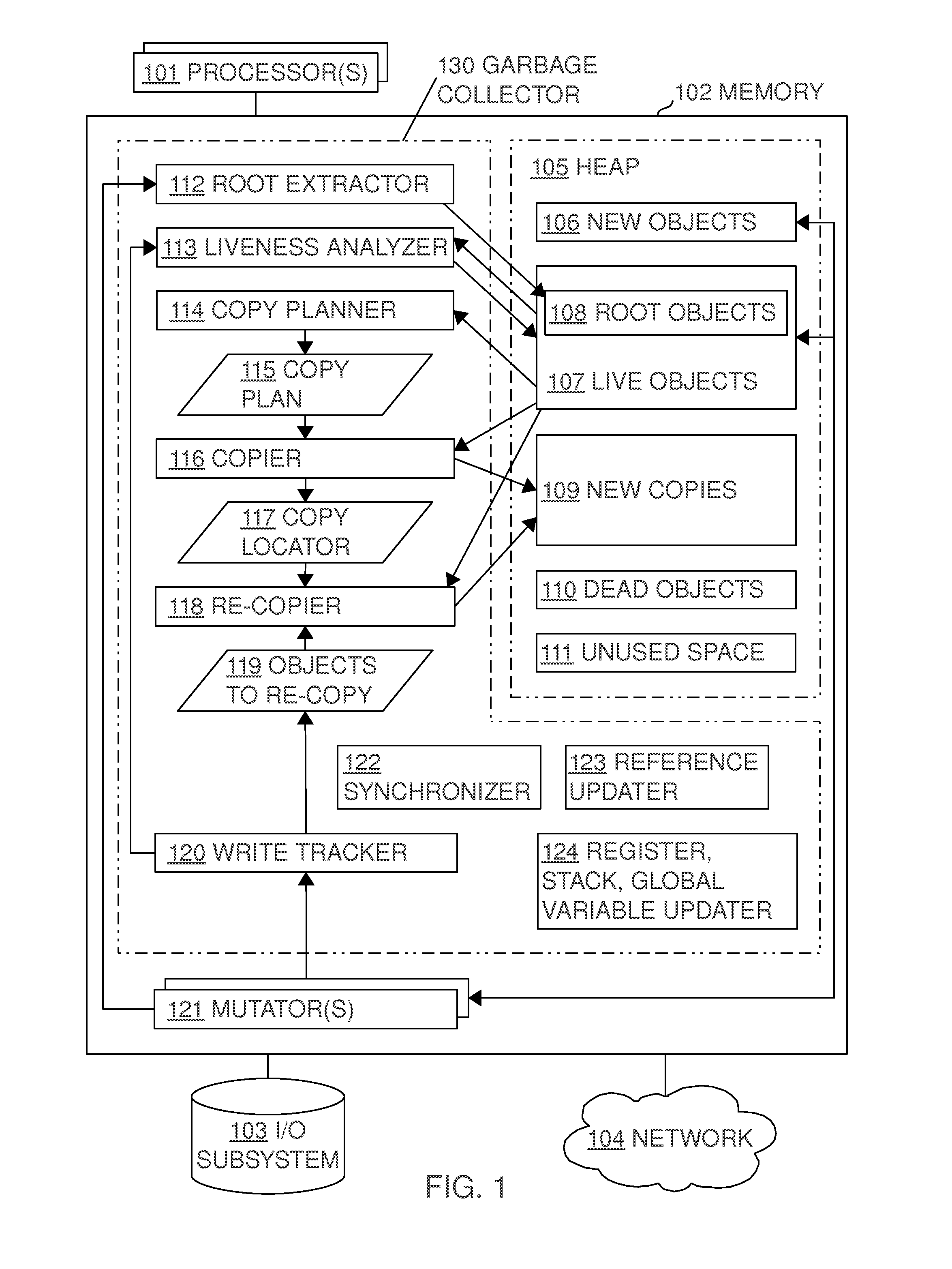

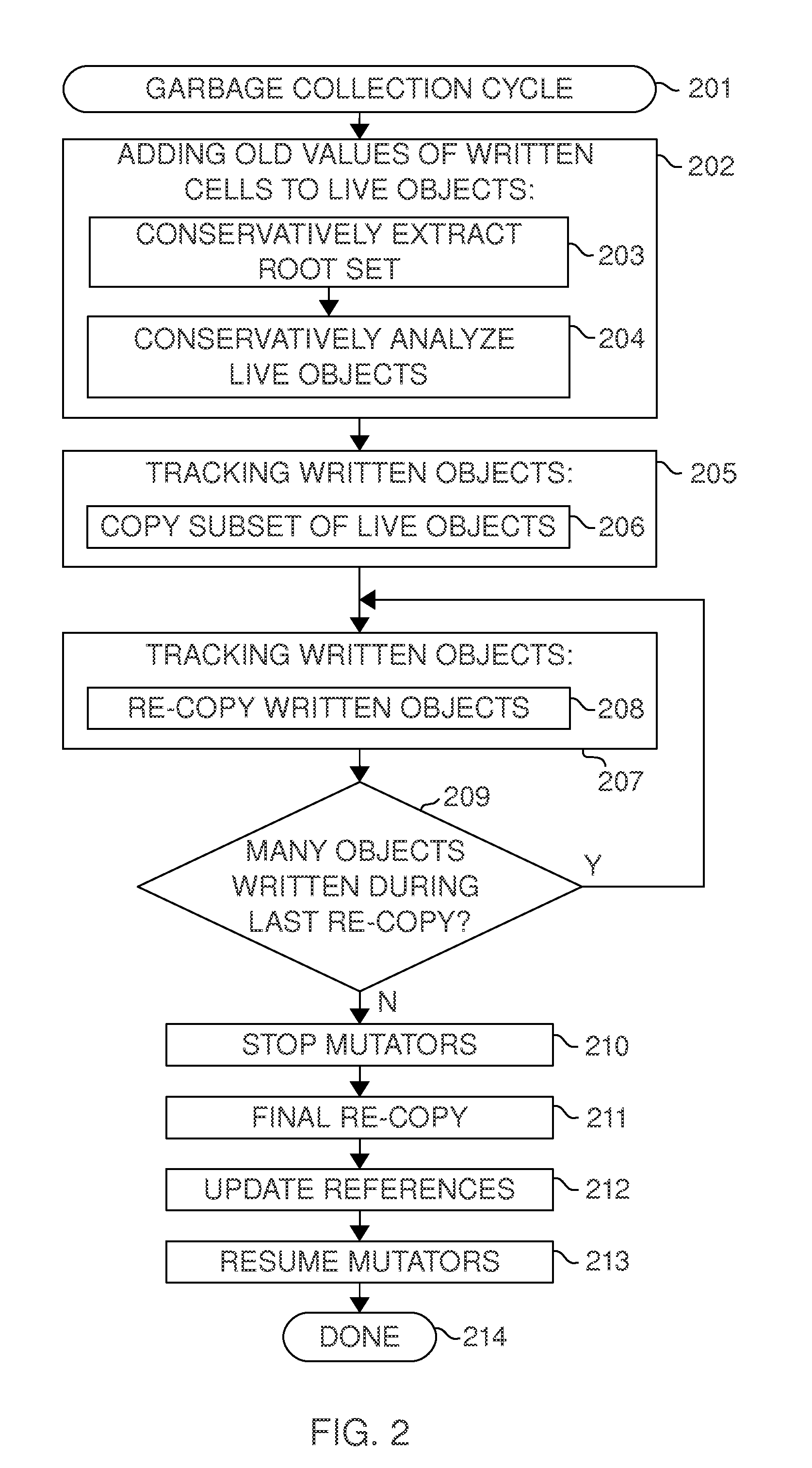

Copy planning in a concurrent garbage collector

InactiveUS20110264712A1Reduce amount of memoryEffective decouplingSpecial data processing applicationsMemory systemsRegion of interestOperating system

A garbage collector is disclosed that permits extensive separation of mutators and the garbage collector from a synchronization perspective. This relative decoupling of mutator and collector operation allows the garbage collector to perform relatively time-intensive operations during garbage collection without substantially slowing down mutators. The present invention makes use of this flexibility by first conservatively determining which objects in a set of regions of interest are live, then planning where to copy the objects (preferably including clustering), and finally performing the actual copying.

Owner:CLAUSAL COMPUTING

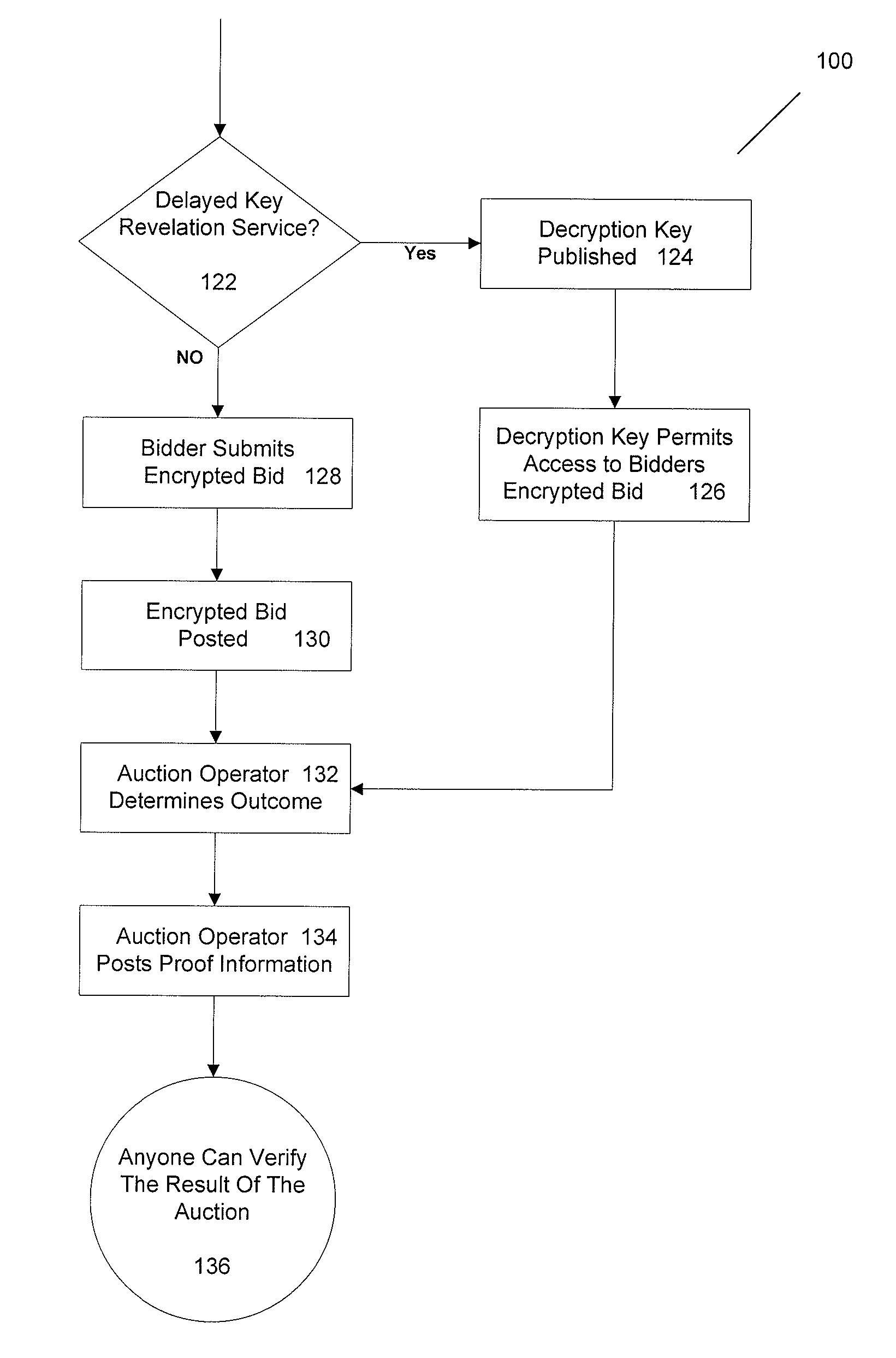

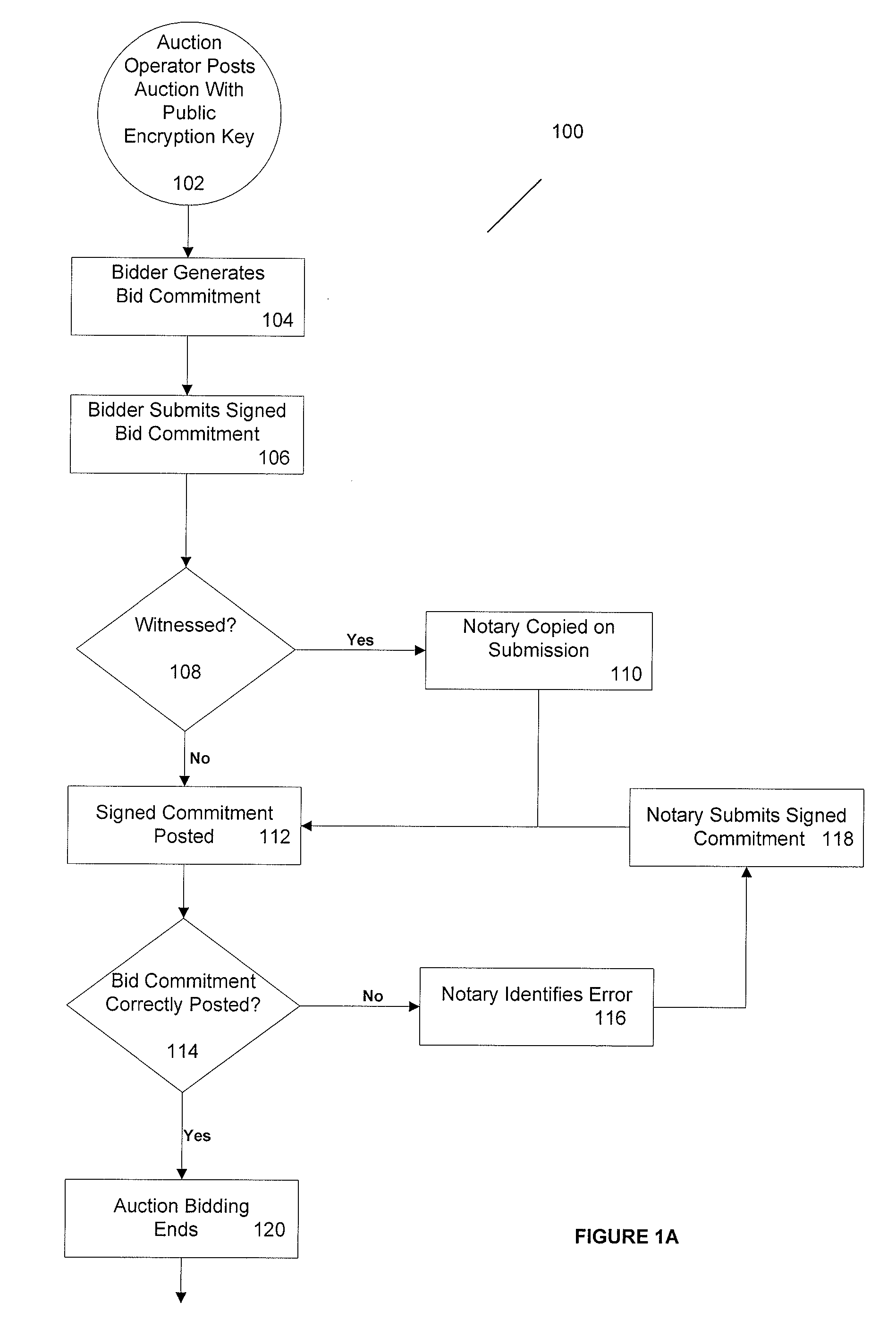

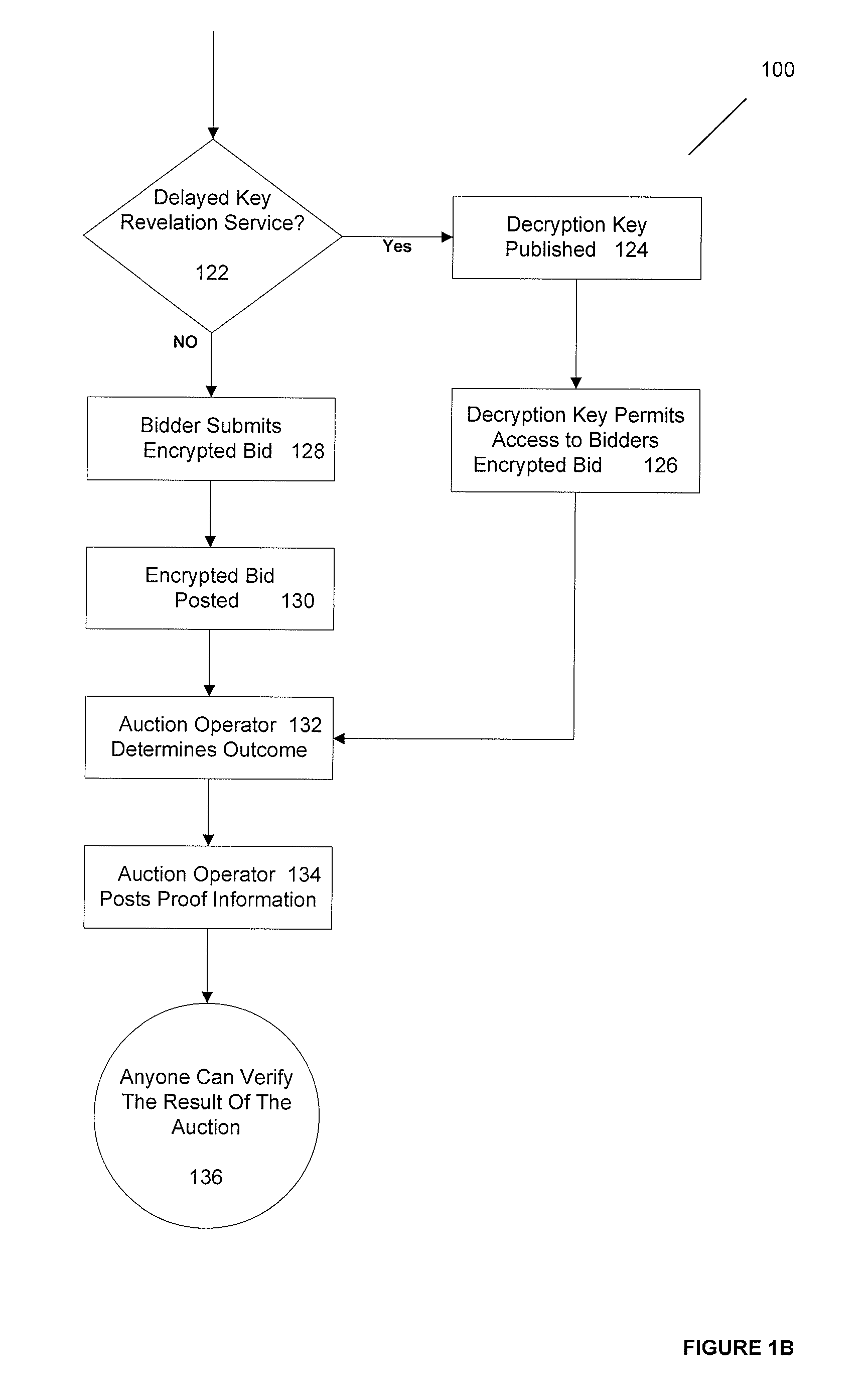

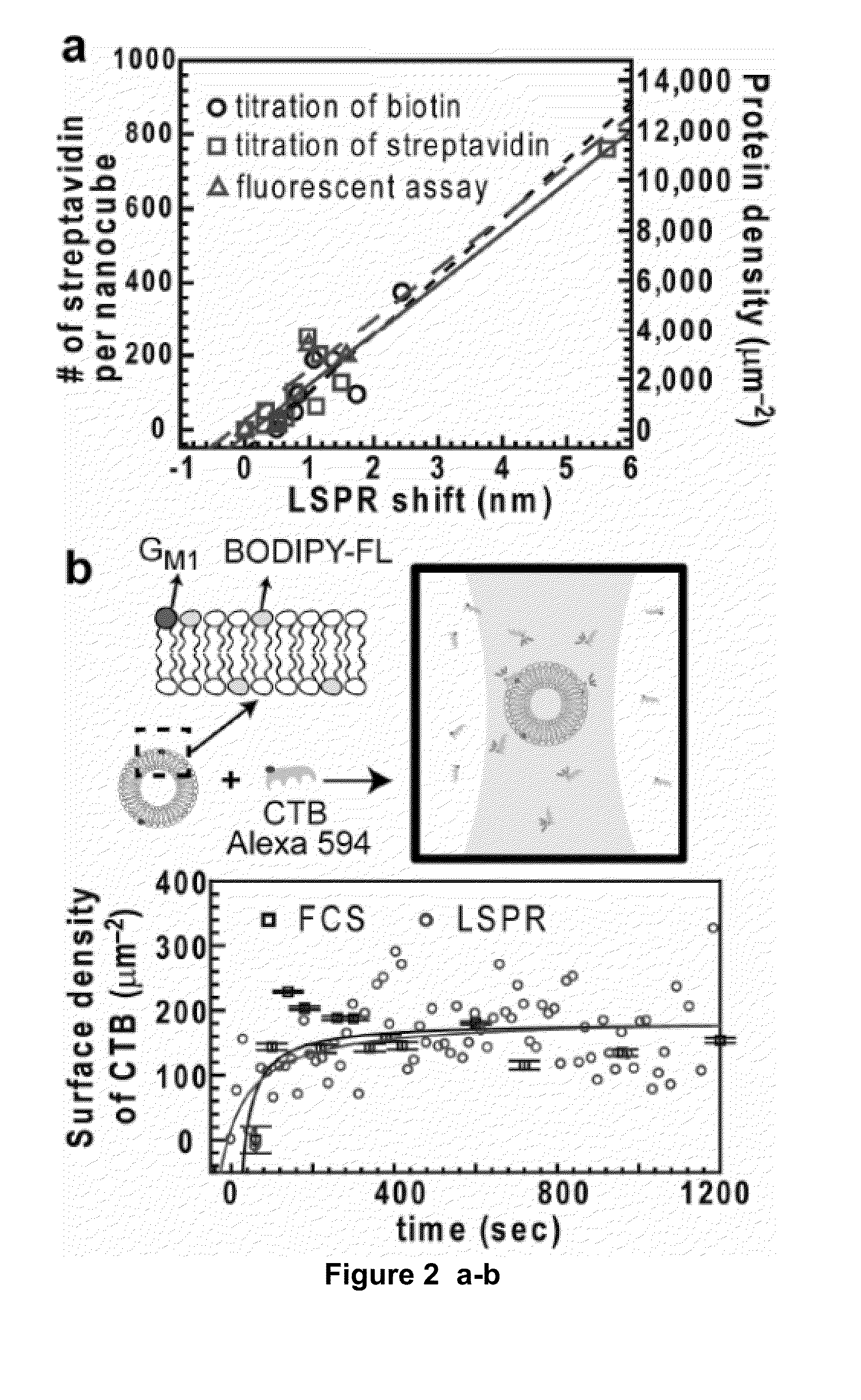

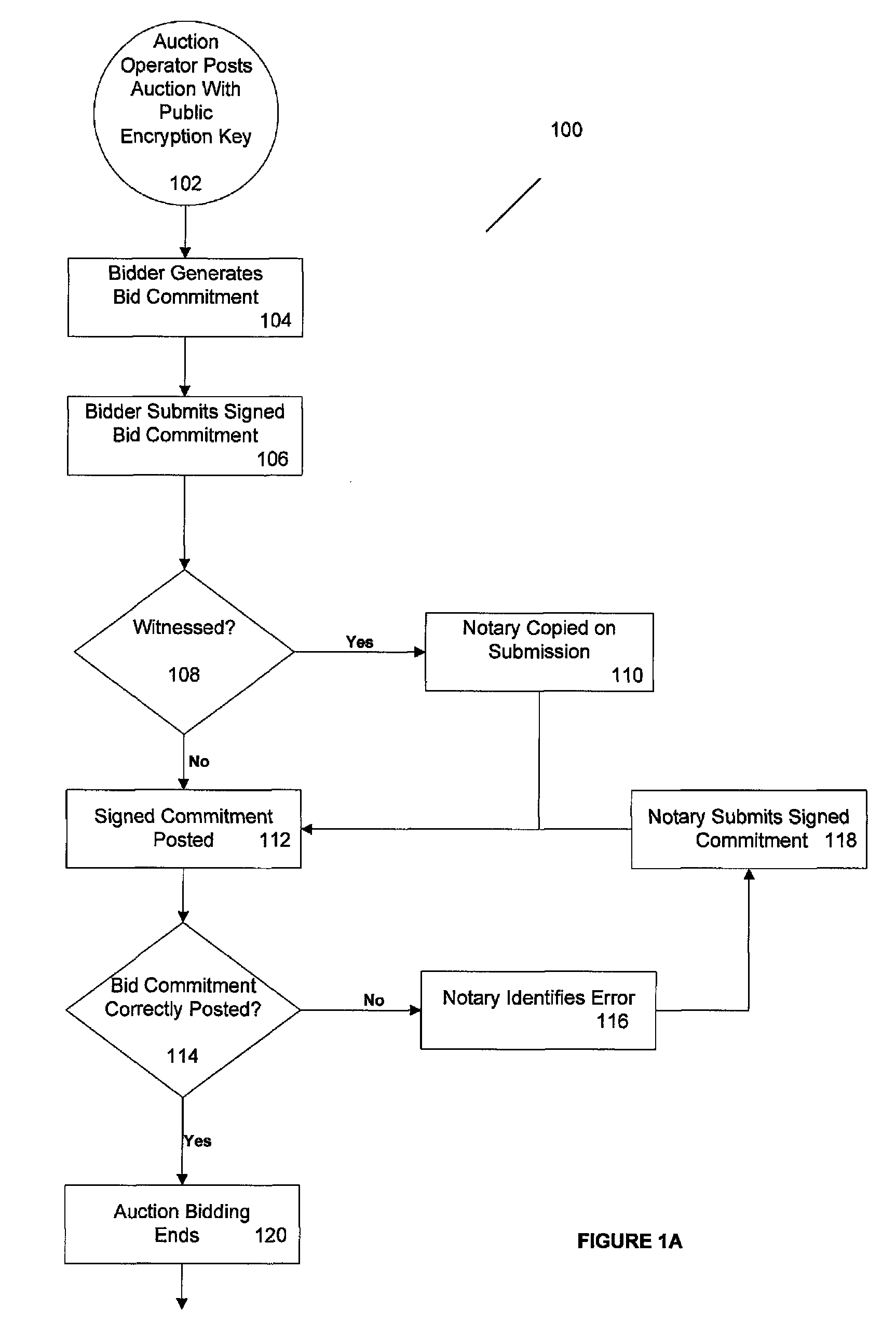

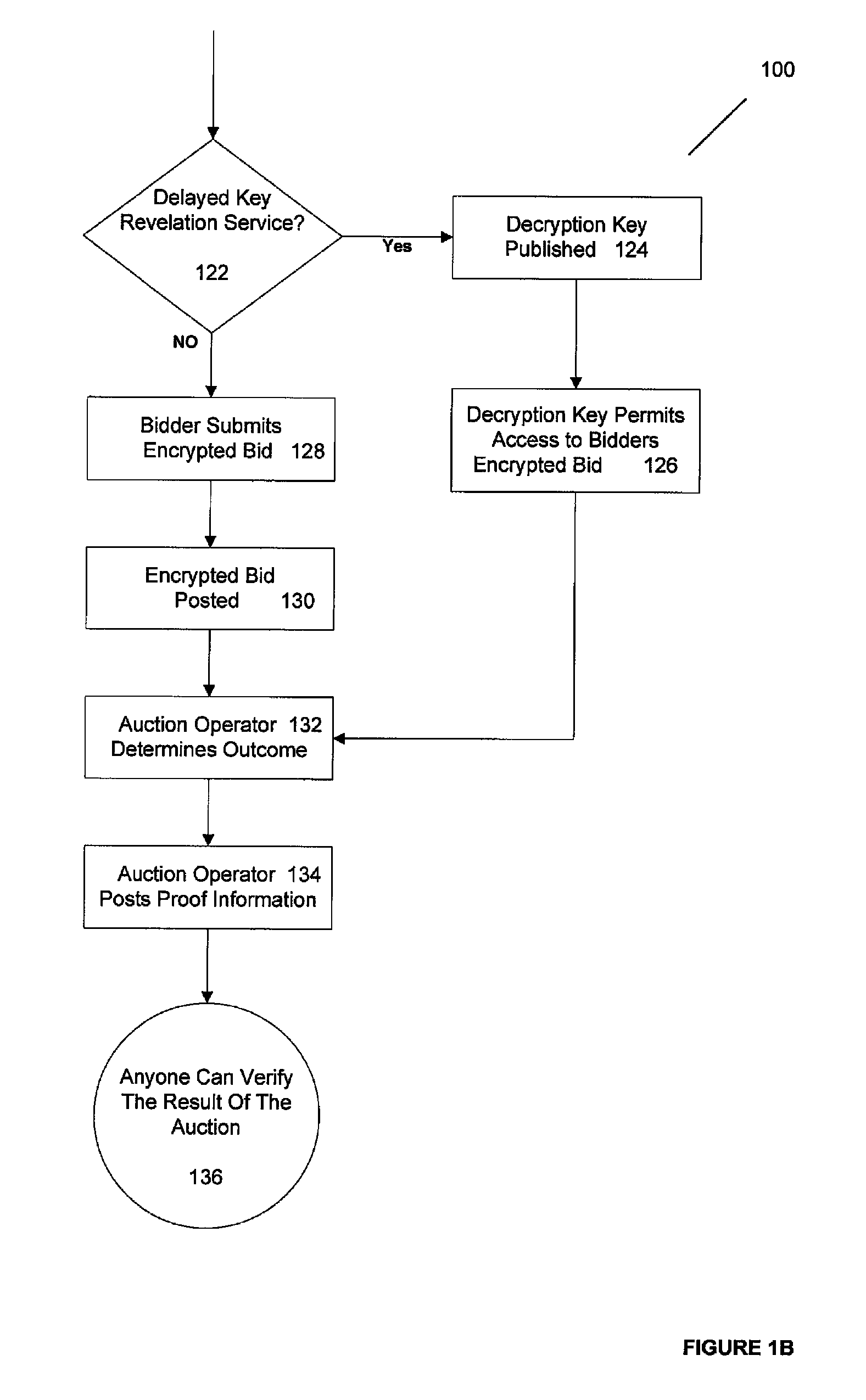

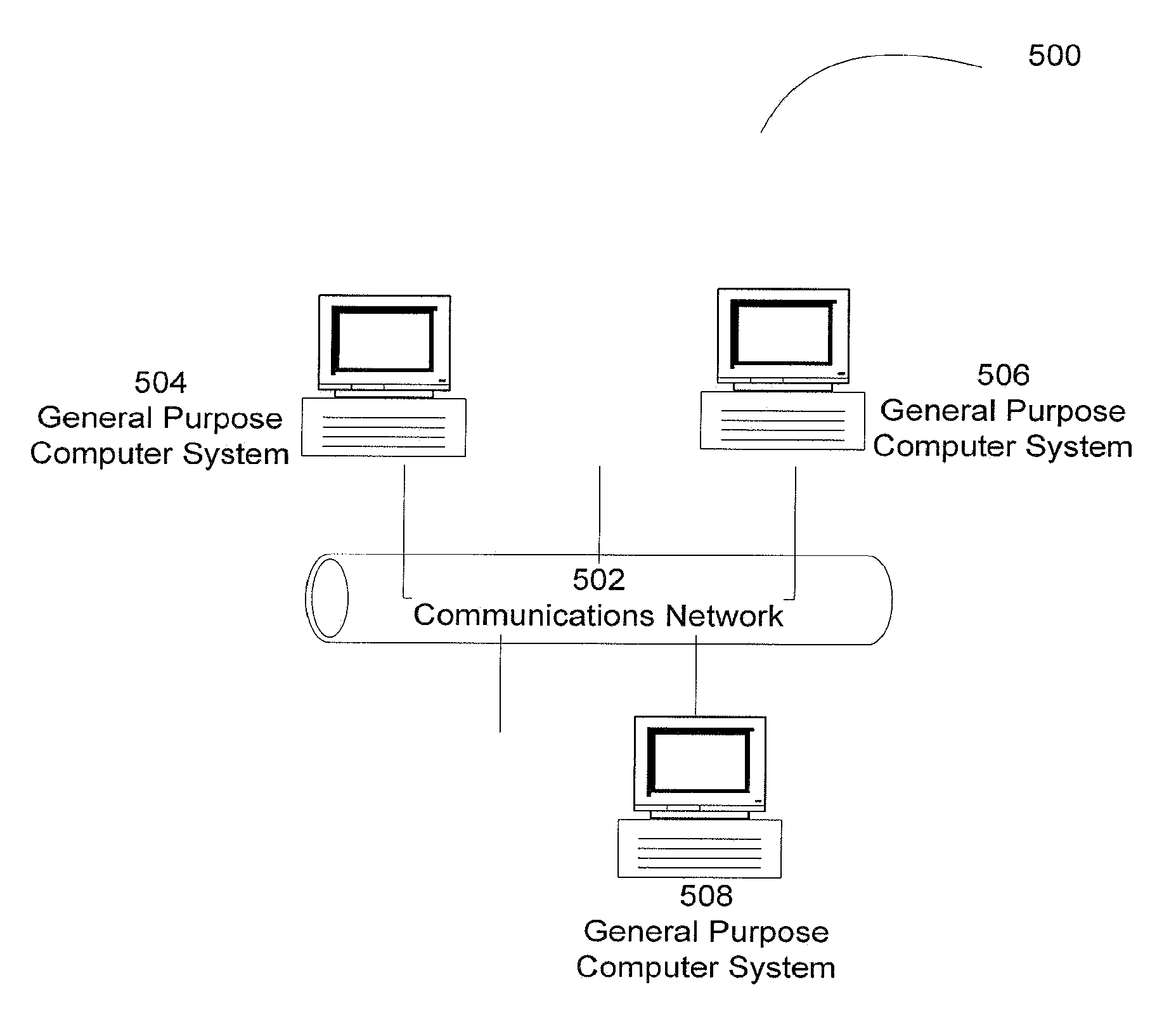

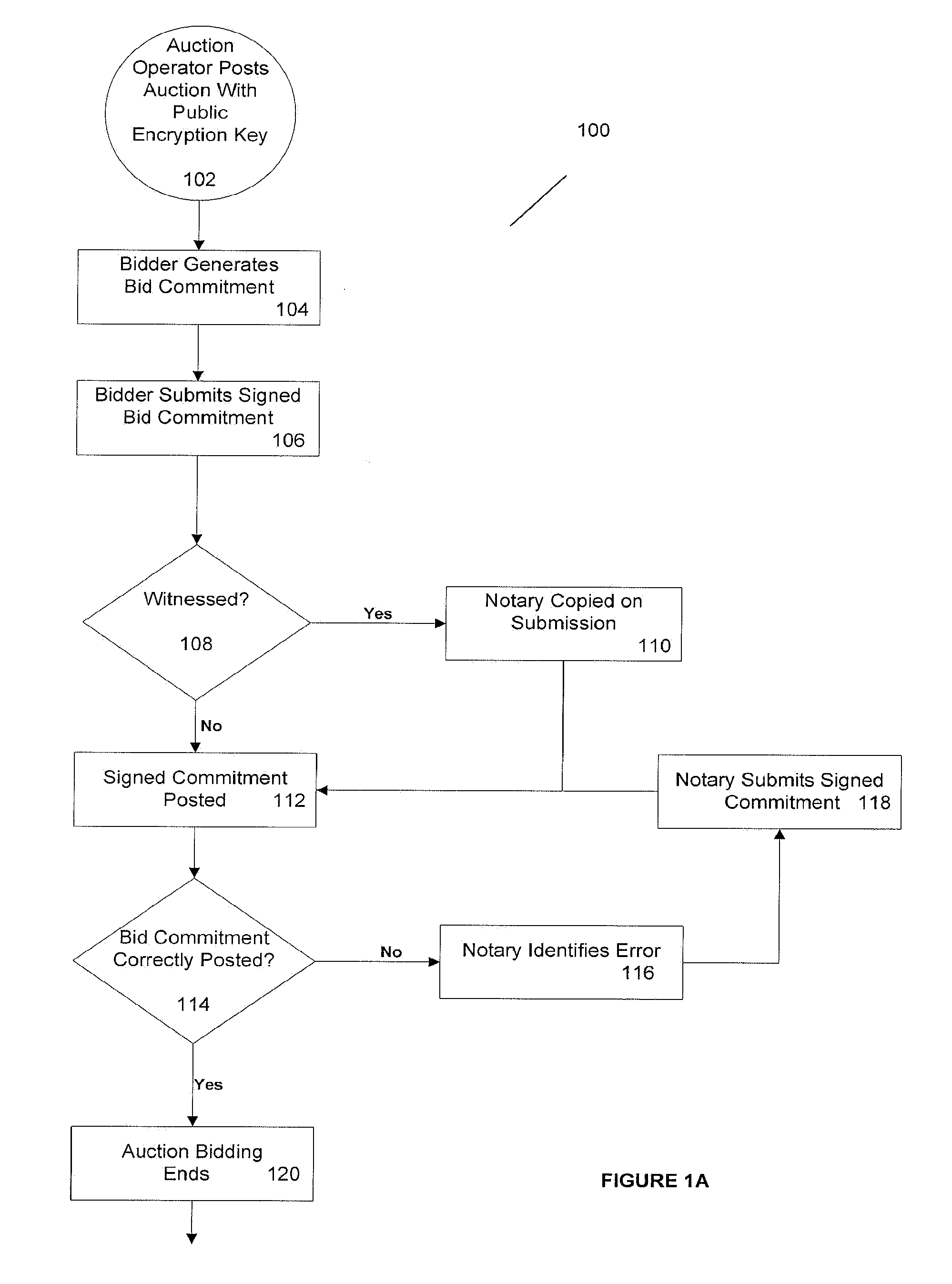

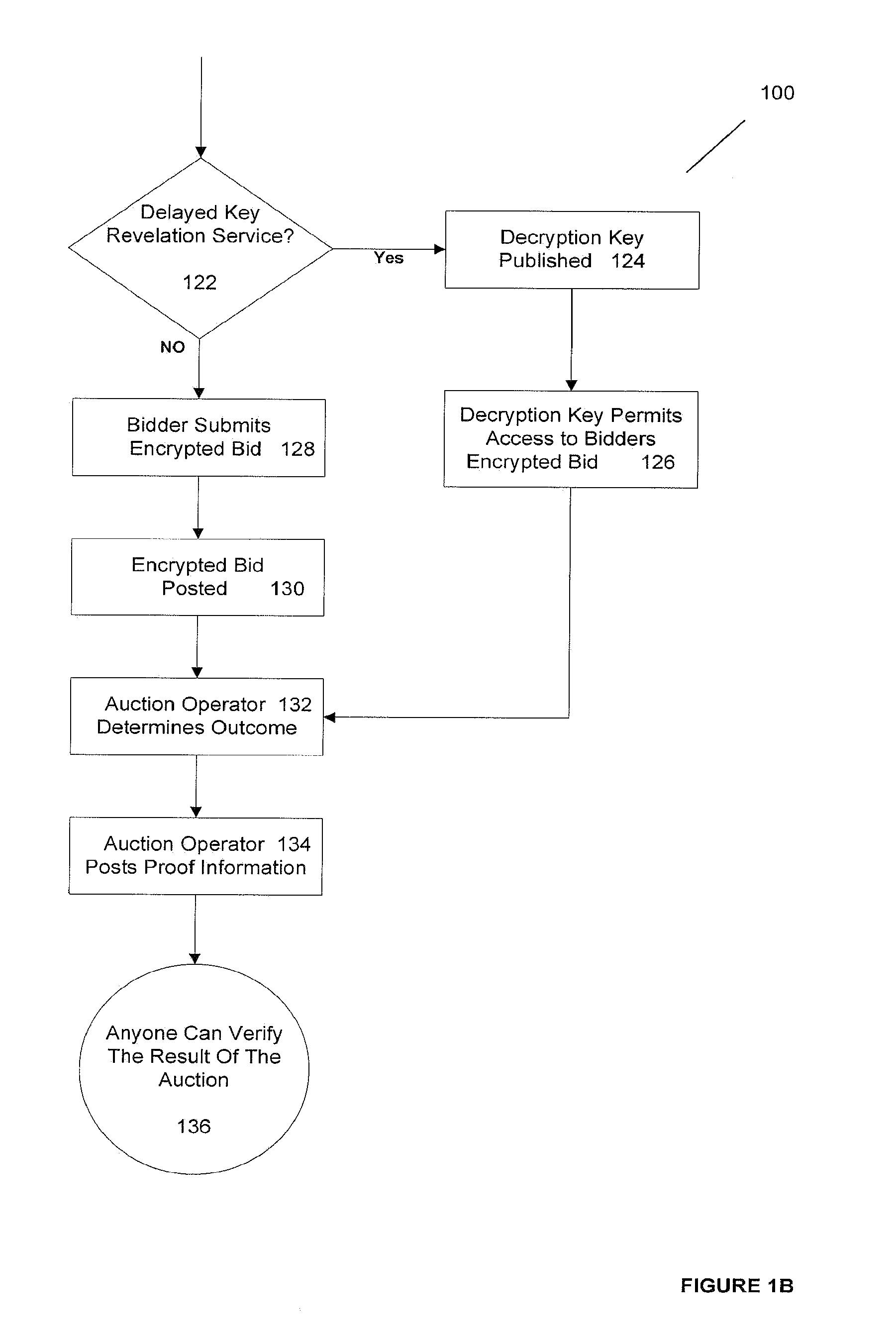

Practical secrecy-preserving, verifiably correct and trustworthy auctions

ActiveUS20090182667A1Ensure safetyImprove simplicityMultiple keys/algorithms usageUser identity/authority verificationCorrectness proofsTheoretical computer science

A system and method for conducting verifiably correct auctions that preserves the secrecy of the bids while providing for verifiable correctness and trustworthiness of the auction is disclosed. Some of the elements of the method and apparatus are that the auction operator accepts all bids submitted and follows the published rules of the auction. In one embodiment, the bids are maintained secret from the auctioneer and all bidders until the auction closes and no bidder is able to change or repudiate her bid. In another embodiment, the auction operator computes the auction results and publishes proofs of the results' correctness. In yet another embodiment, any party can check these proofs of correctness via publicly verifiable computations on encrypted bids.

Owner:PRESIDENT & FELLOWS OF HARVARD COLLEGE

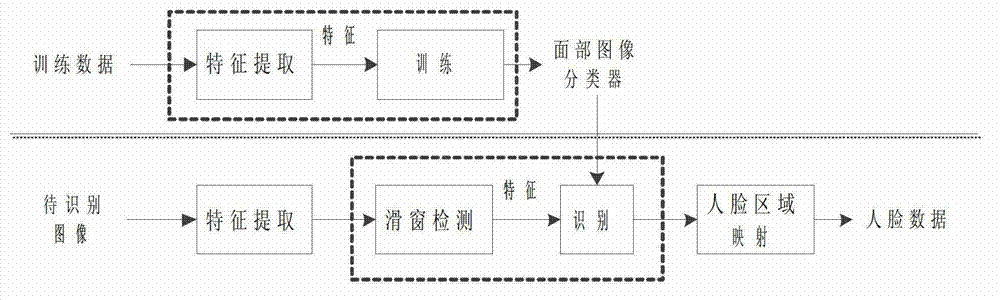

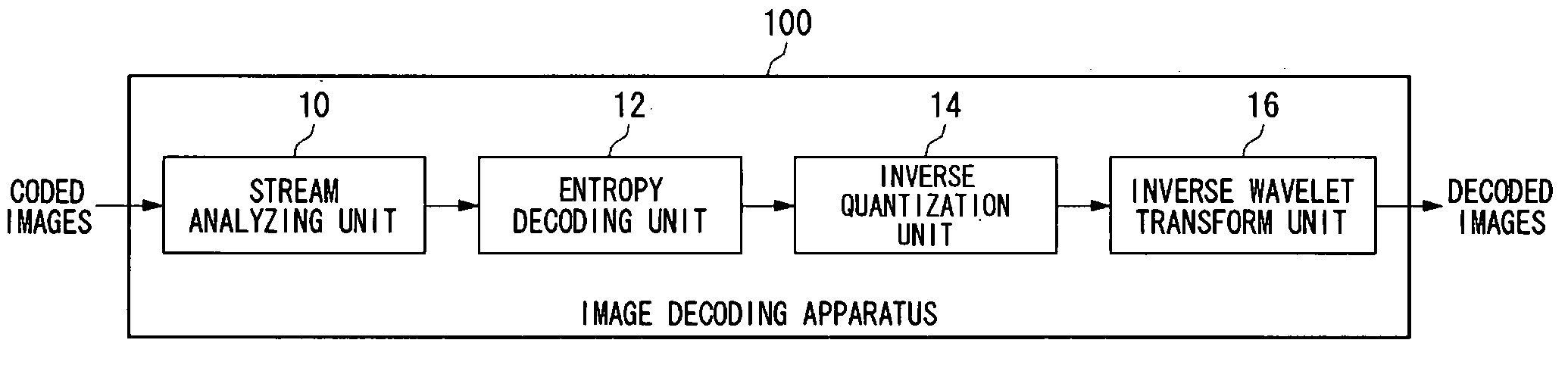

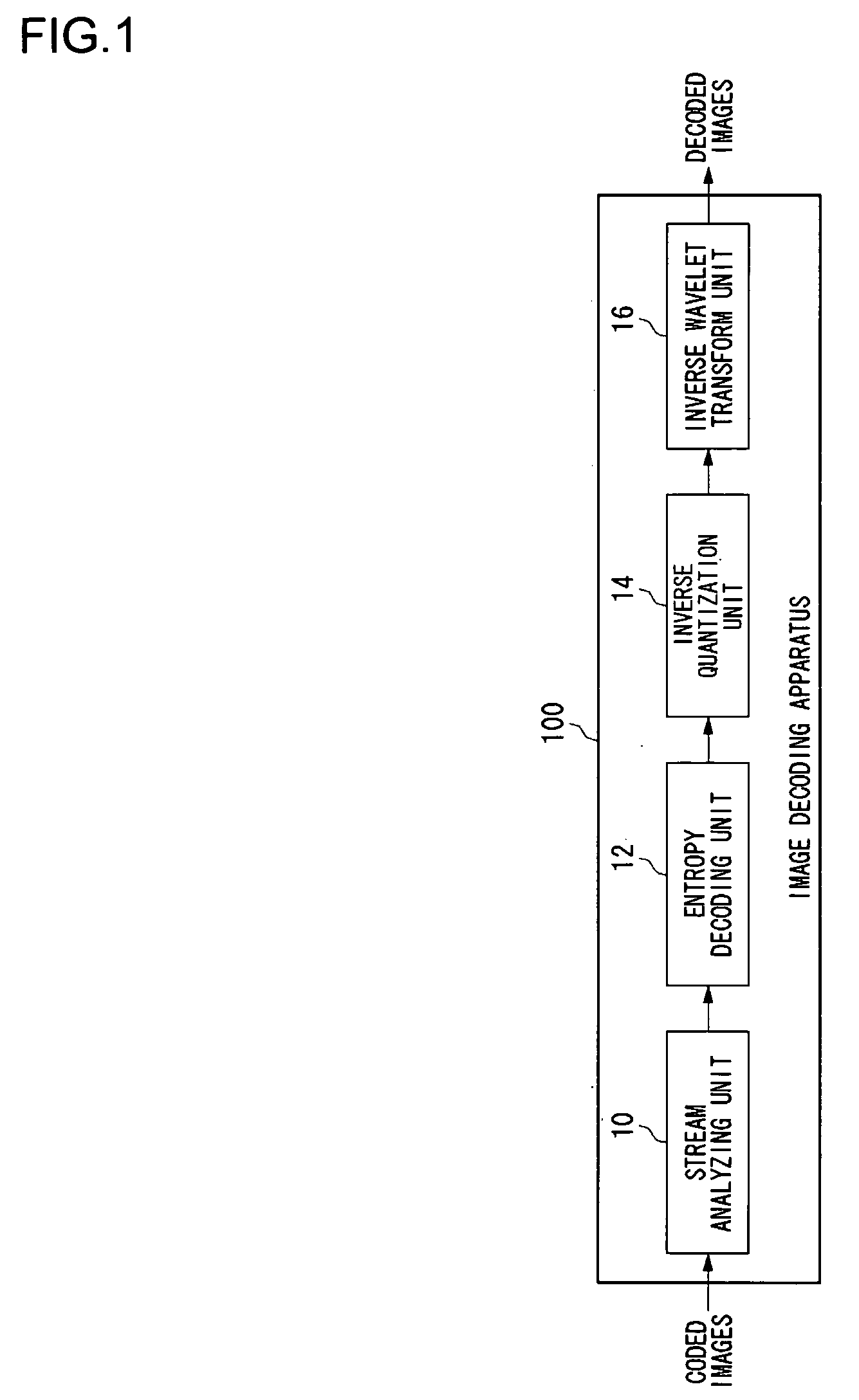

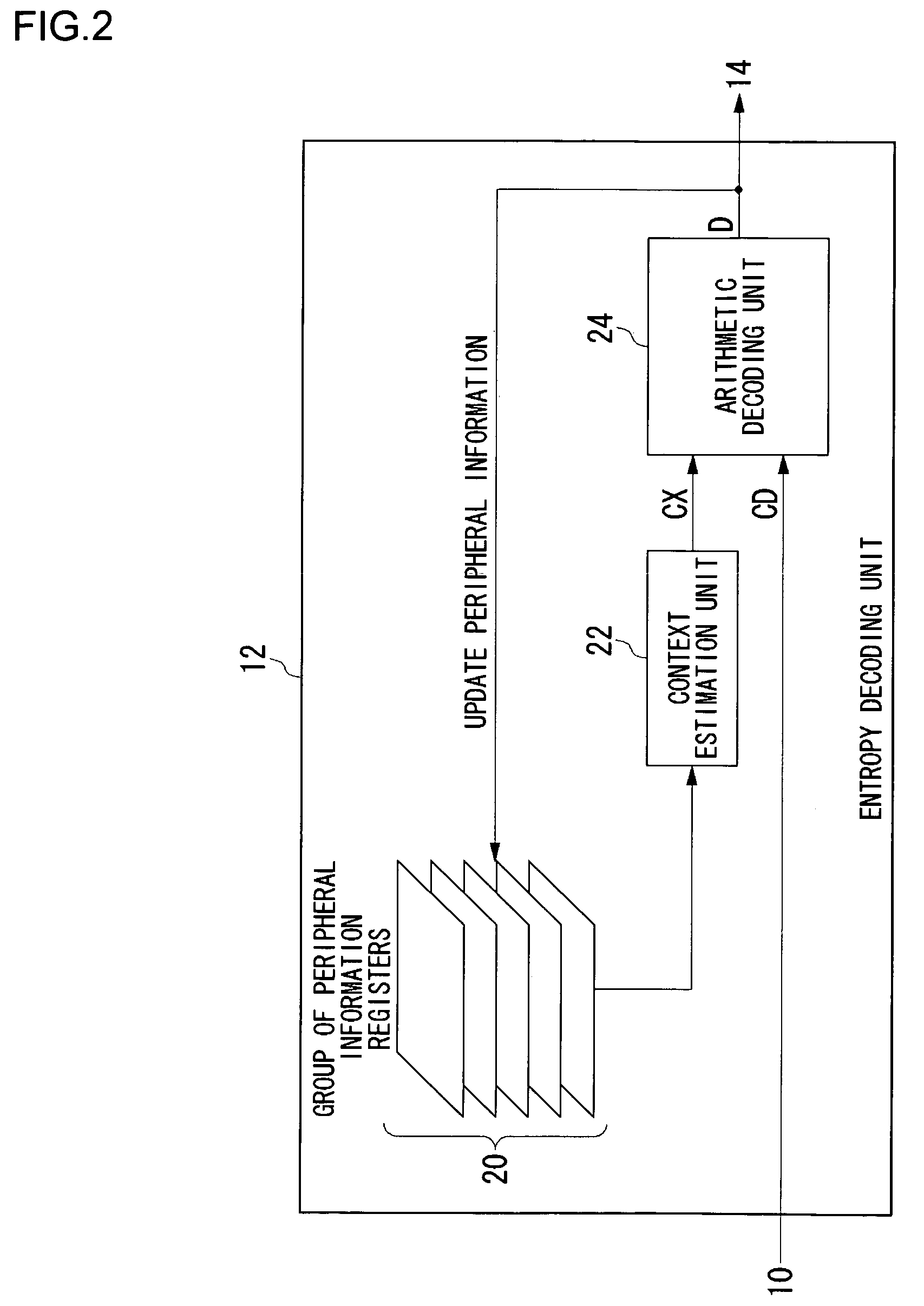

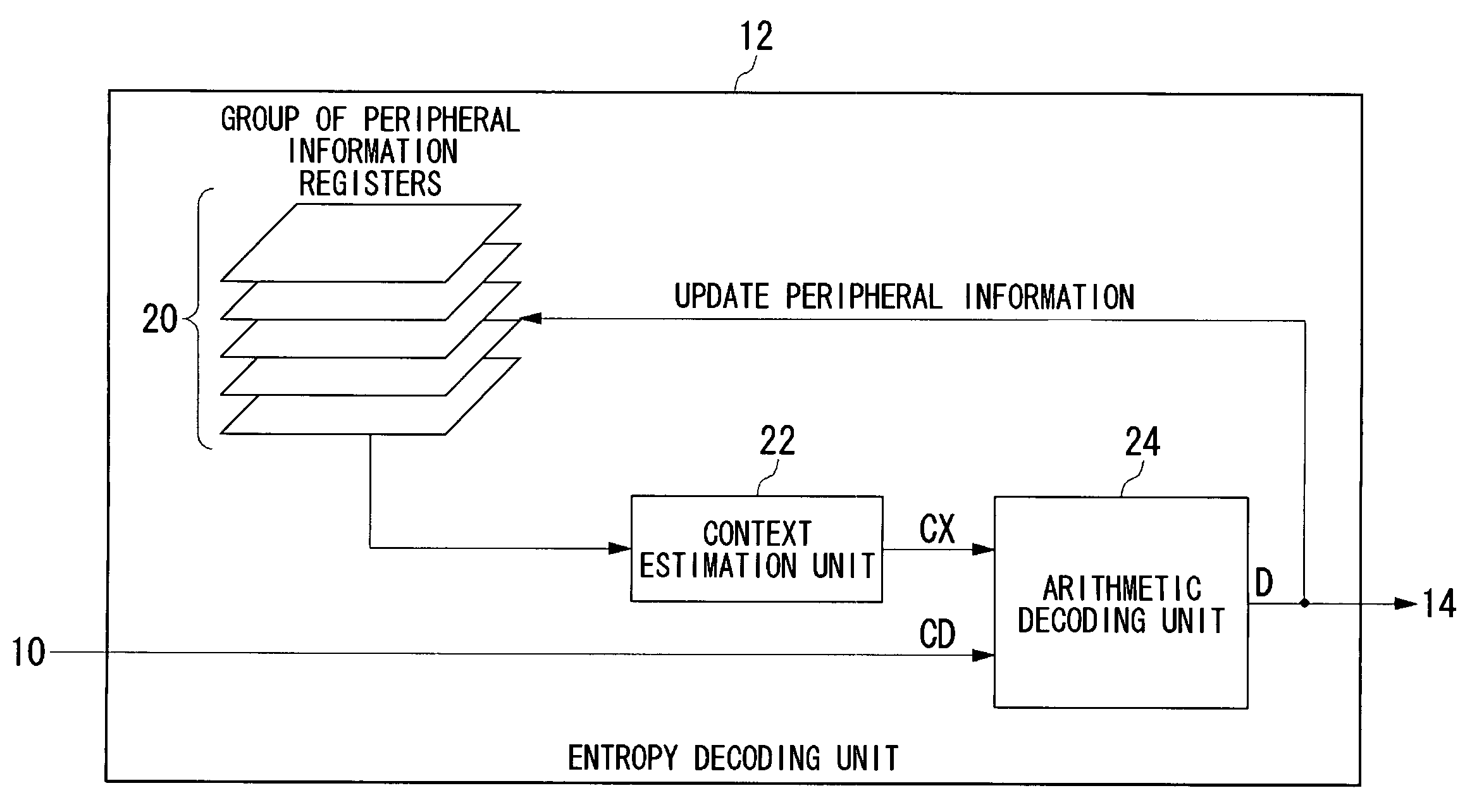

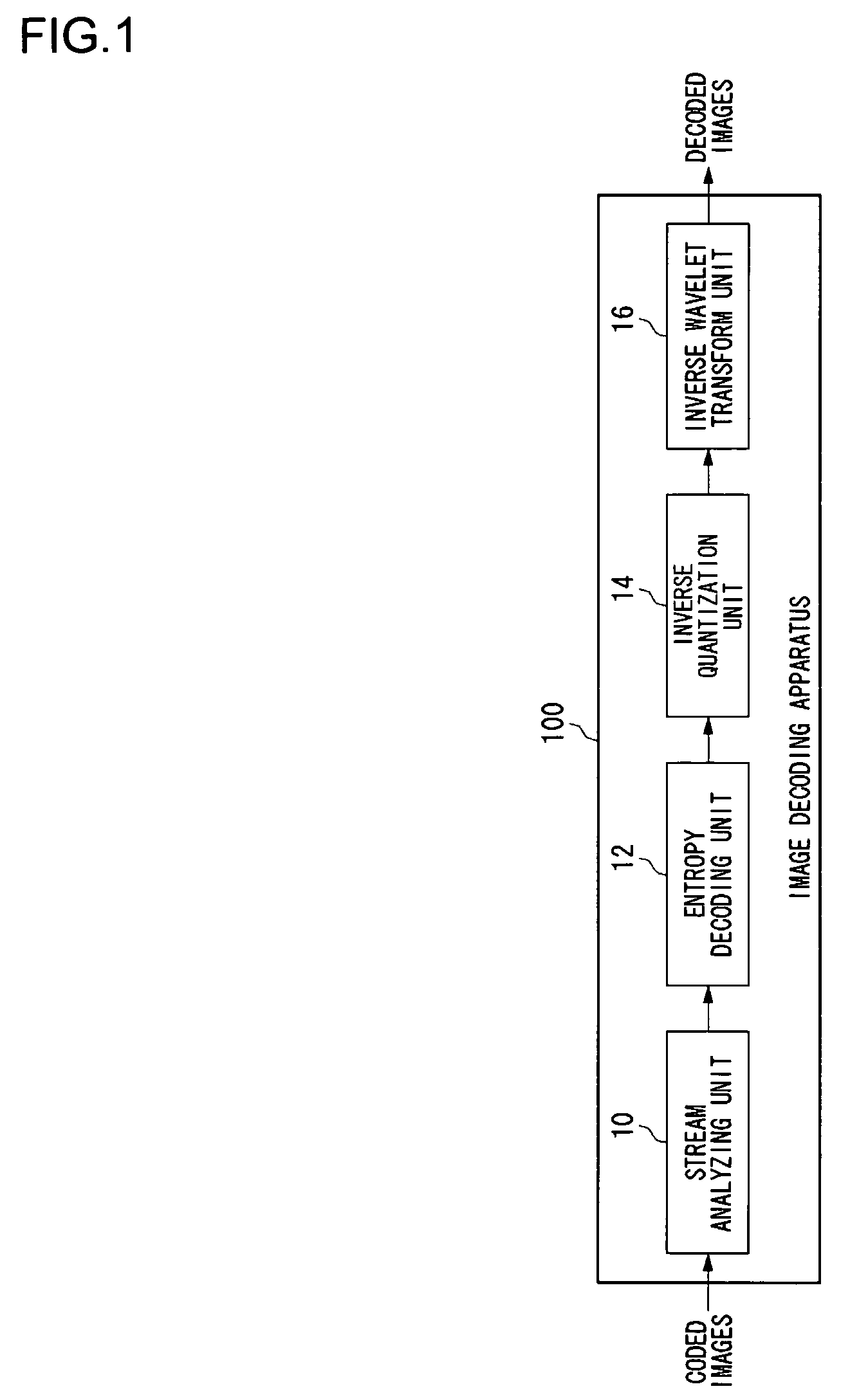

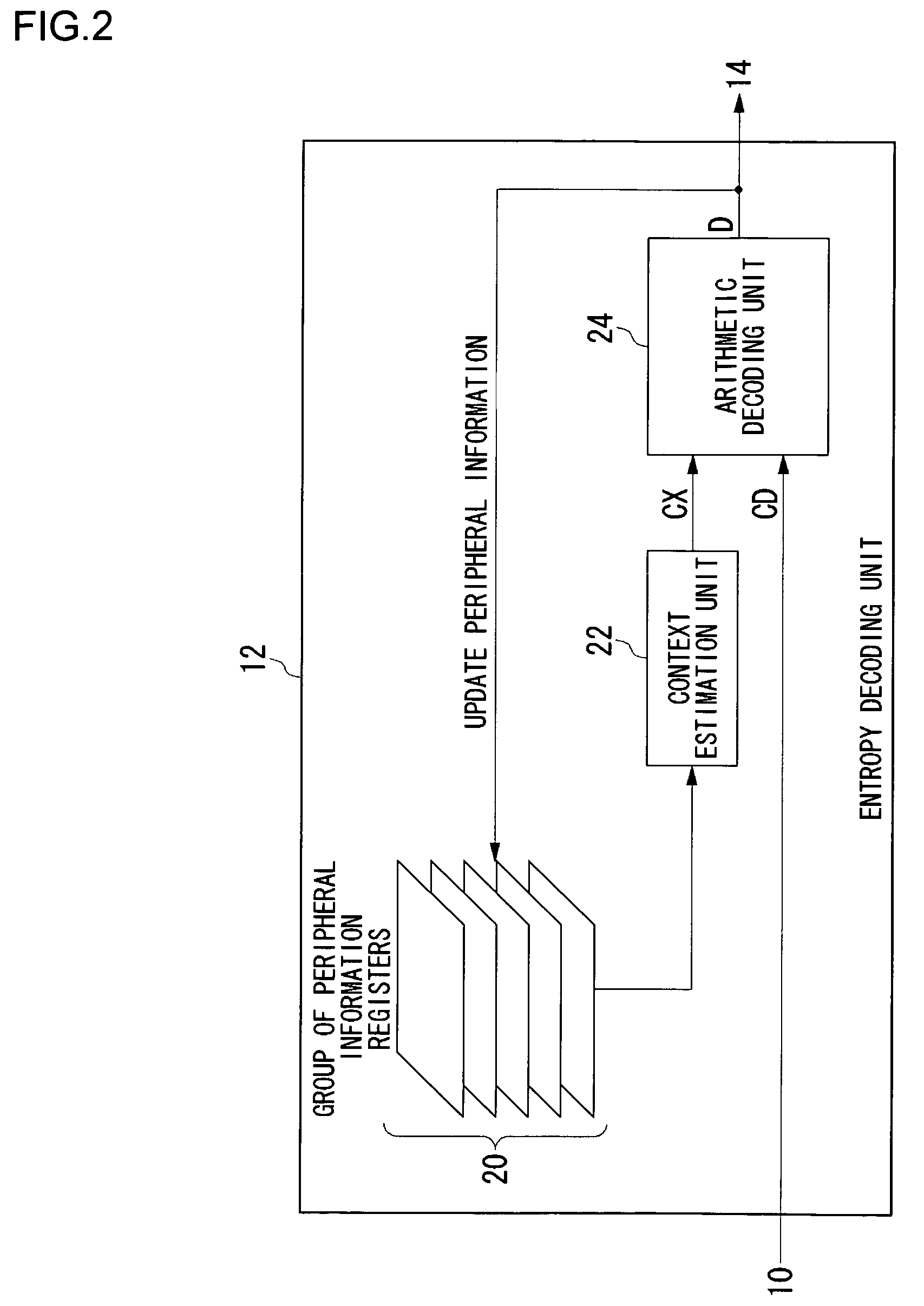

Image decoding apparatus

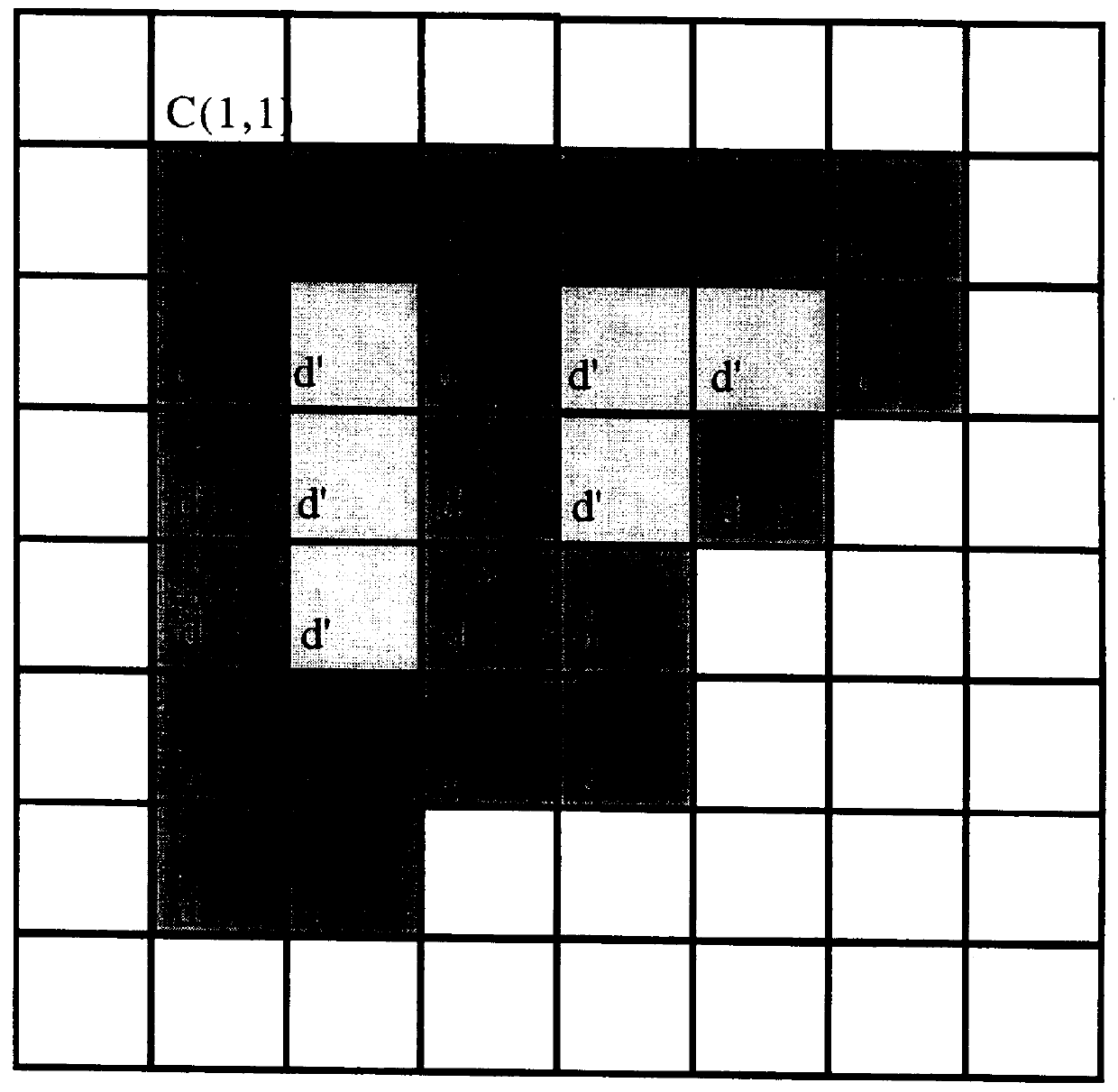

InactiveUS20050175250A1Easy to parallelizeImprove versatilityCode conversionCharacter and pattern recognitionComputer scienceInverse quantization

Coded data are inputted from a stream analyzing unit to an entropy decoding unit. A group of peripheral information registers stores peripheral information on a target pixel for estimating a context used for arithmetic decoding of the coded data. Based on the peripheral information stored in the group of peripheral registers, a context estimation unit estimates a context and delivers the estimated context to an arithmetic decoding unit. The arithmetic decoding unit decodes the coded data based on a context label, then derives a decision and supplies the decision to an inverse quantization unit. The peripheral information stored in the group of peripheral registers is updated by a decoding result of the arithmetic decoding unit in the same cycle as the decoding.

Owner:SANYO ELECTRIC CO LTD

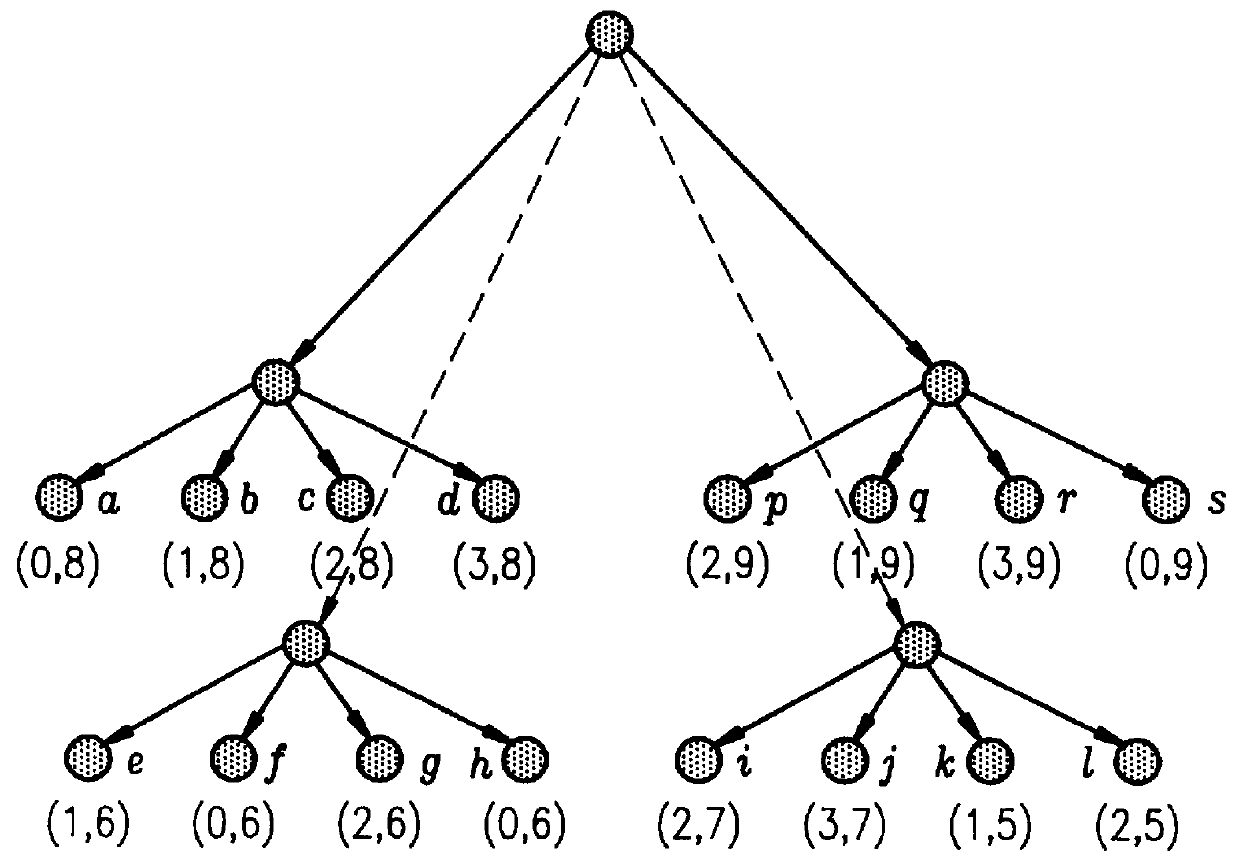

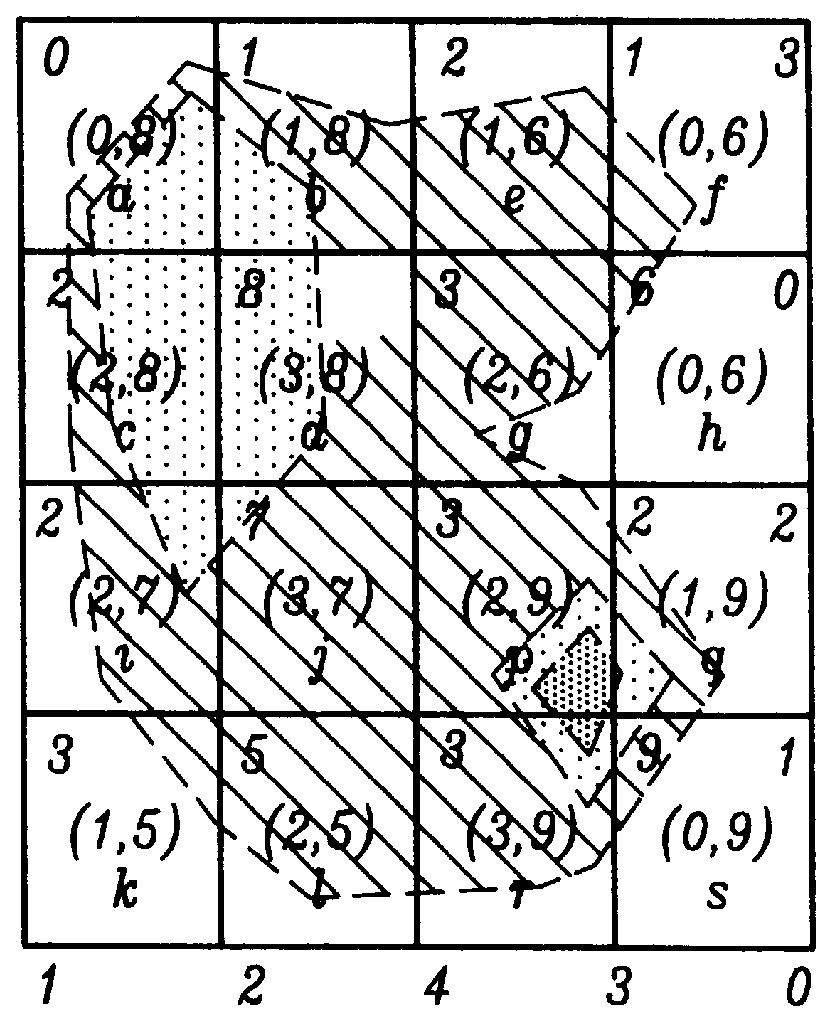

Time and space efficient data structure and method and apparatus for using the same for surface rendering

InactiveUS6075538AIncrease speedMeet growth requirementsCharacter and pattern recognition3D-image renderingSearch algorithmData set

A computationally time and space efficient data structure and method and system for using the same for surface rendering. The basis for the new data structure lies in organizing a volume data set for surface rendering into a new format where the cells needed for the surface rendering can be searched and displayed more efficiently. Given a threshold t specified by the user, the present data structure is able to efficiently identify all surface cells saving valuable processing time by providing three unique beneficial characteristics. First, given a threshold t, it can directly provide all S-cells without having to check most of the 1-cells and 0-cells such that no time is wasted on visiting the intermediate nodes. Second, it facilitates significant savings in memory space where the data structure only requires N3 pointers for data storage saving memory space for all intermediate nodes, i.e. O(N3) pairs of (Min, Max). And third, it makes viable a searching algorithm which can have parallelization capabilities for finding all S-cells such that the algorithm can be efficiently used in today's workstation employing more than one processor.

Owner:INST OF HIGH PERFORMANCE COMPUTING

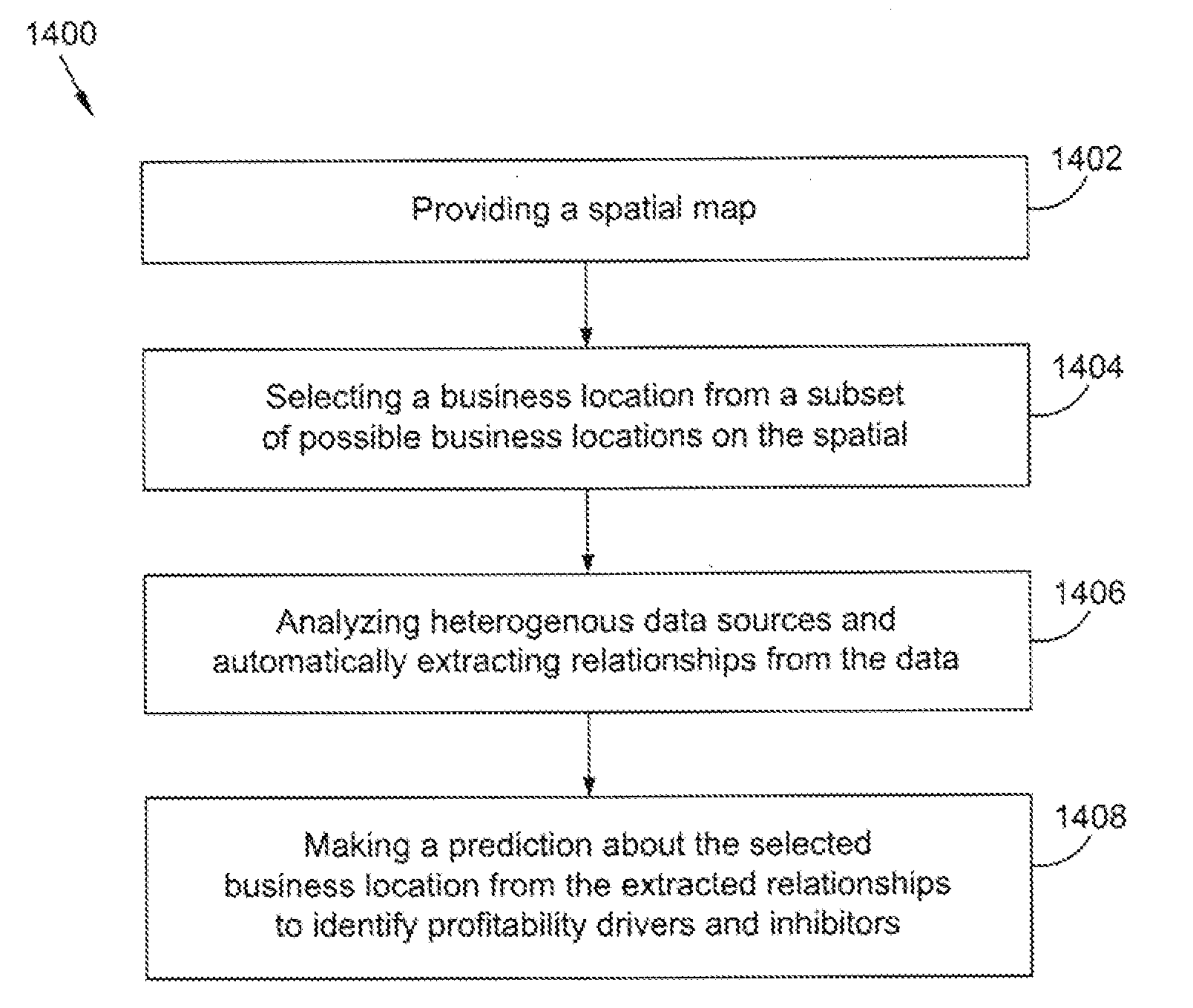

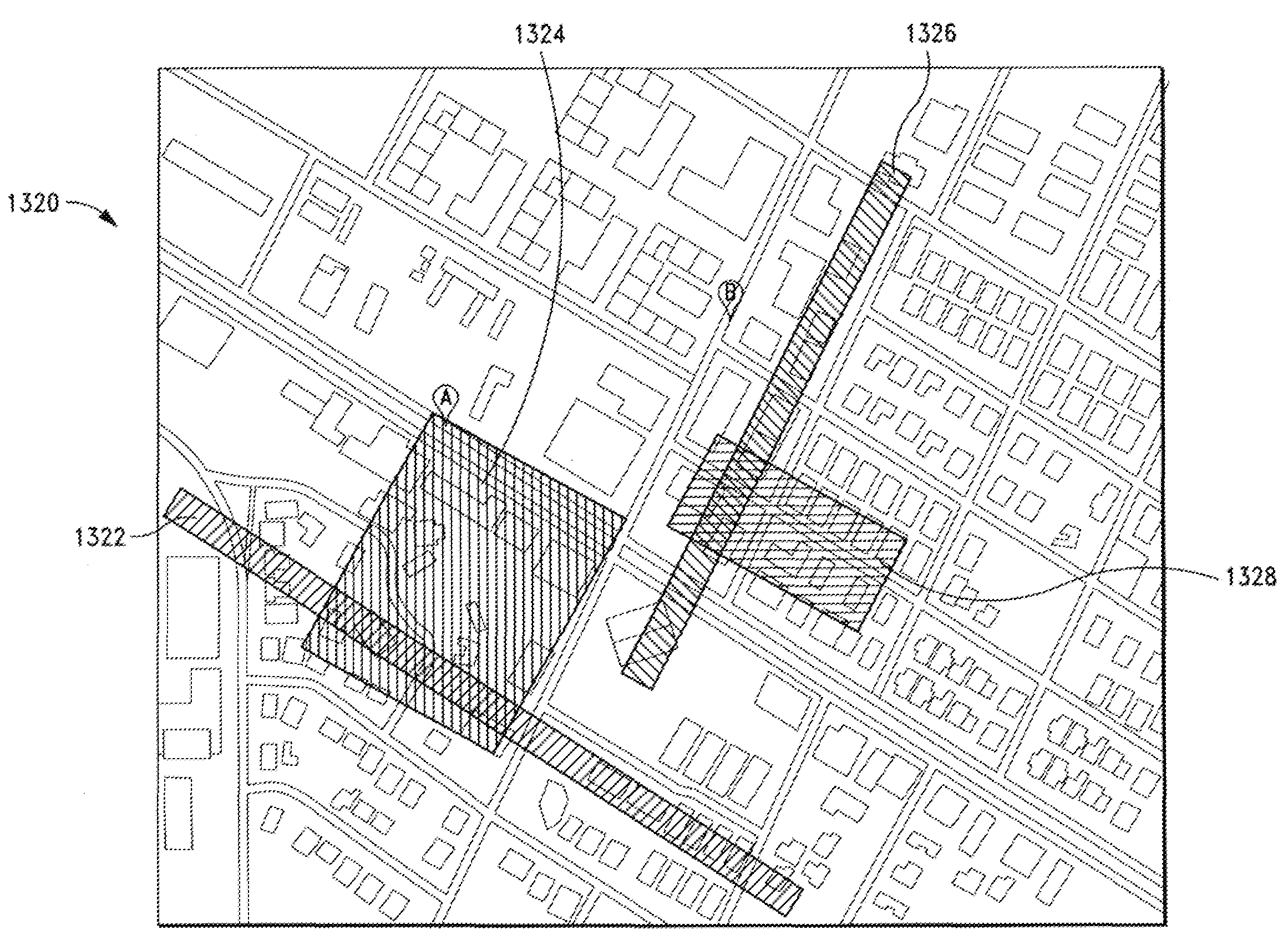

Method and system utilizing online analytical processing (OLAP) for making predictions about business locations

ActiveUS20080208652A1Reducing resourceShorten the timeForecastingCommerceSpatial mapsComposite indicator

A method and system that utilizes OLAP and supporting data structures for making predictions about business locations. The method includes providing a spatial map and analyzing heterogeneous data having a spatial component to find utilizable data. Relationships are automatically extracted from the utilizable data by employing machine learning. The step of automatically extracting relationships includes generating a composite indicator, which correlates spatial data with unstructured data. The extracted relationships are presented on a spatial map to make a prediction about at least one business location. Preferably, the predictions are presented as a rank-ordered list on the spatial map and a heat map overlays the spatial map to indicate predictions about particular regions.

Owner:SAAMA TECH

Method and system utilizing online analytical processing (OLAP) for making predictions about business locations

A method and system that utilizes OLAP and supporting data structures for making predictions about business locations. The method includes providing a spatial map and analyzing heterogeneous data having a spatial component to find utilizable data. Relationships are automatically extracted from the utilizable data by employing machine learning. The step of automatically extracting relationships includes generating a composite indicator, which correlates spatial data with unstructured data. The extracted relationships are presented on a spatial map to make a prediction about at least one business location. Preferably, the predictions are presented as a rank-ordered list on the spatial map and a heat map overlays the spatial map to indicate predictions about particular regions.

Owner:SAAMA TECH LLC

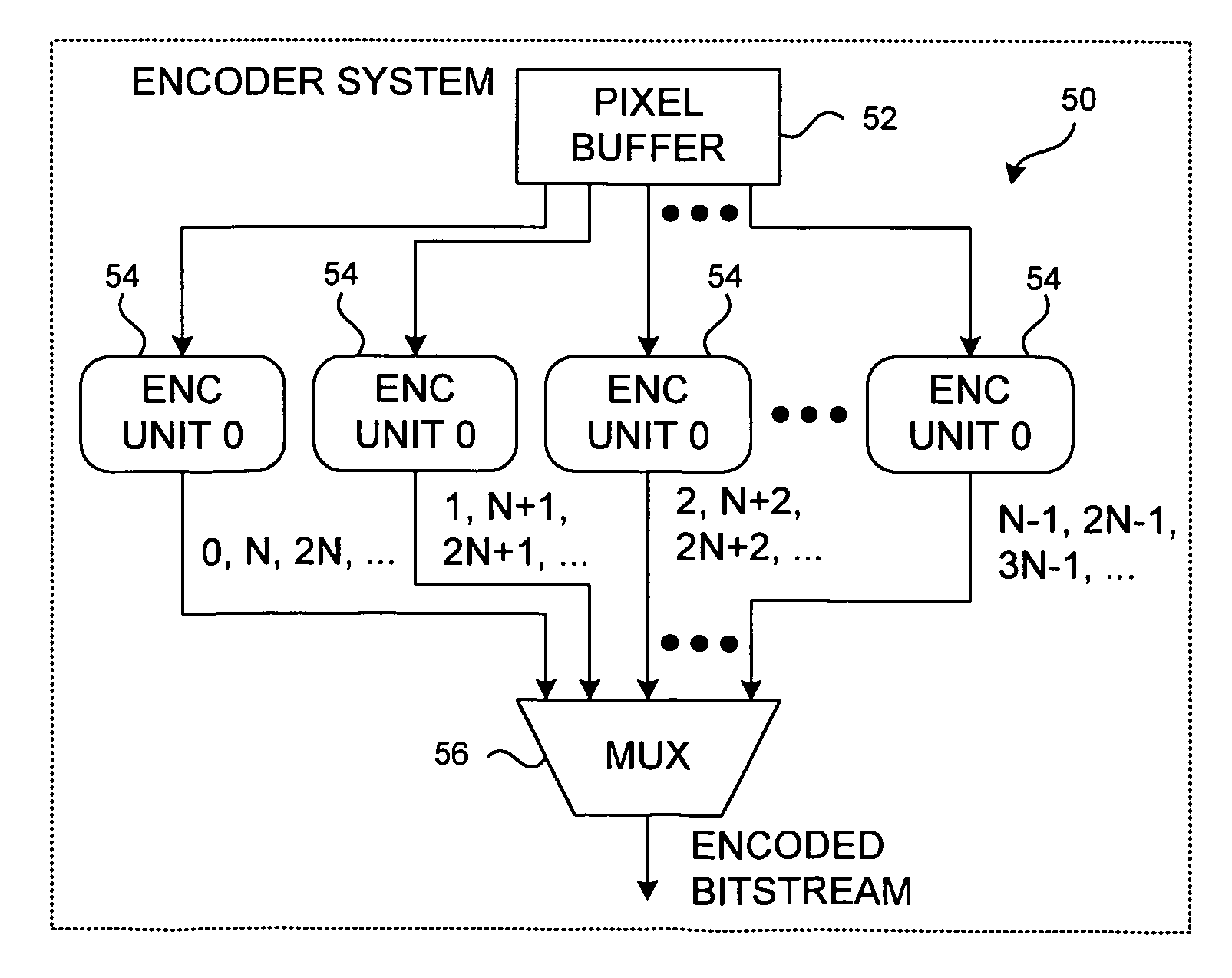

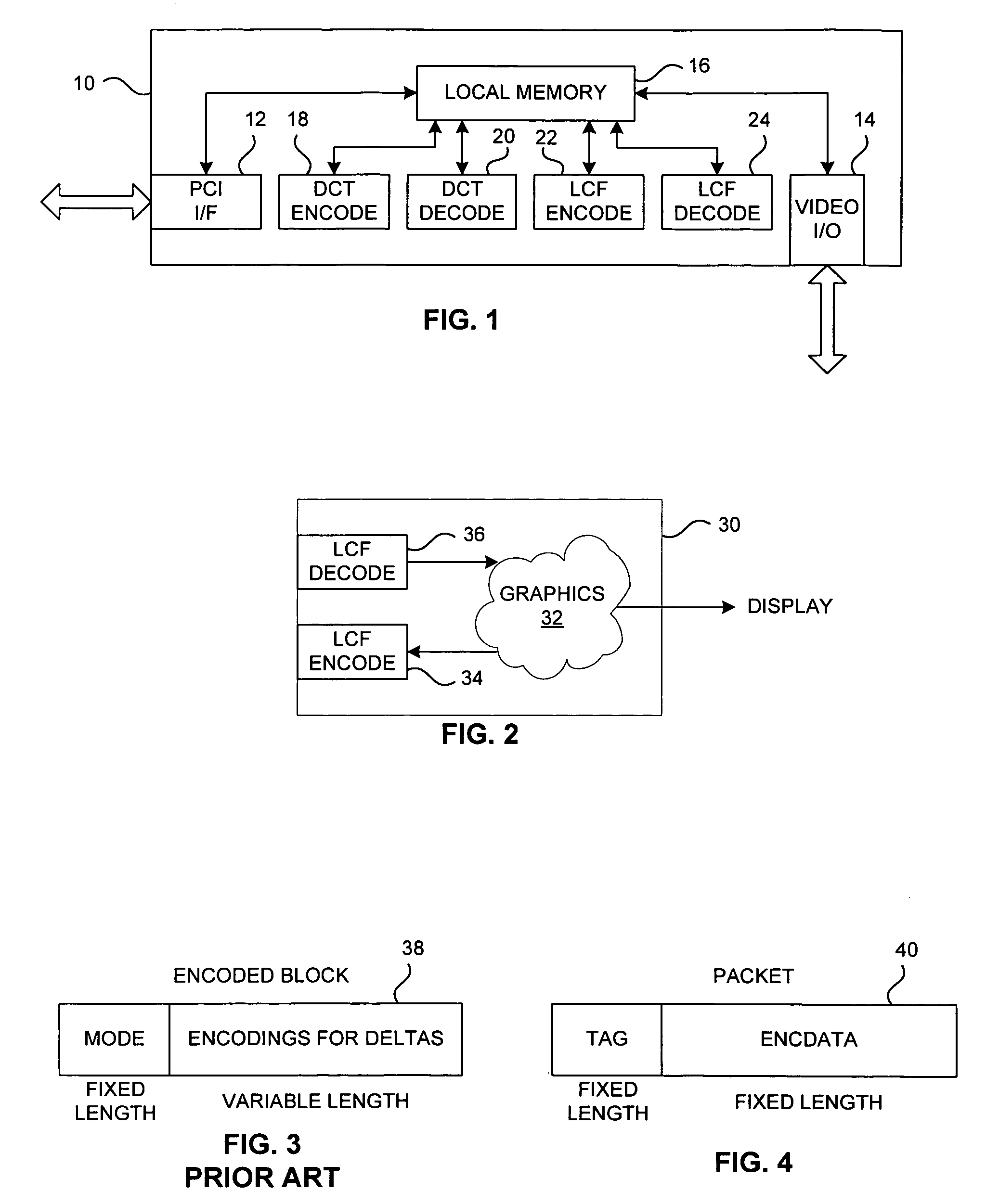

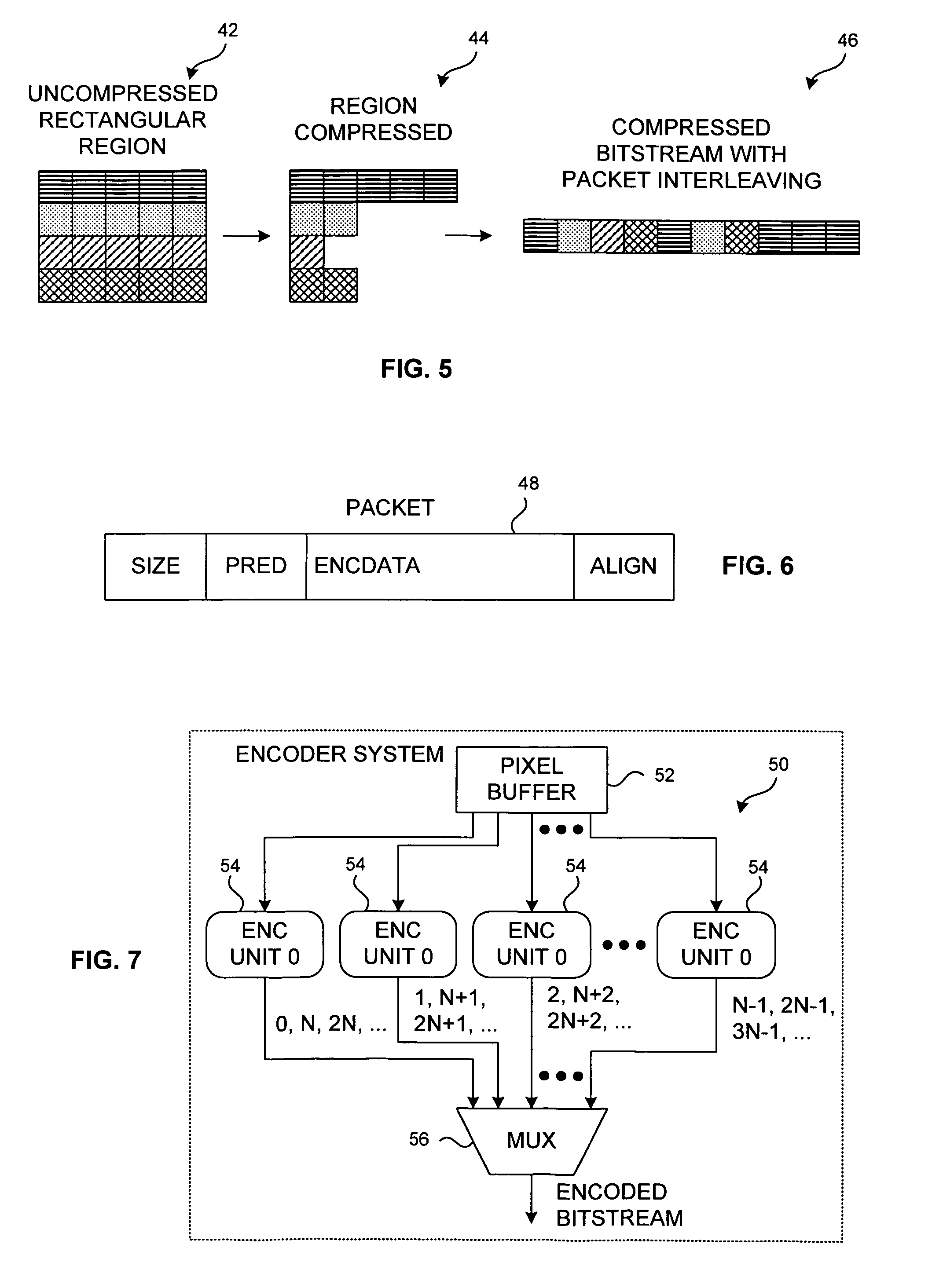

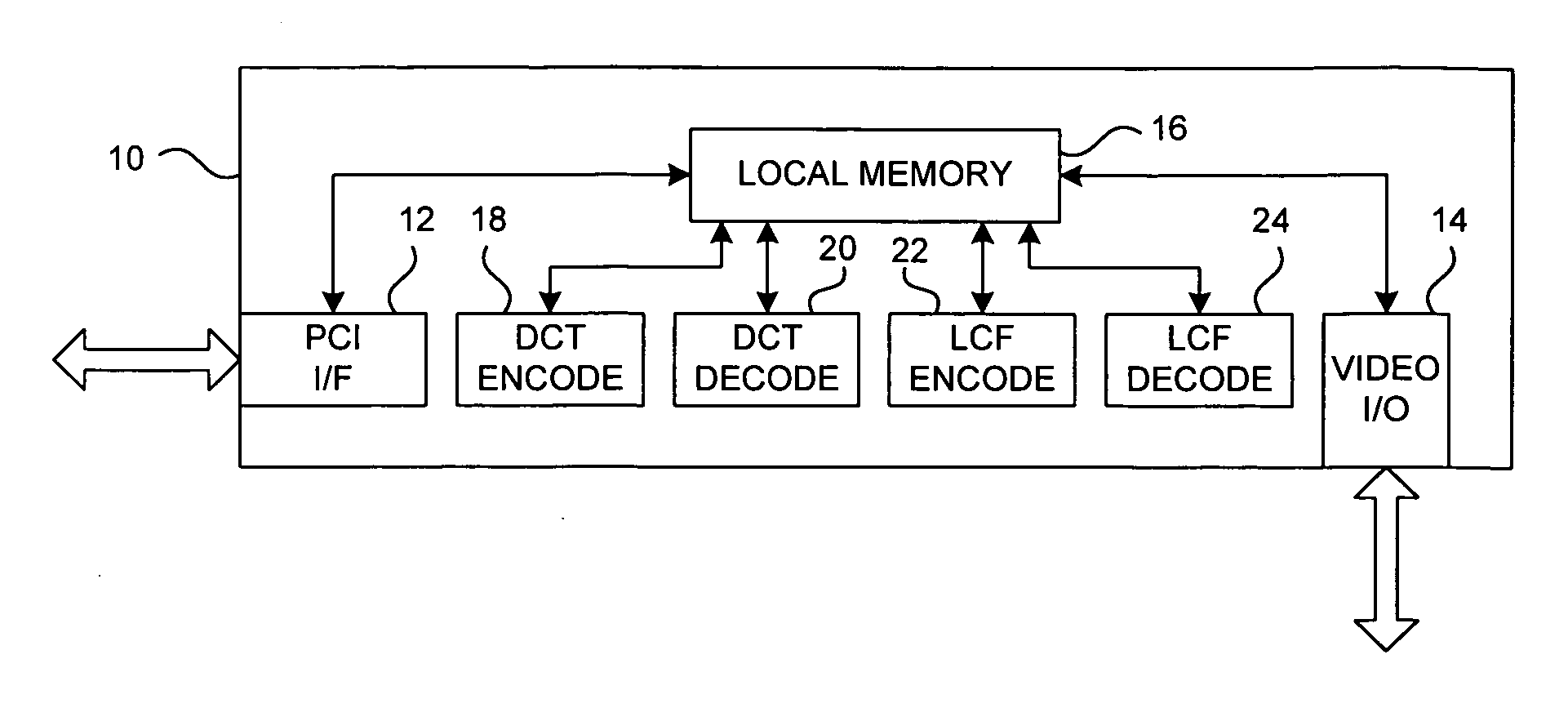

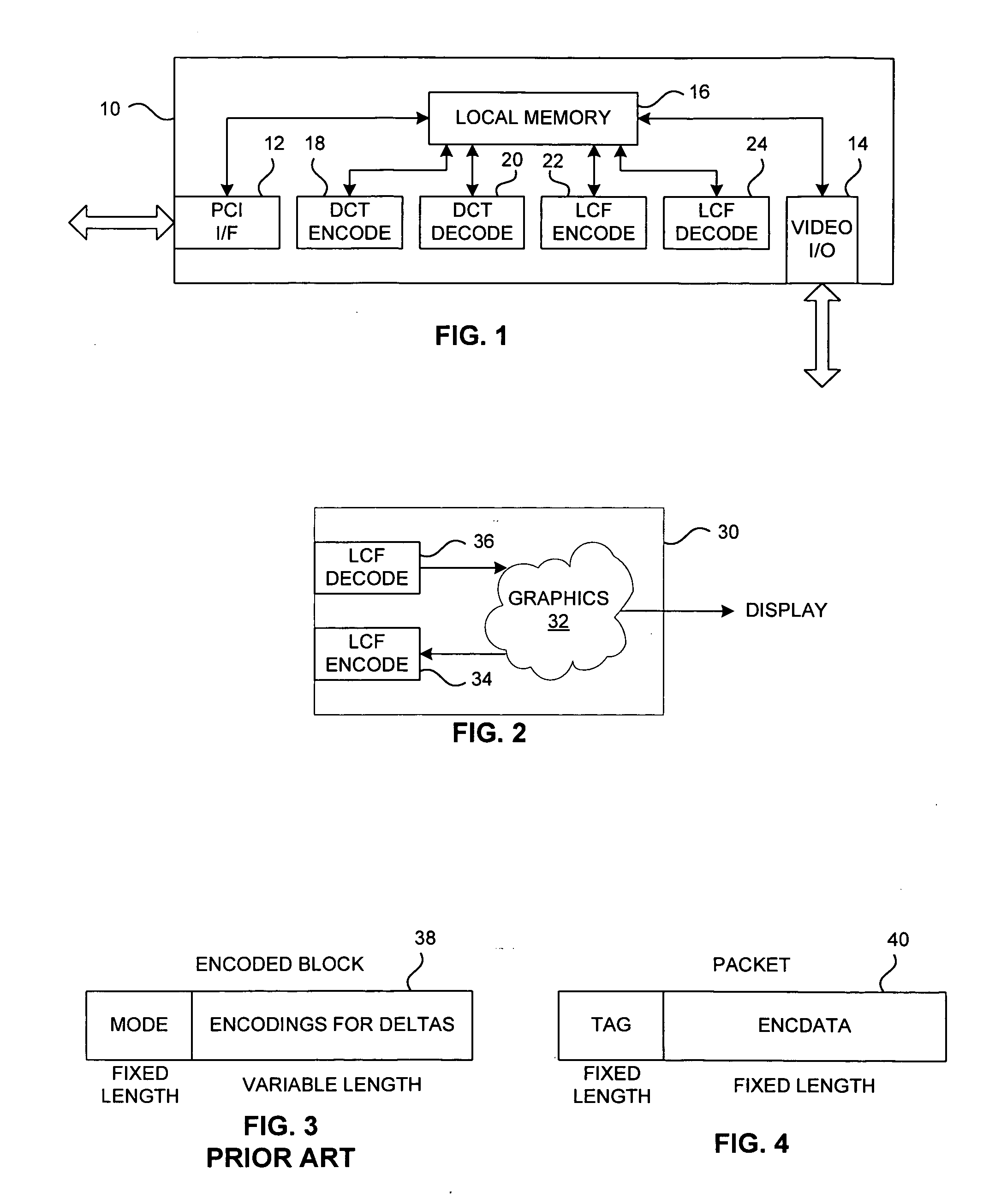

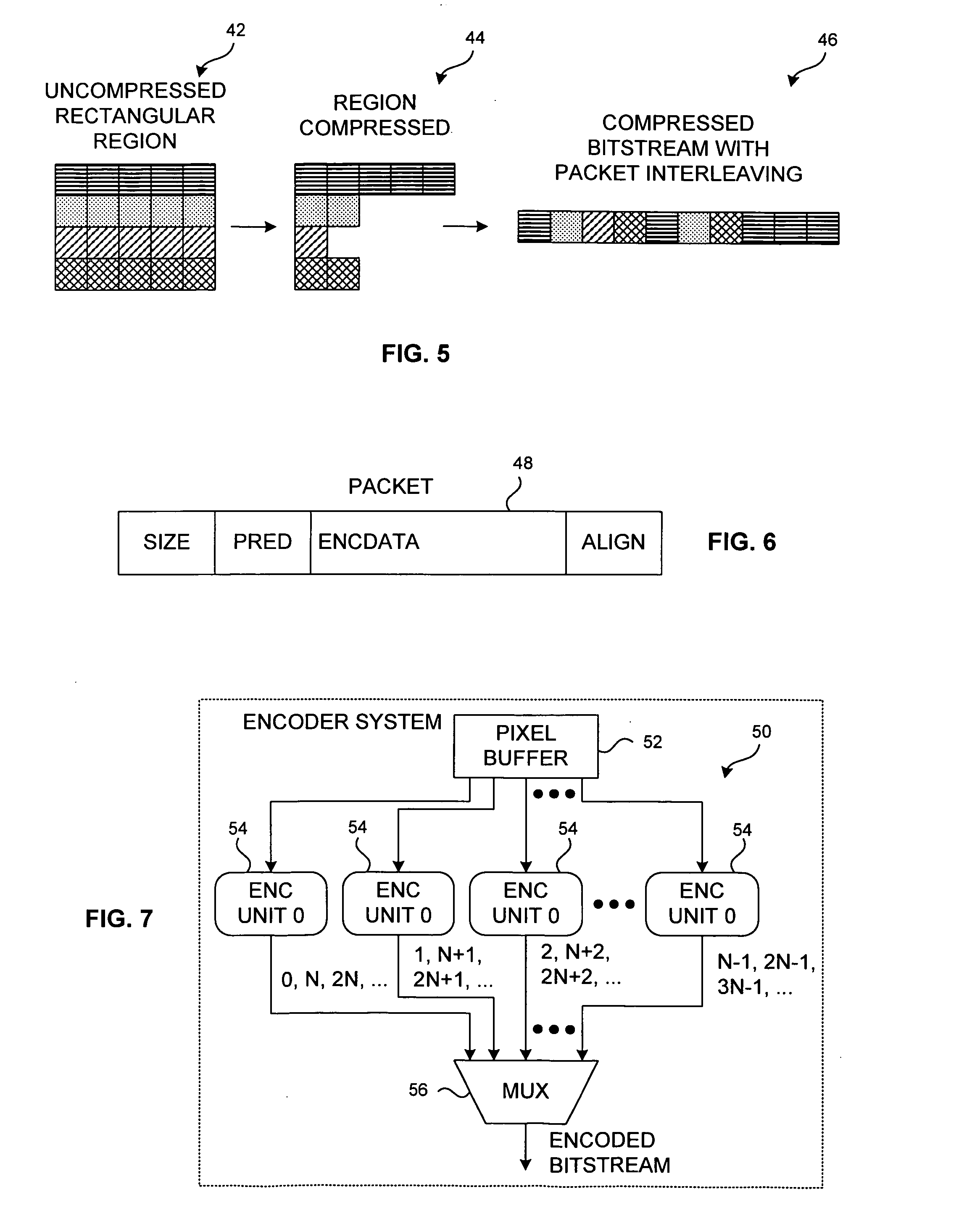

System and method using a packetized encoded bitstream for parallel compression and decompression

InactiveUS7180901B2Easy to parallelizeImprove performancePicture reproducers using cathode ray tubesPicture reproducers with optical-mechanical scanningComputer hardwareParallel compression

A system and method are disclosed for parallel compression and decompression of a bitstream. For compression, the bitstream is separated into a plurality of components, and the components are encoded using a compression algorithm. Packets are then constructed from the encoded components. At least one packet is associated with each encoded component and comprises header information and encoded data. The packets are combined into a packetized encoded bitstream. For decompression, the packets are separated from the packetized encoded bitstream using the header information. The packets are then decoded in parallel using a decompression algorithm to recover the encoded data. The plurality of components are reconstructed from the recovered encoded data and combined to-recover the bitstream.

Owner:MICROSOFT TECH LICENSING LLC

System and method using a packetized encoded bitstream for parallel compression and decompression

InactiveUS20050135433A1Easy to parallelizeImprove performanceColor television with pulse code modulationColor television with bandwidth reductionComputer hardwareParallel compression

A system and method are disclosed for parallel compression and decompression of a bitstream. For compression, the bitstream is separated into a plurality of components, and the components are encoded using a compression algorithm. Packets are then constructed from the encoded components. At least one packet is associated with each encoded component and comprises header information and encoded data. The packets are combined into a packetized encoded bitstream. For decompression, the packets are separated from the packetized encoded bitstream using the header information. The packets are then decoded in parallel using a decompression algorithm to recover the encoded data. The plurality of components are reconstructed from the recovered encoded data and combined to-recover the bitstream.

Owner:MICROSOFT TECH LICENSING LLC

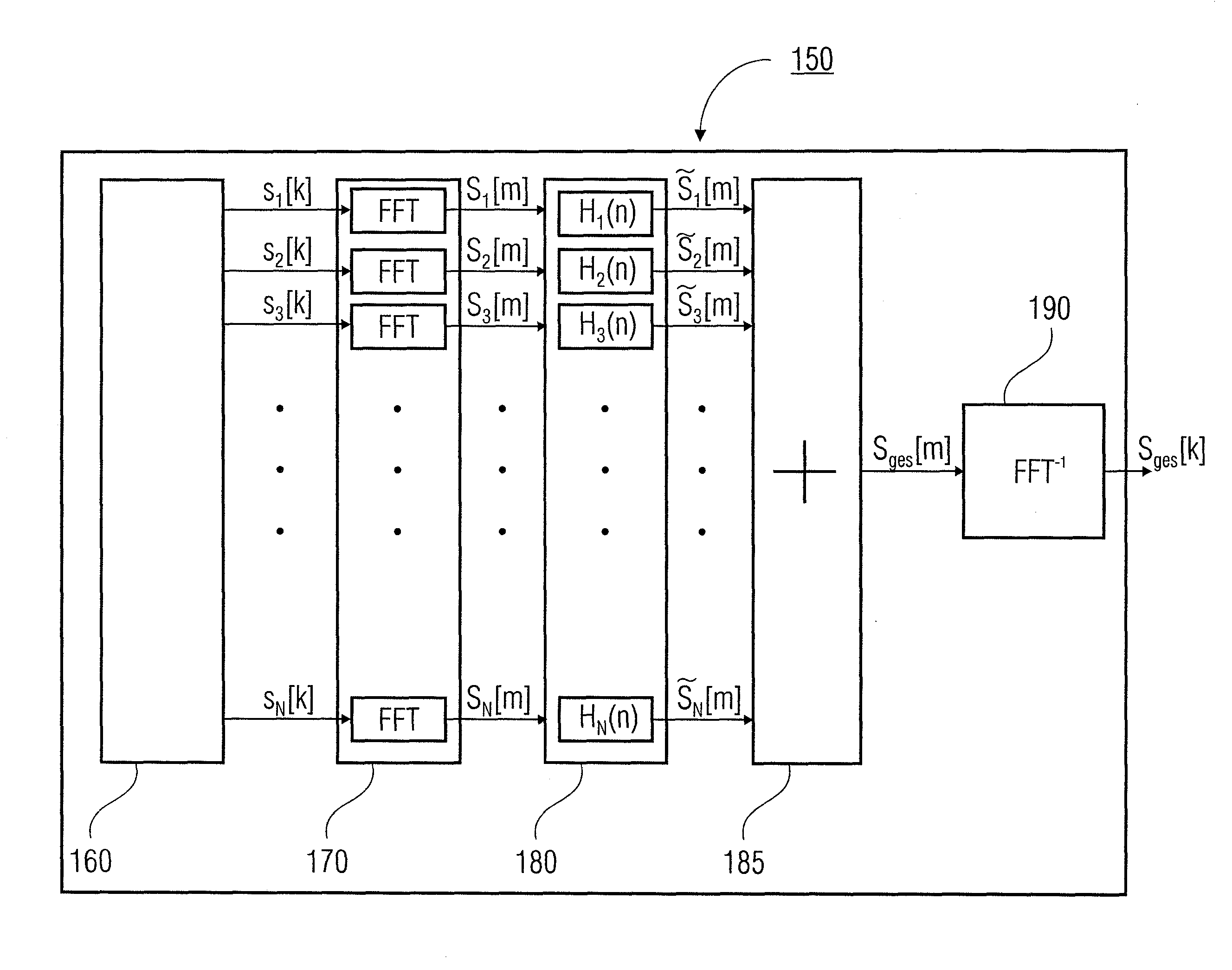

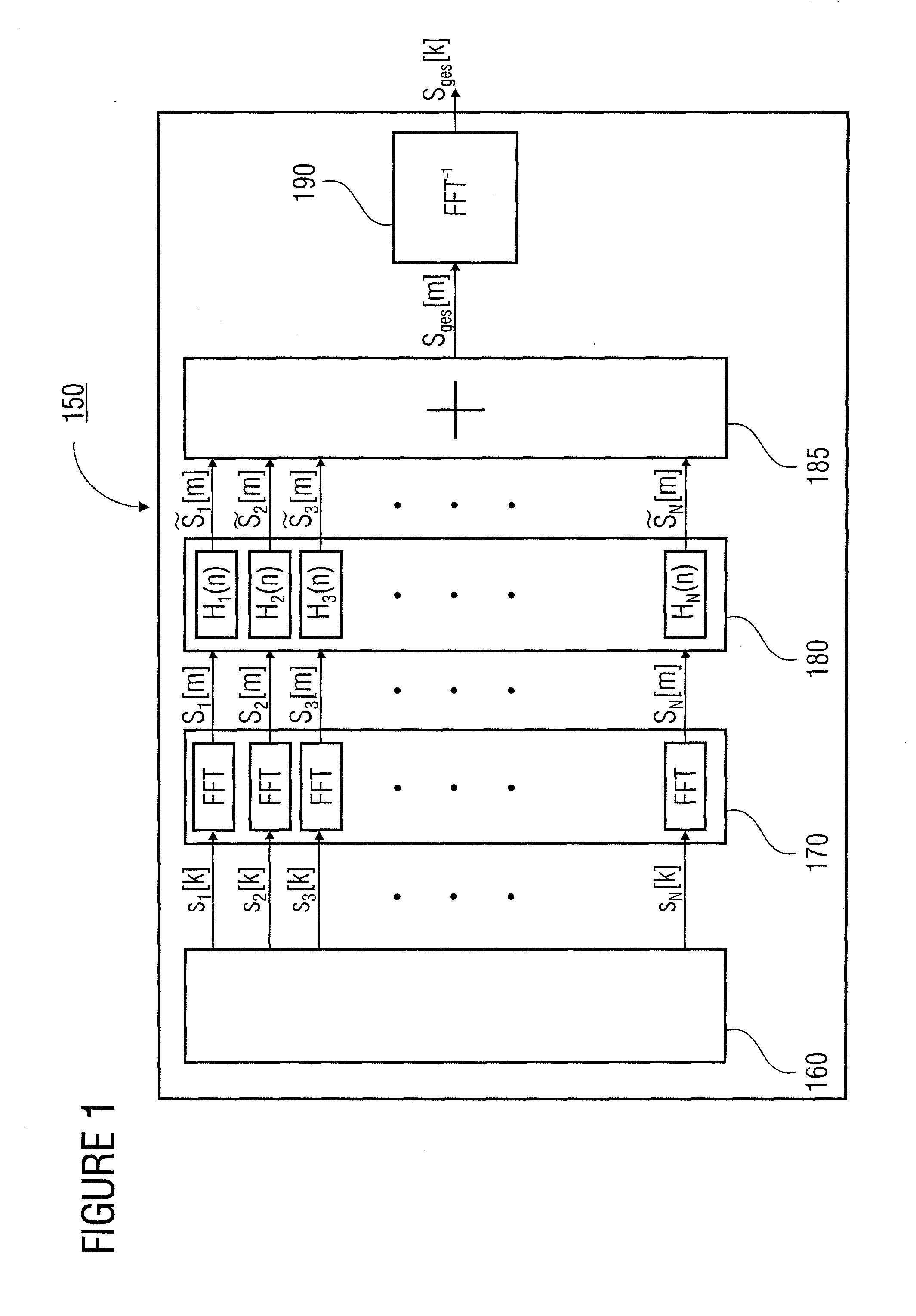

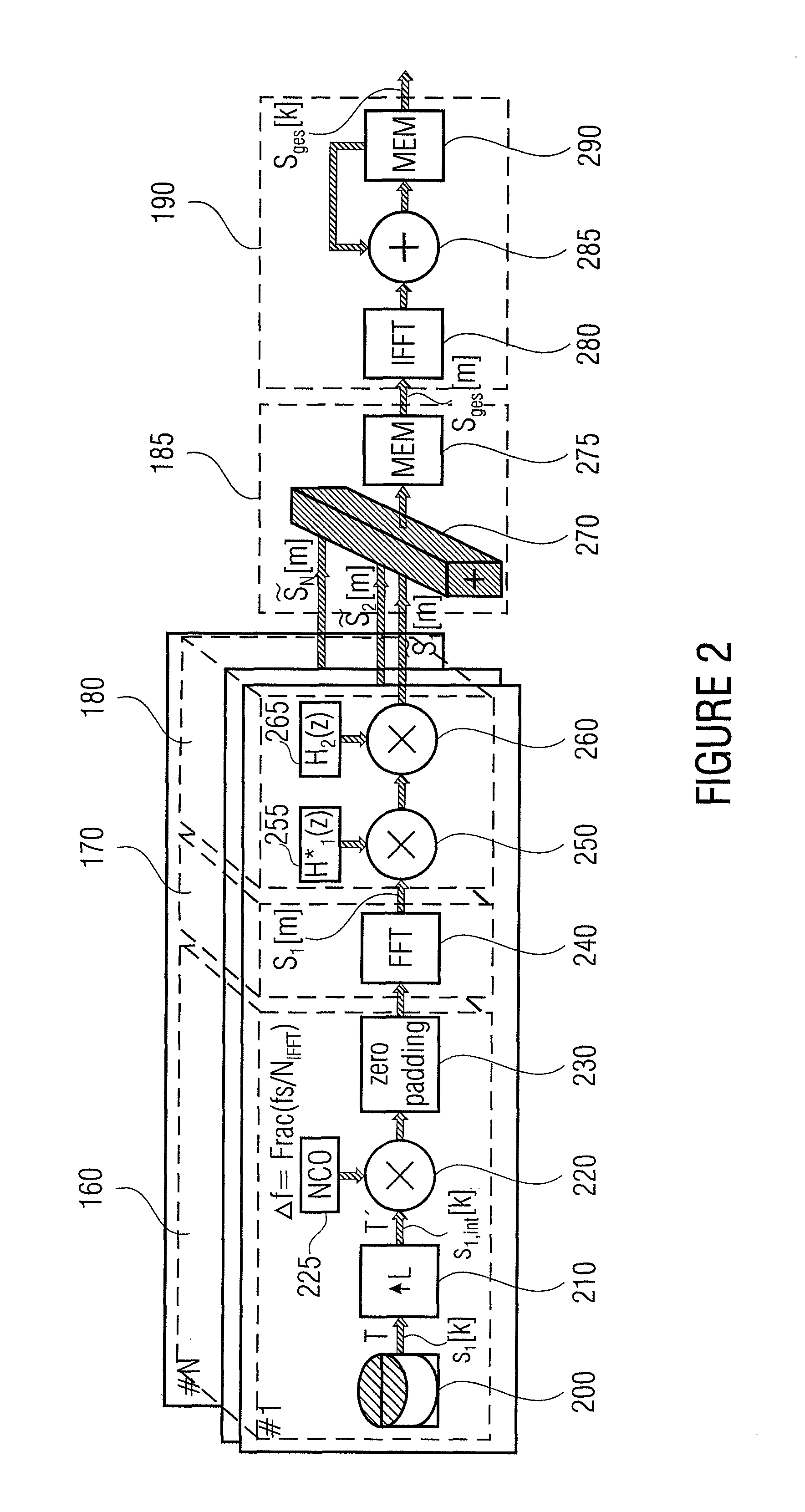

Concept for Realistic Simulation of a Frequency Spectrum

ActiveUS20100121617A1Low resource requirementHigh numberDigital computer detailsComputation using non-denominational number representationEngineeringFrequency domain

An apparatus for simulating a signal composed of a plurality of individual signals from respective signal locations at a simulation location, having a provider for providing the plurality of individual signals in the time domain, a transformer for transforming the individual signals to the frequency domain, a processor for processing the individual signals transformed to the frequency domain each depending on a signal channel existing between the simulation location and the respective signal location, a combiner for combining the processed individual signals transformed to the frequency domain to a combined signal, and a transformer for transforming the combined signal to the time domain for generating the simulated combined signal at the simulation location.

Owner:INNOVATIONSZENTRUM FUER TELEKOMMUNIKATIONSTECHNIK GMBH IZT

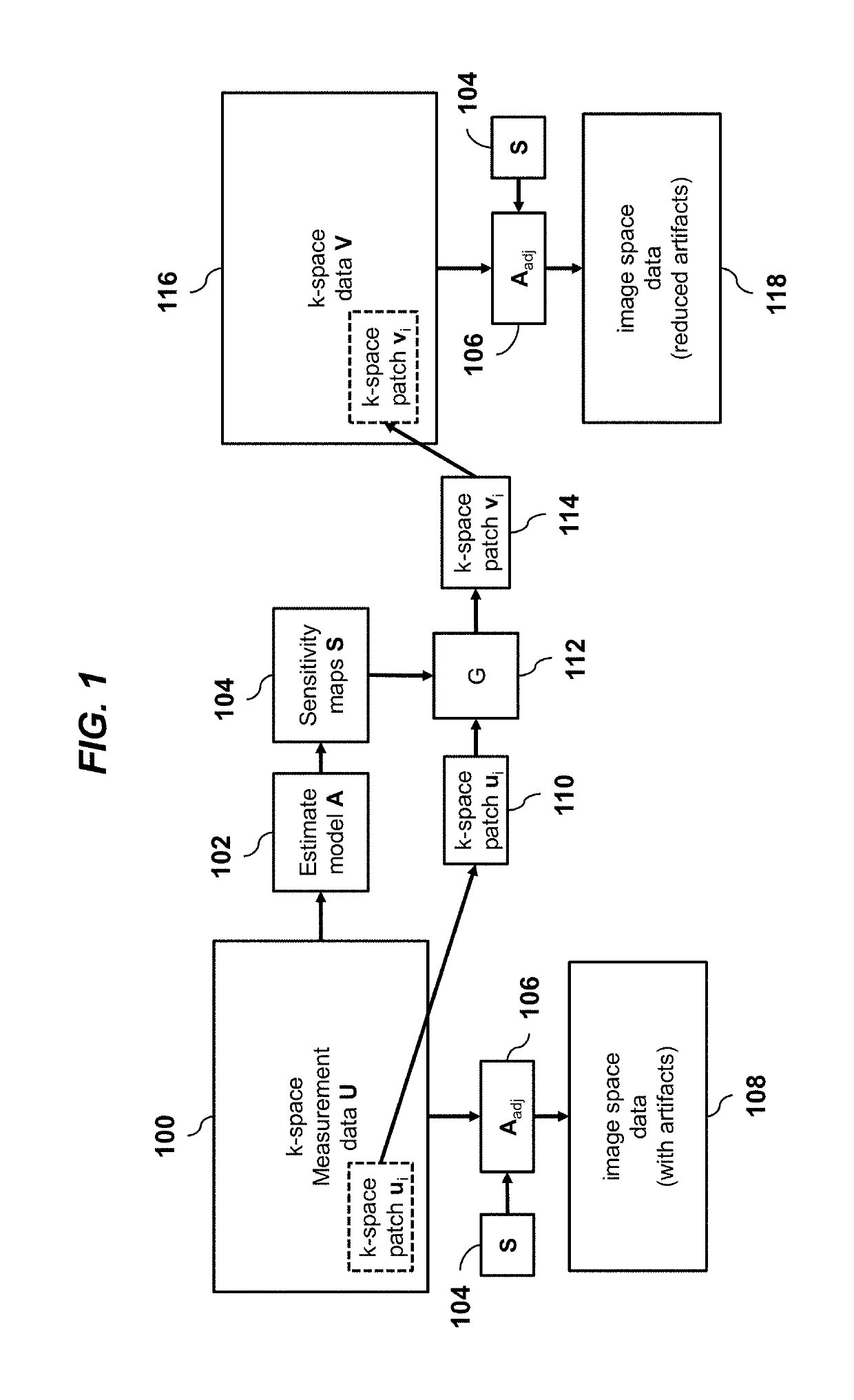

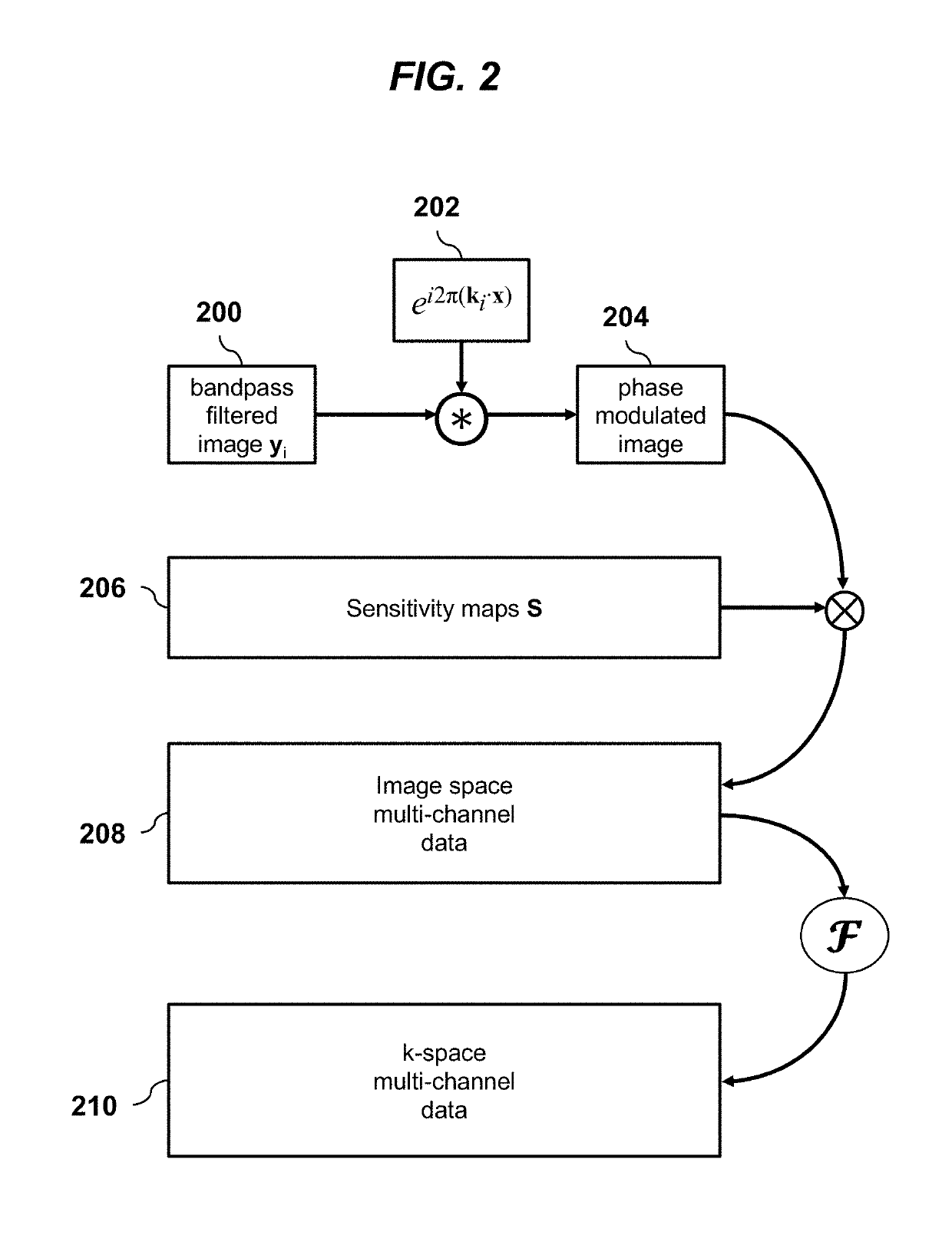

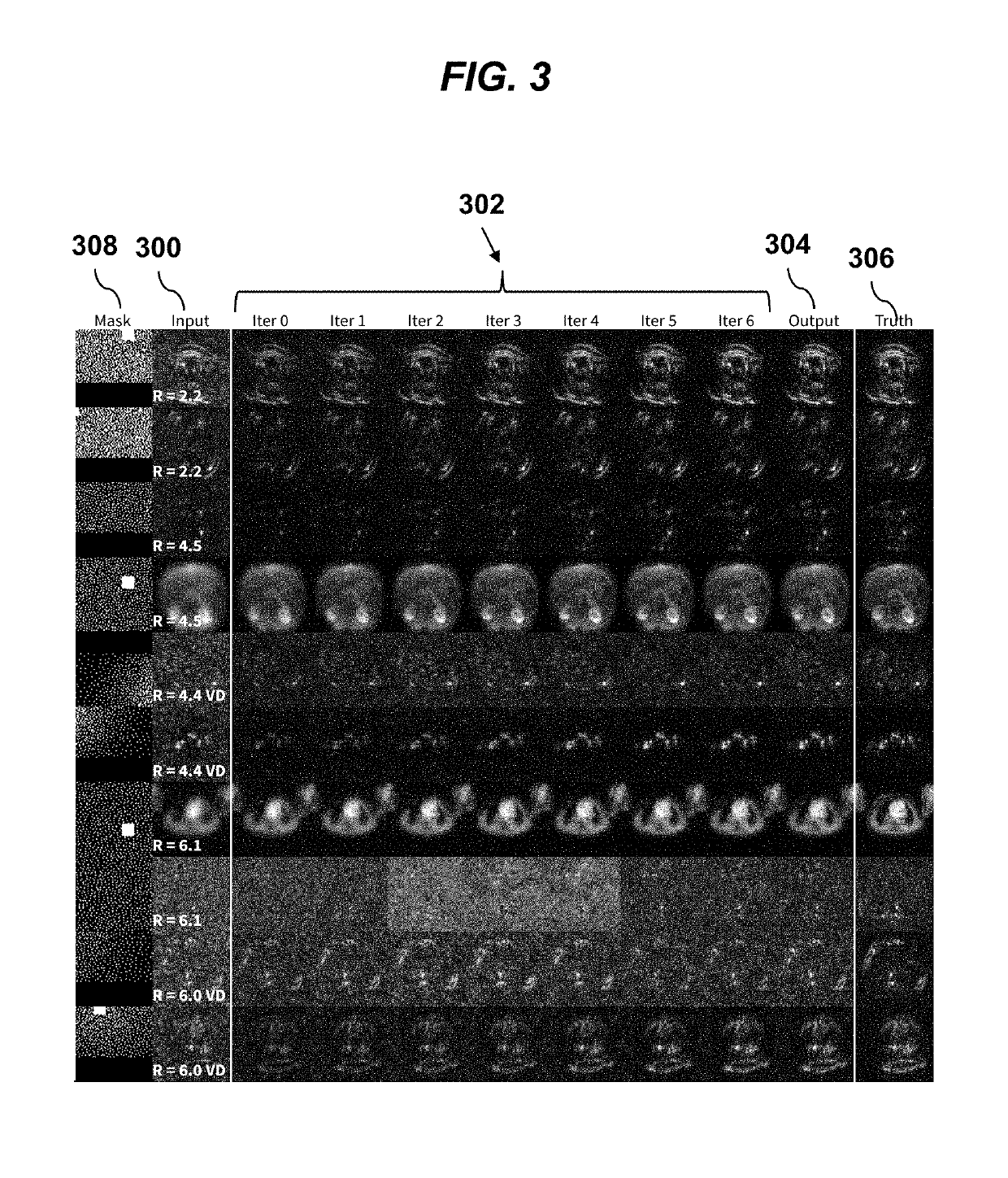

Highly-scalable image reconstruction using deep convolutional neural networks with bandpass filtering

ActiveUS20190257905A1Improve networking flexibilityMinimization requirementsImage enhancementImage analysisBandpass filteringField of view

A method for magnetic resonance imaging (MRI) scans a field of view and acquires sub-sampled multi-channel k-space data U. An imaging model A is estimated. Sub-sampled multi-channel k-space data U is divided into sub-sampled k-space patches, each of which is processed using a deep convolutional neural network (ConvNet) to produce corresponding fully-sampled k-space patches, which are assembled to form fully-sampled k-space data V, which is transformed to image space using the imaging model adjoint Aadj to produce an image domain MRI image. The processing of each k-space patch ui preferably includes applying the k-space patch ui as input to the ConvNet to infer an image space bandpass-filtered image yi, where the ConvNet comprises repeated de-noising blocks and data-consistency blocks; and estimating the fully-sampled k-space patch vi from the image space bandpass-filtered image yi using the imaging model A and a mask matrix.

Owner:THE BOARD OF TRUSTEES OF THE LELAND STANFORD JUNIOR UNIV

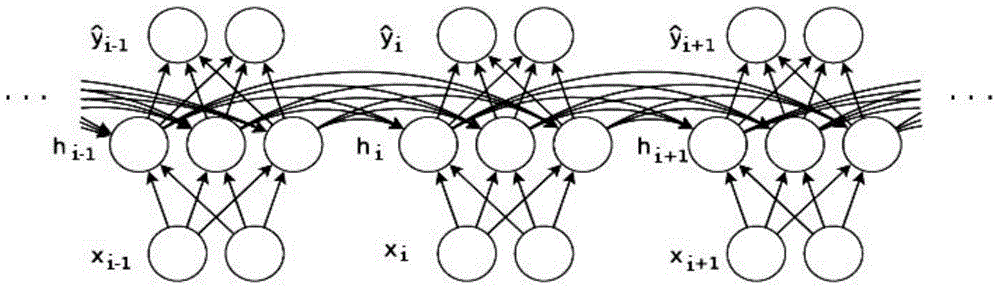

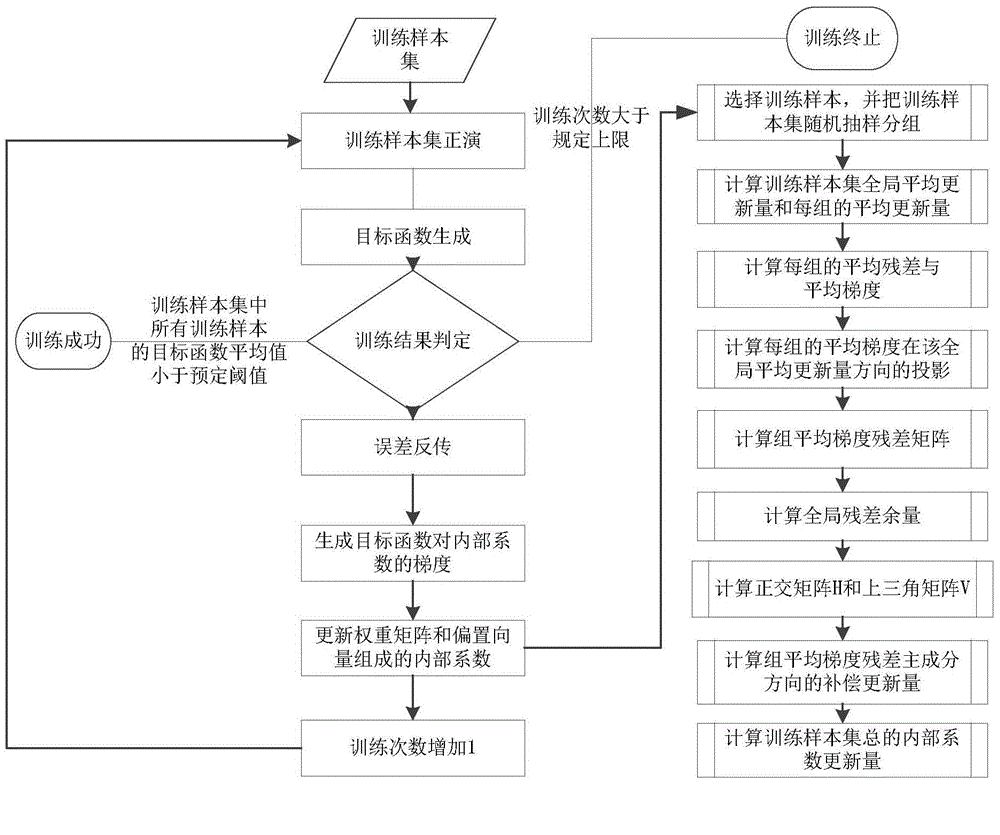

Quick training method of large-scale data recurrent neutral network (RNN)

InactiveCN104598972AInternal Coefficient ImprovementsIncrease training speedBiological neural network modelsLarge scale dataErrors and residuals

The invention relates to a quick training method of large-scale data recurrent neutral network (RNN), and belongs to the technical field of machine learning. The method comprises the steps of synchronously updating large-scale data of internal coefficients in the average gradient direction and the gradient residual main component direction to quickly train the generalized regression neural network; performing error back propagation to obtain the gradient of the target functions at each training sample to the internal coefficient; grouping the training samples; performing weighted averaging for the whole training sample set and the gradients of each group according to the target function value of each training sample; updating the internal coefficients in the global average gradient direction and the residual main component direction that and the group average gradient is orthogonal to the global average gradient. With the adoption of the method, the gradient information of each training sample can be effectively utilized with relatively small calculation cost to reduce the iteration steps can be decreased, so as to increase the calculation efficiency of RNN training process.

Owner:TSINGHUA UNIV

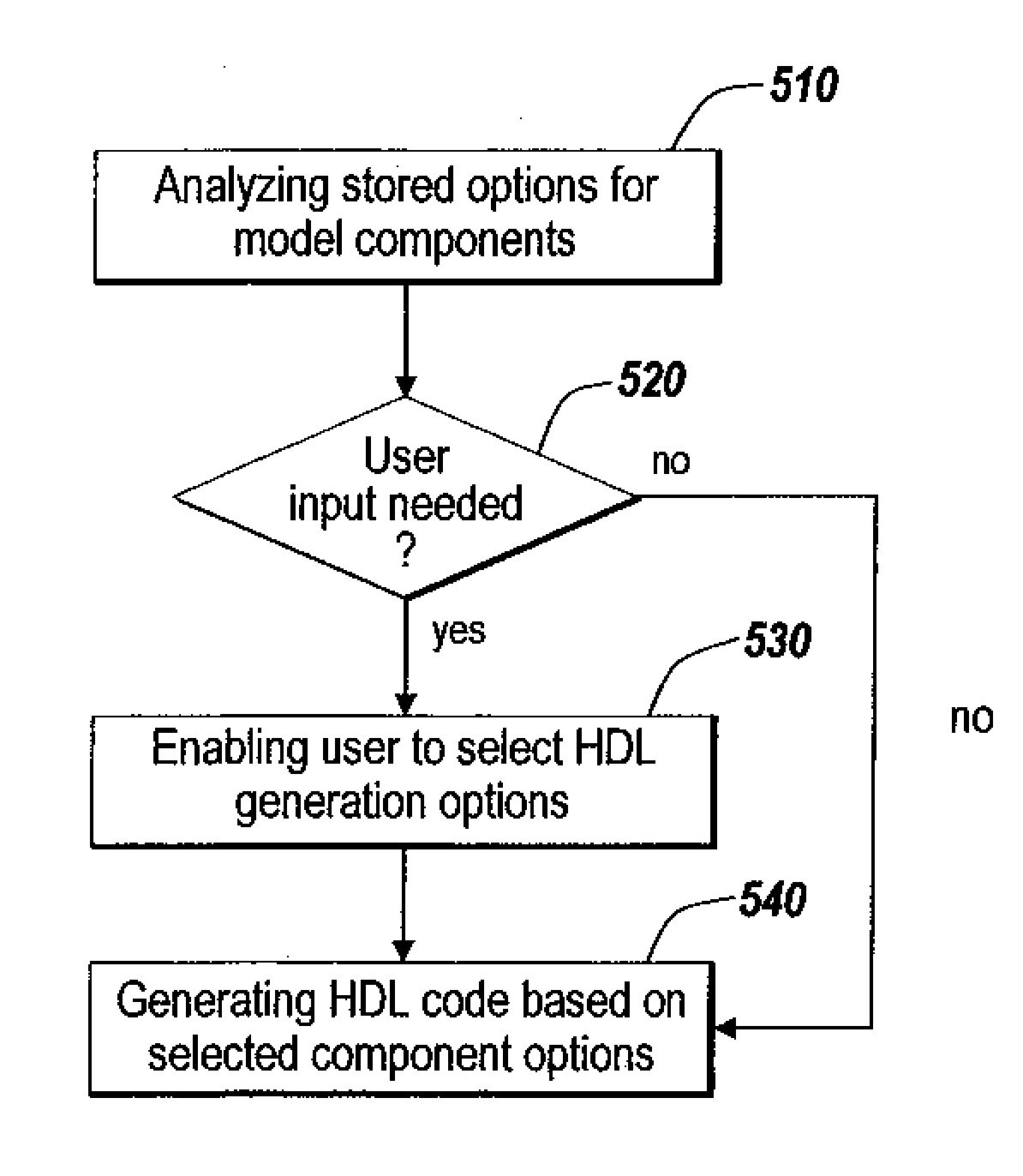

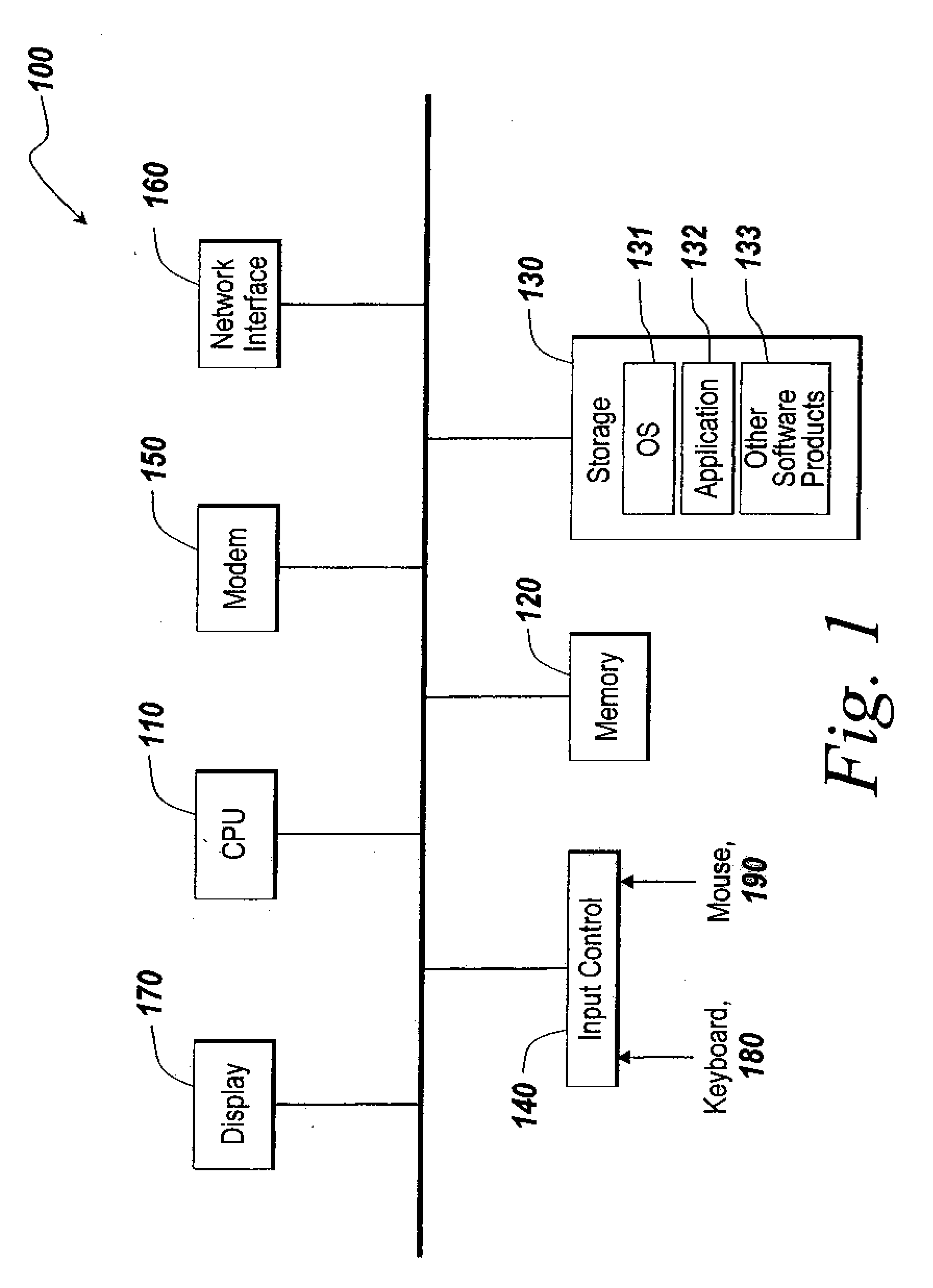

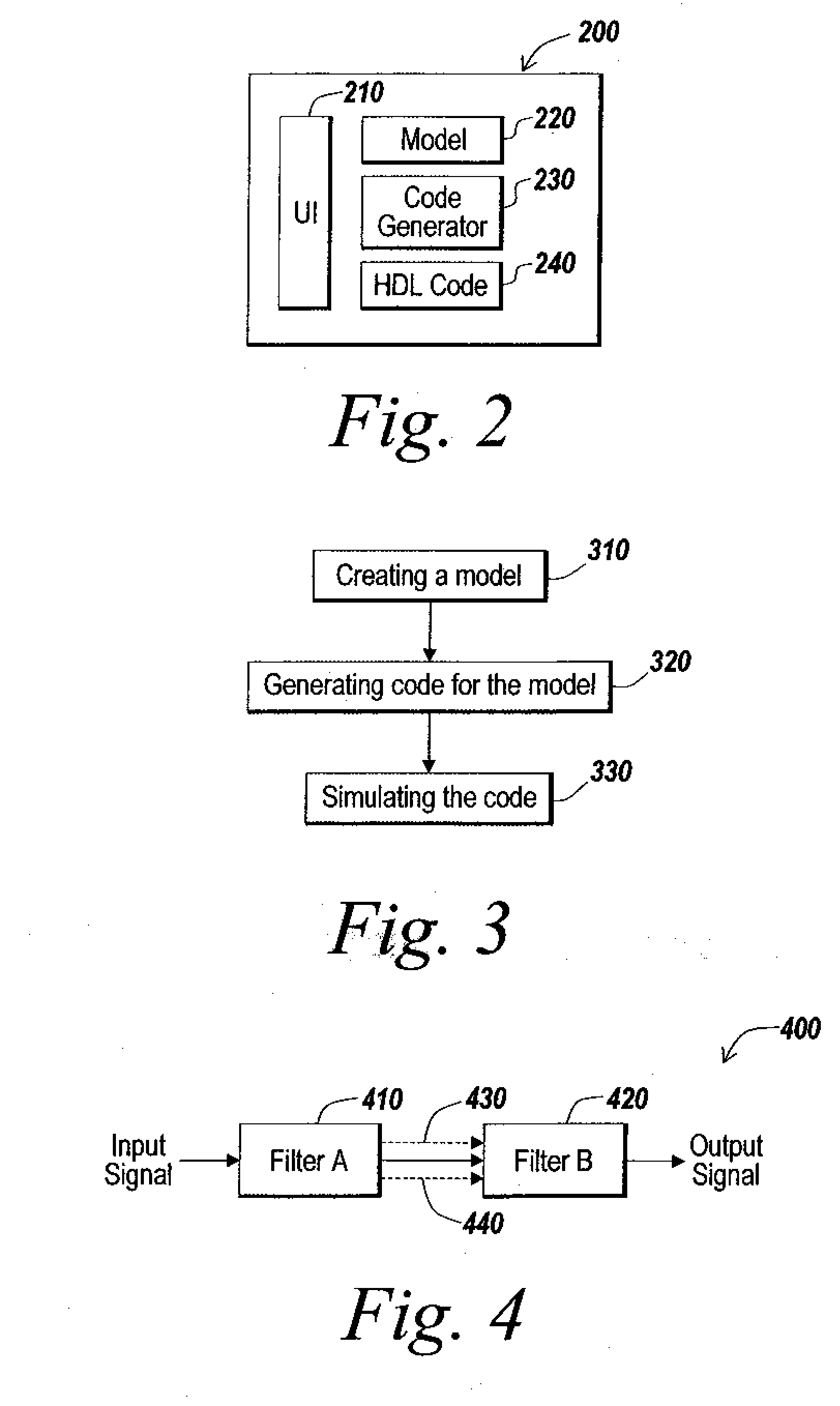

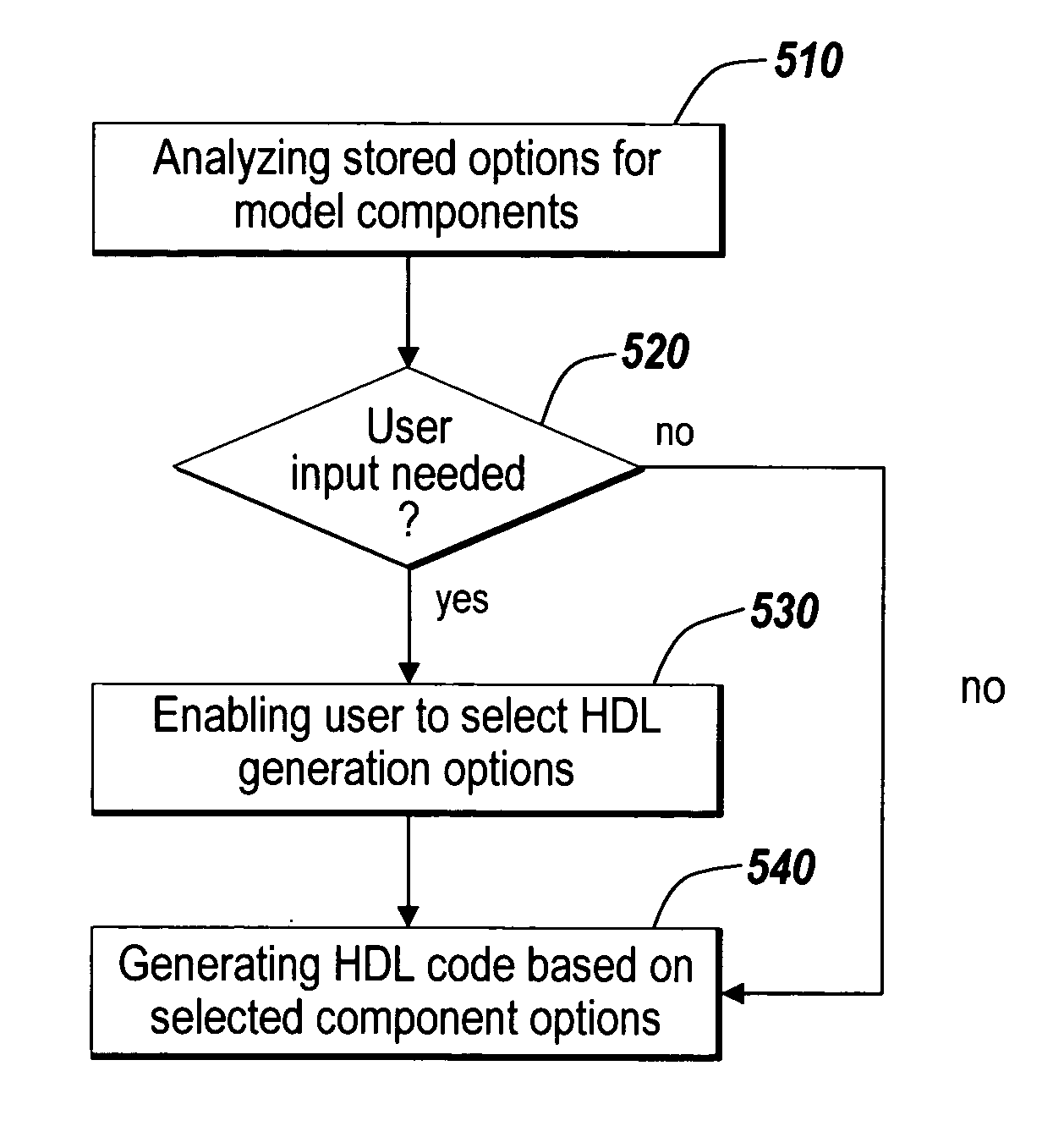

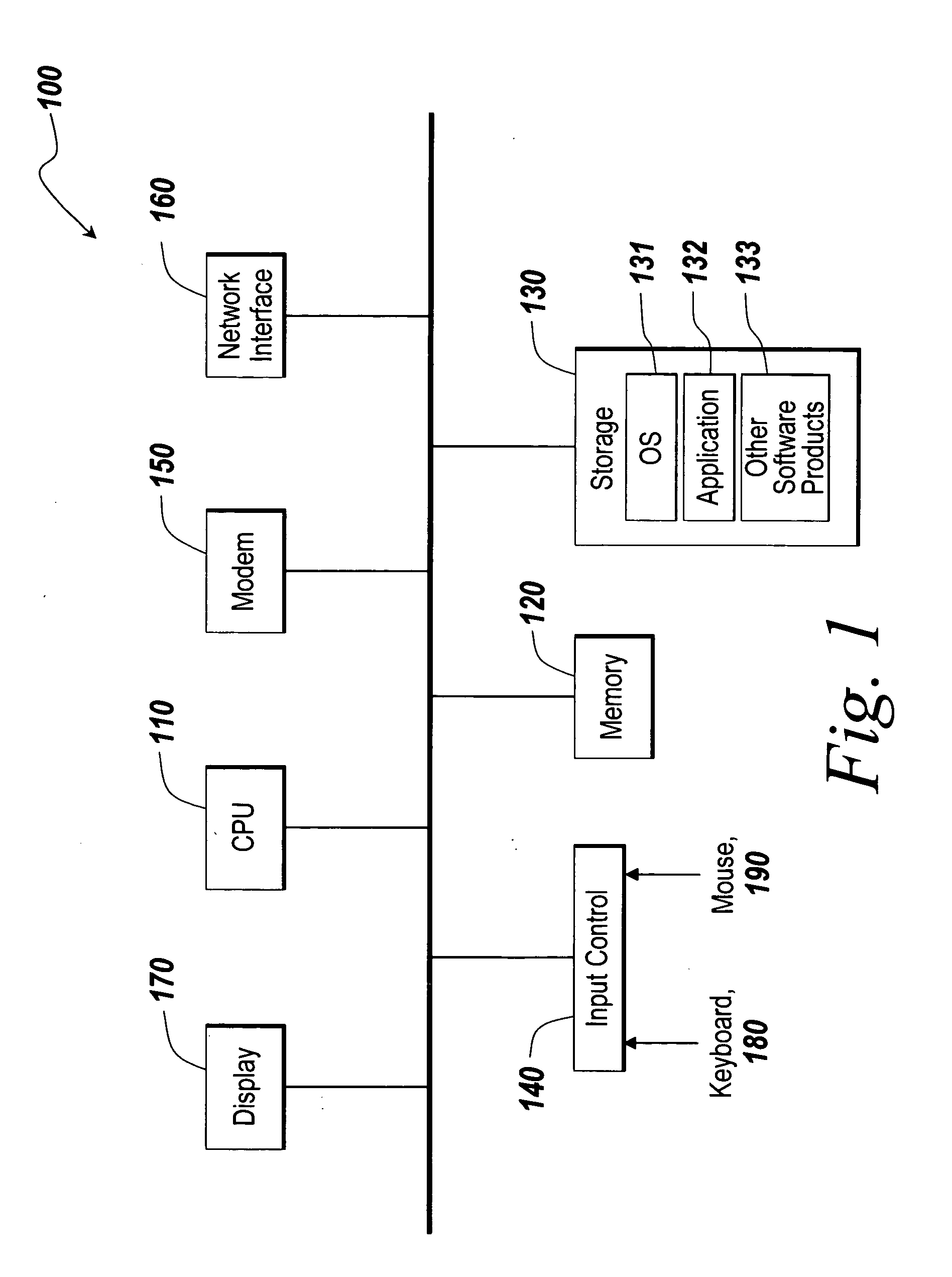

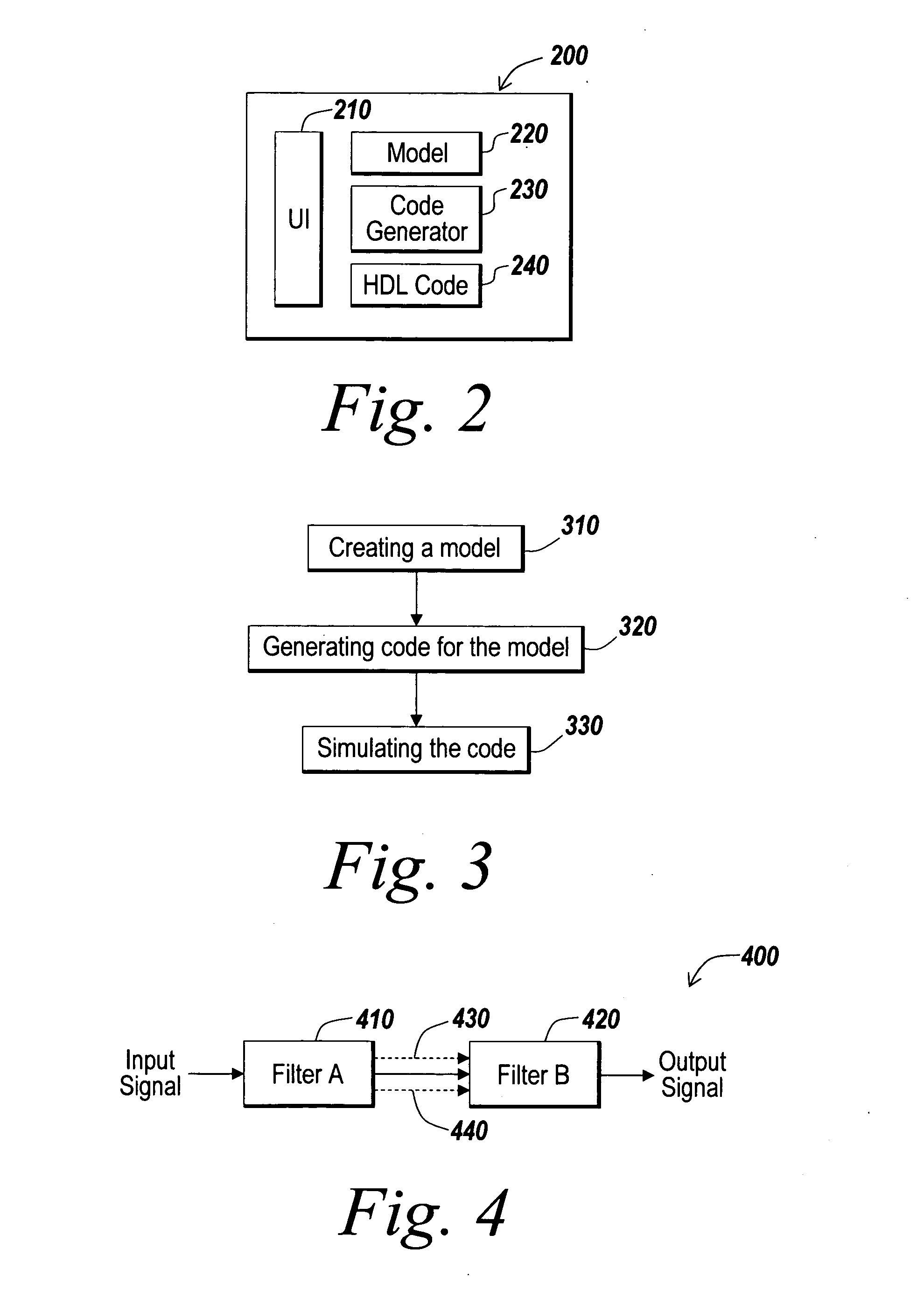

Hardware definition language generation for frame-based processing

ActiveUS20090013301A1Increased latencyMinimized in sizeCAD circuit designSoftware simulation/interpretation/emulationProgramming languageFrame based

A method generates hardware description language (HDL) code from a model having a plurality of components, including at least one component that processes frame-based input data. A selected preference is received for implementing the frame-based component. The generated HDL code includes a hardware implementation of the frame-based component that satisfies the selected preference.

Owner:THE MATHWORKS INC

Image decoding apparatus

InactiveUS7418146B2Easy to parallelizeImprove versatilityCode conversionCharacter and pattern recognitionProcessor registerComputer science

Coded data are inputted from a stream analyzing unit to an entropy decoding unit. A group of peripheral information registers stores peripheral information on a target pixel for estimating a context used for arithmetic decoding of the coded data. Based on the peripheral information stored in the group of peripheral registers, a context estimation unit estimates a context and delivers the estimated context to an arithmetic decoding unit. The arithmetic decoding unit decodes the coded data based on a context label, then derives a decision and supplies the decision to an inverse quantization unit. The peripheral information stored in the group of peripheral registers is updated by a decoding result of the arithmetic decoding unit in the same cycle as the decoding.

Owner:SANYO ELECTRIC CO LTD

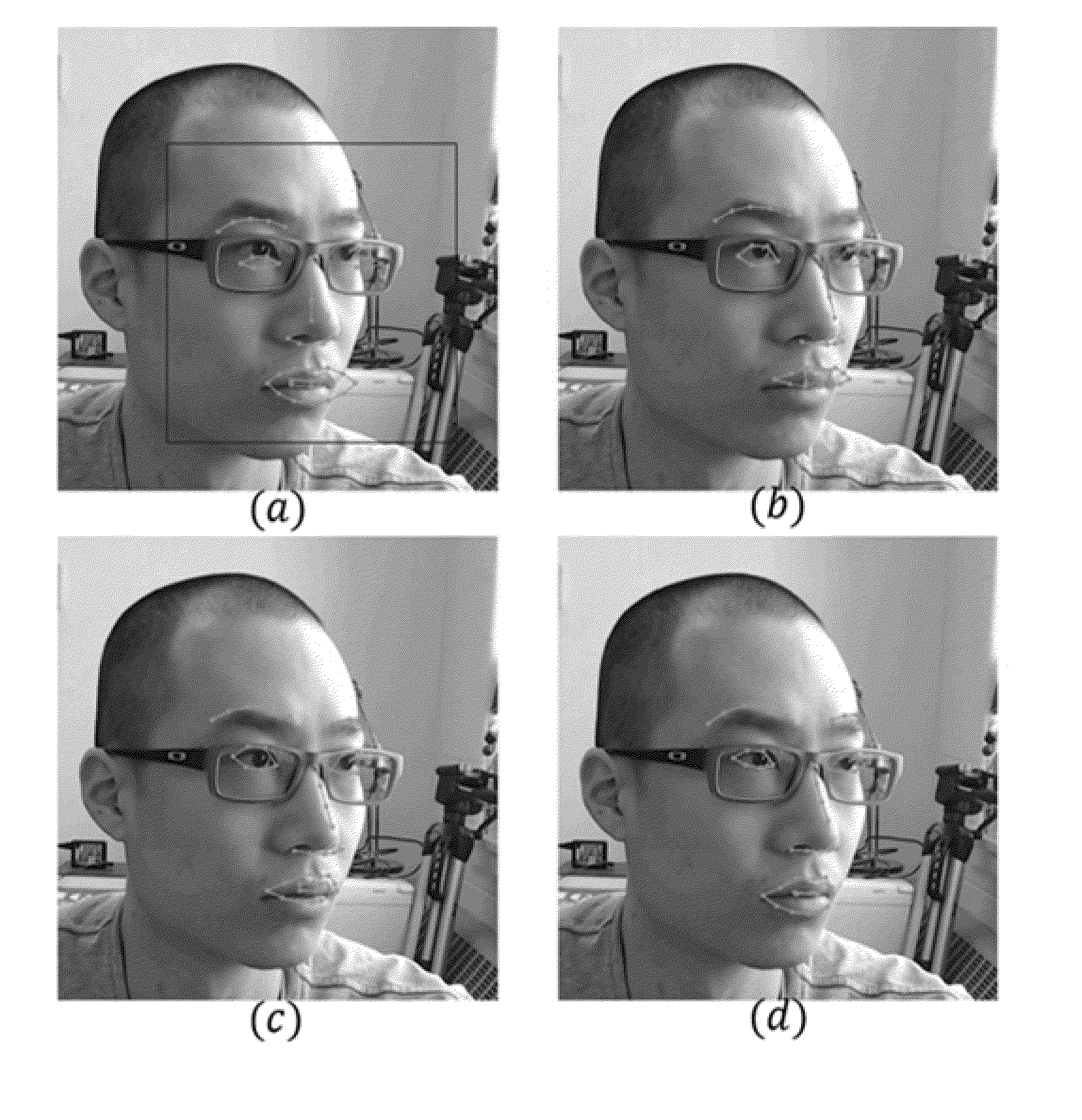

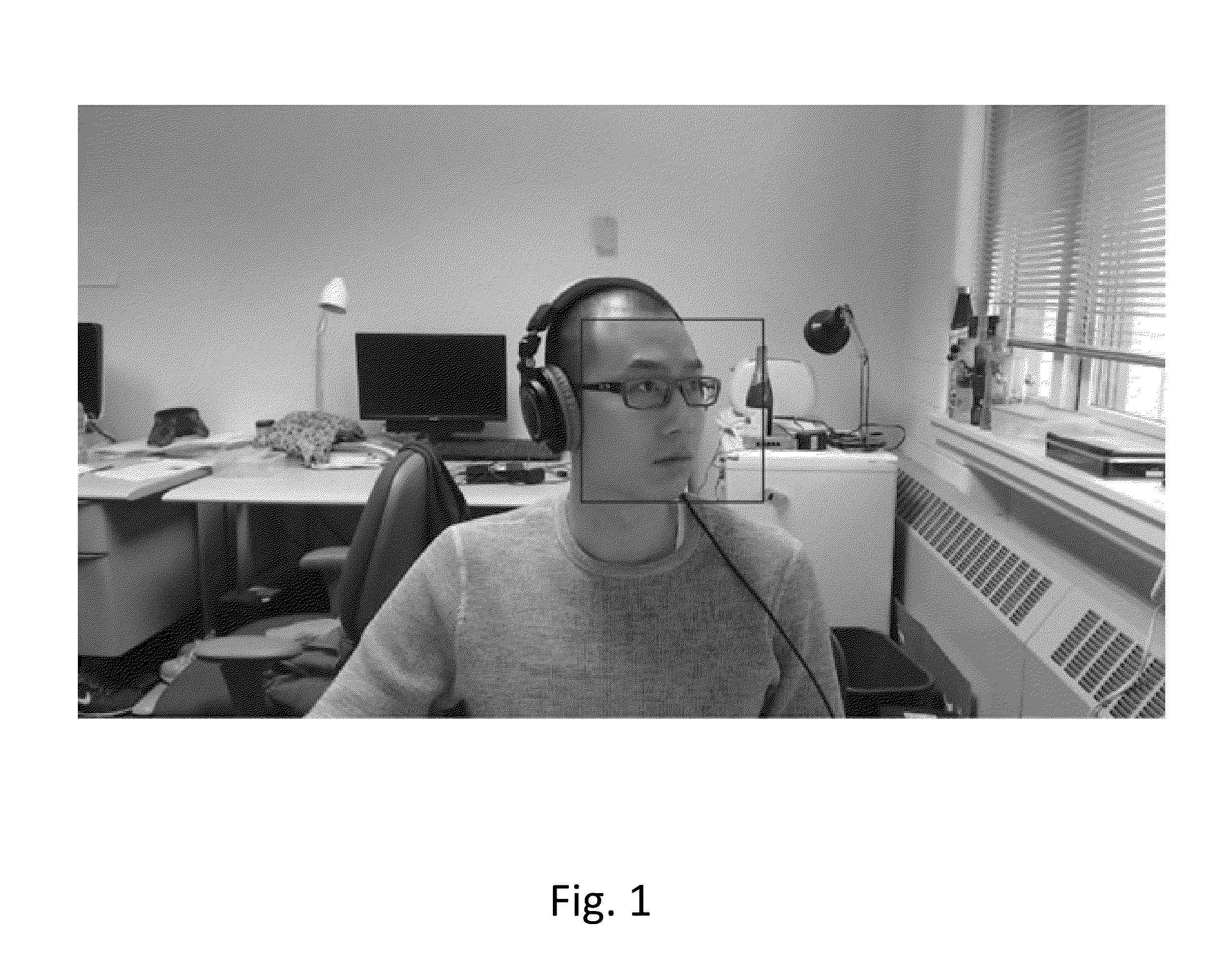

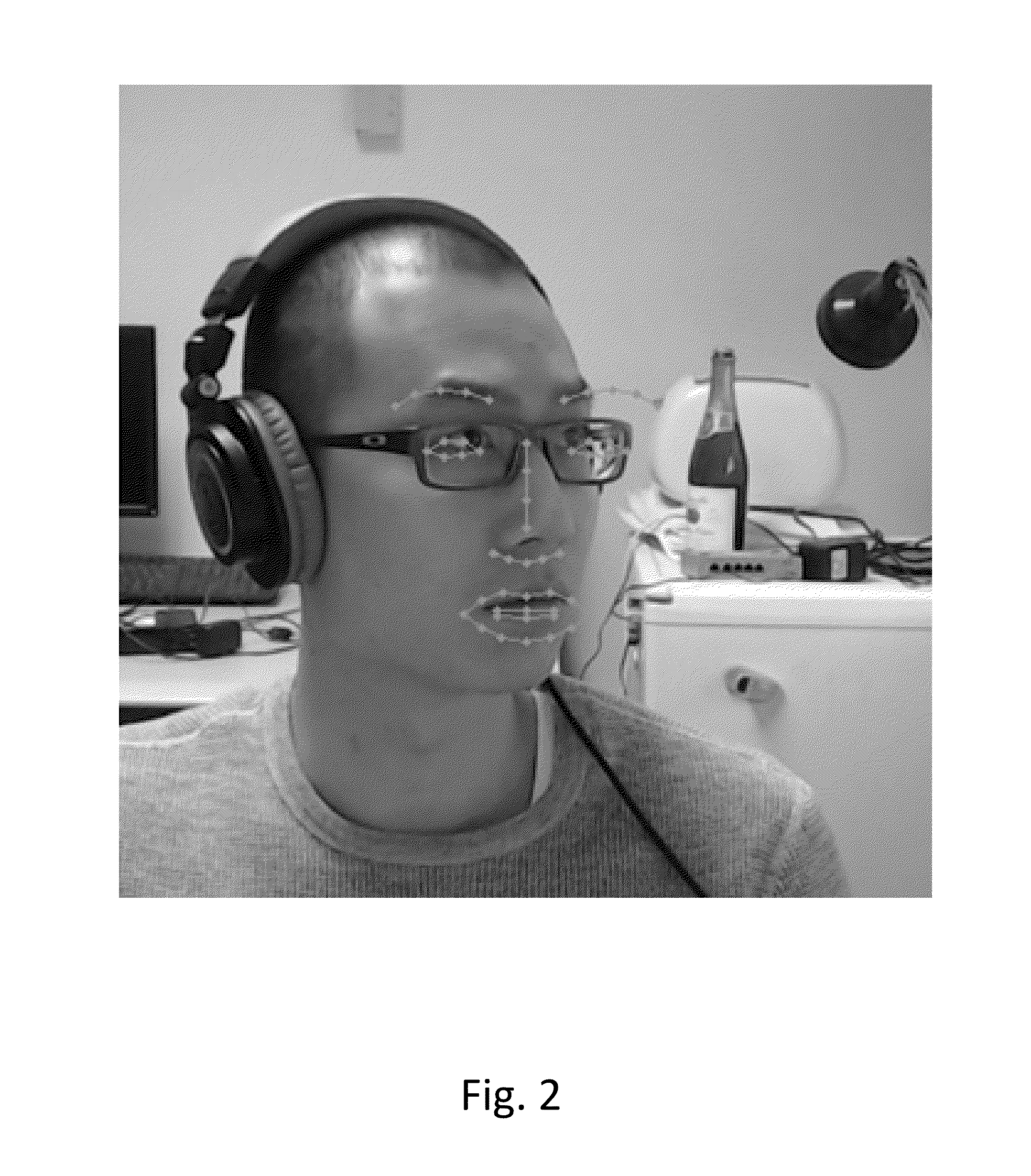

System and Method for Detecting and Tracking Facial Features In Images

ActiveUS20160275339A1Easy to parallelizeEasily vectorizedImage enhancementImage analysisMobile phoneTime processing

The present invention relates to a system for detecting and tracking facial features in images and can be used in conjunction with a camera. Given a camera, the system will detect facial landmarks in images. The present invention includes software for real time, accurate facial feature detection and tracking in unconstrained images and videos. The present invention is better, more robust and faster than existing approaches and can be implemented very efficiently allowing real-time processing, even on low-power devices, such as mobile phones.

Owner:CARNEGIE MELLON UNIV

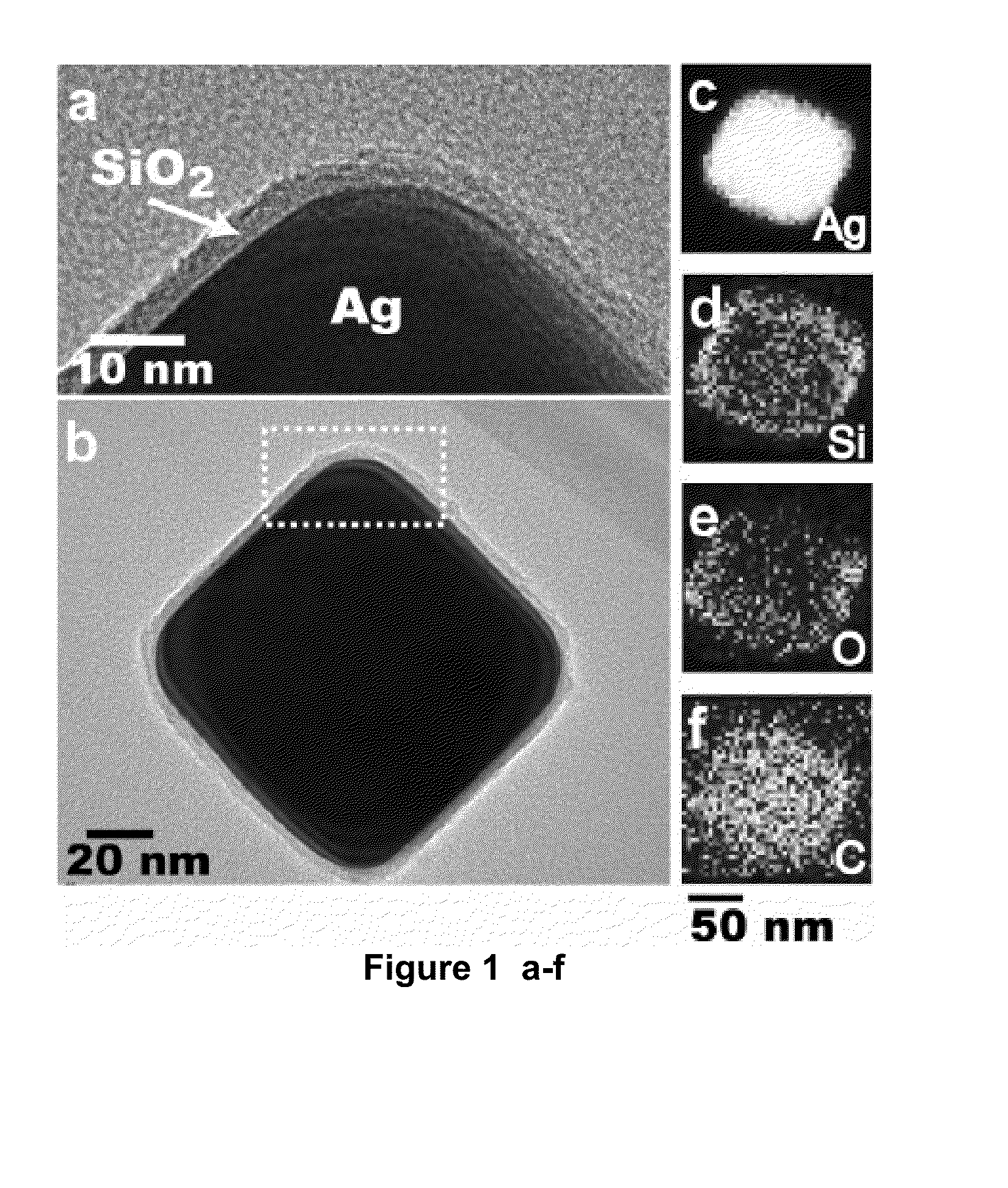

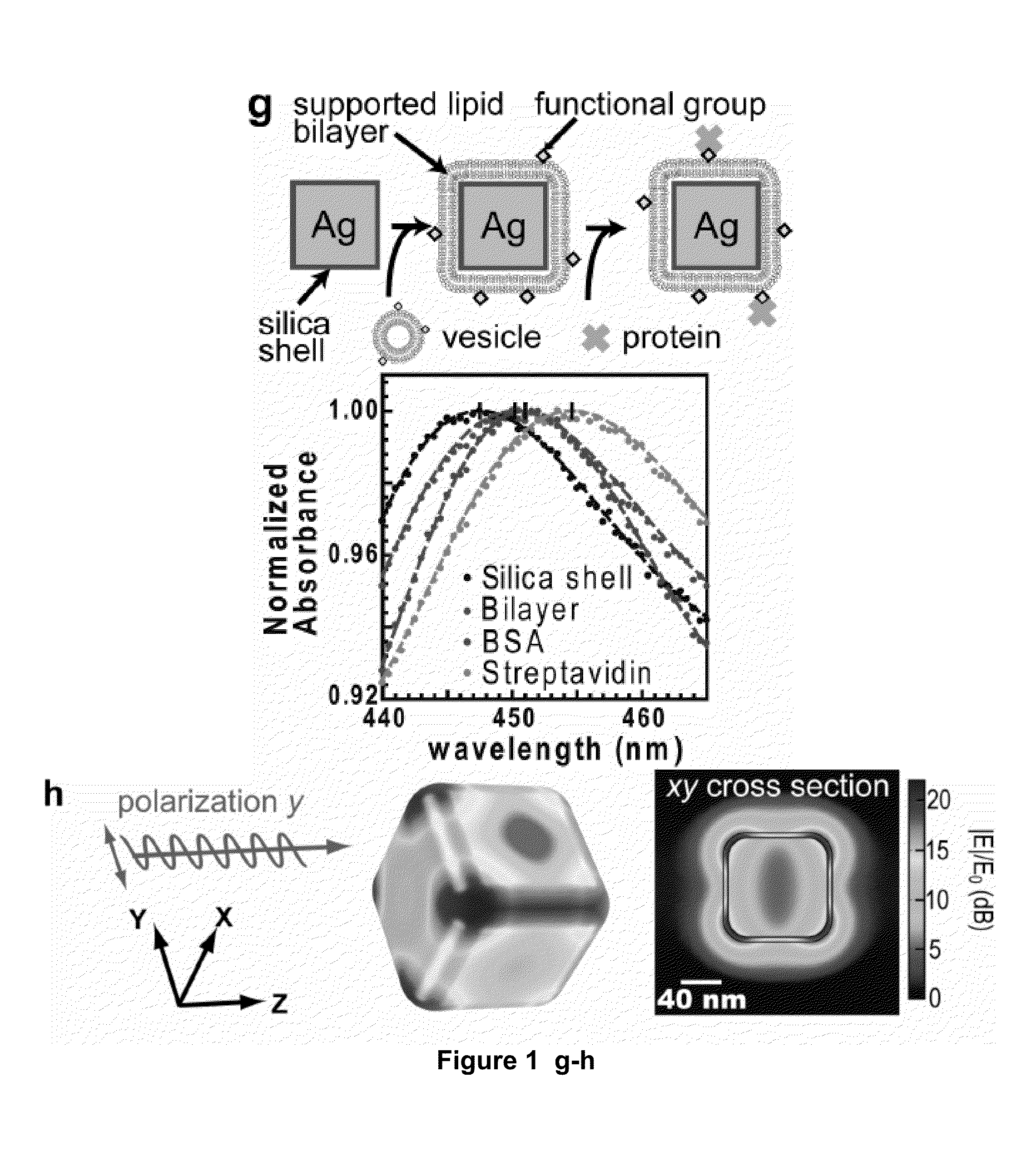

Nanoparticle Plasmonic Sensor for Localized Surface Plasmon Resonance

The present invention provides a sensor for detecting the binding of molecules to membrane surfaces. The sensor comprises a nanoparticle coated with a continuous layer of silica, and having a ligand attached thereto, for detection of an analyte in a solution. The nanoparticle can be further coated with a continuous membrane, such as a lipid bilayer.

Owner:RGT UNIV OF CALIFORNIA

Practical secrecy-preserving, verifiably correct and trustworthy auctions

InactiveUS8024274B2Preserve secrecyAccurately determineMultiple keys/algorithms usageComputer security arrangementsCorrectness proofsTheoretical computer science

A system and method for conducting verifiably correct auctions that preserves the secrecy of the bids while providing for verifiable correctness and trustworthiness of the auction is disclosed. Some of the elements of the method and apparatus are that the auction operator accepts all bids submitted and follows the published rules of the auction. In one embodiment, the bids are maintained secret from the auctioneer and all bidders until the auction closes and no bidder is able to change or repudiate her bid. In another embodiment, the auction operator computes the auction results and publishes proofs of the results' correctness. In yet another embodiment, any party can check these proofs of correctness via publicly verifiable computations on encrypted bids.

Owner:PRESIDENT & FELLOWS OF HARVARD COLLEGE

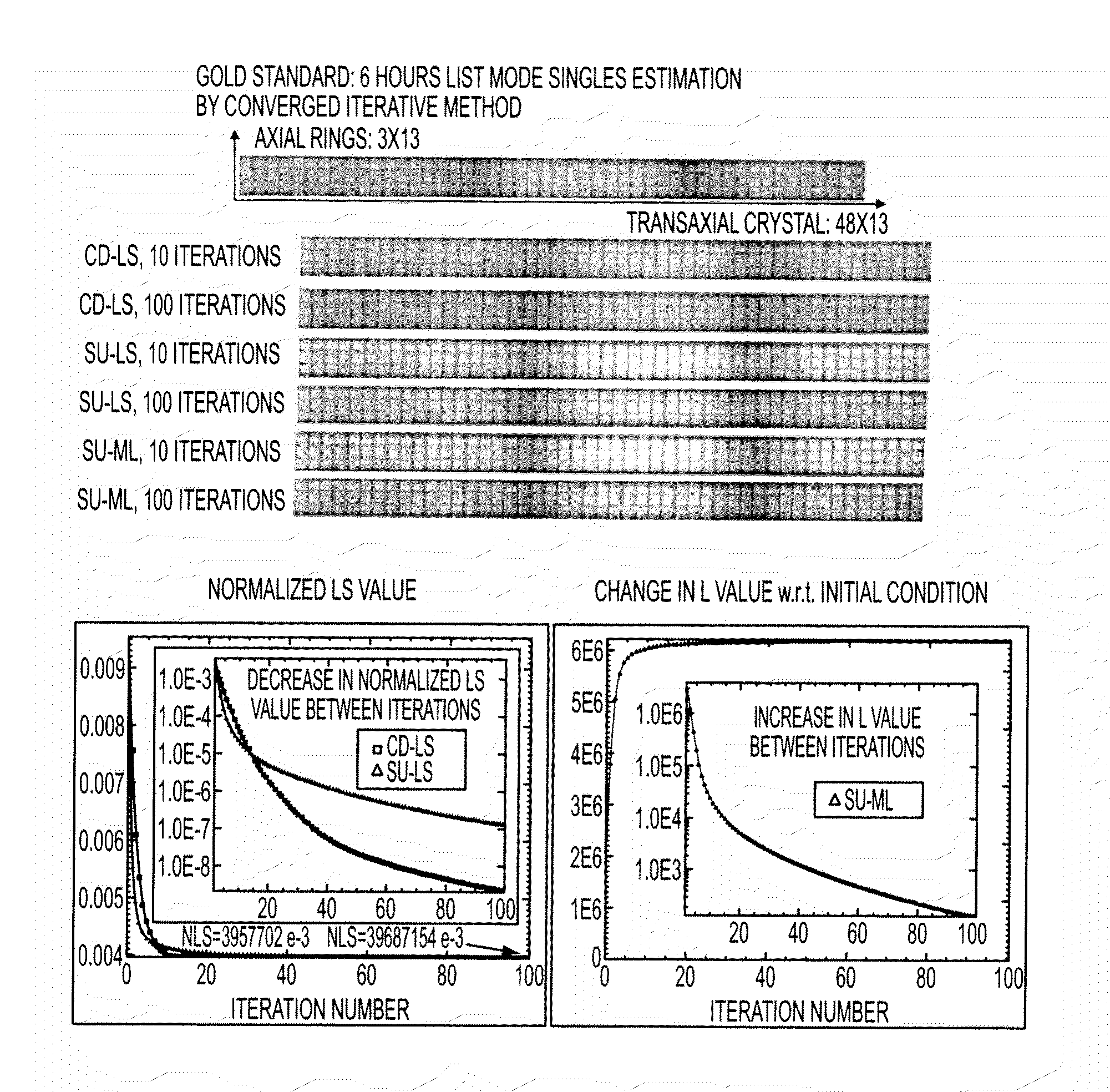

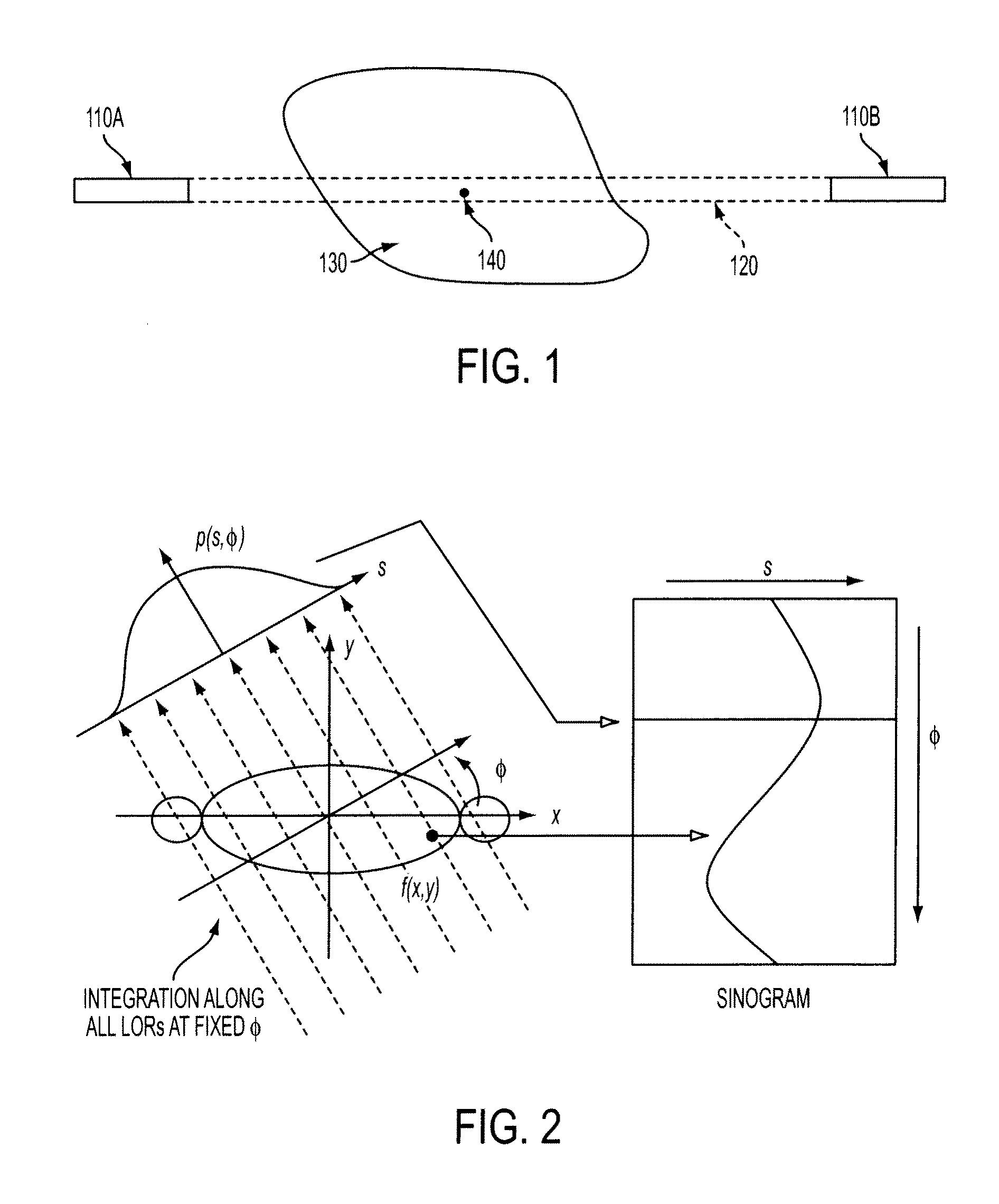

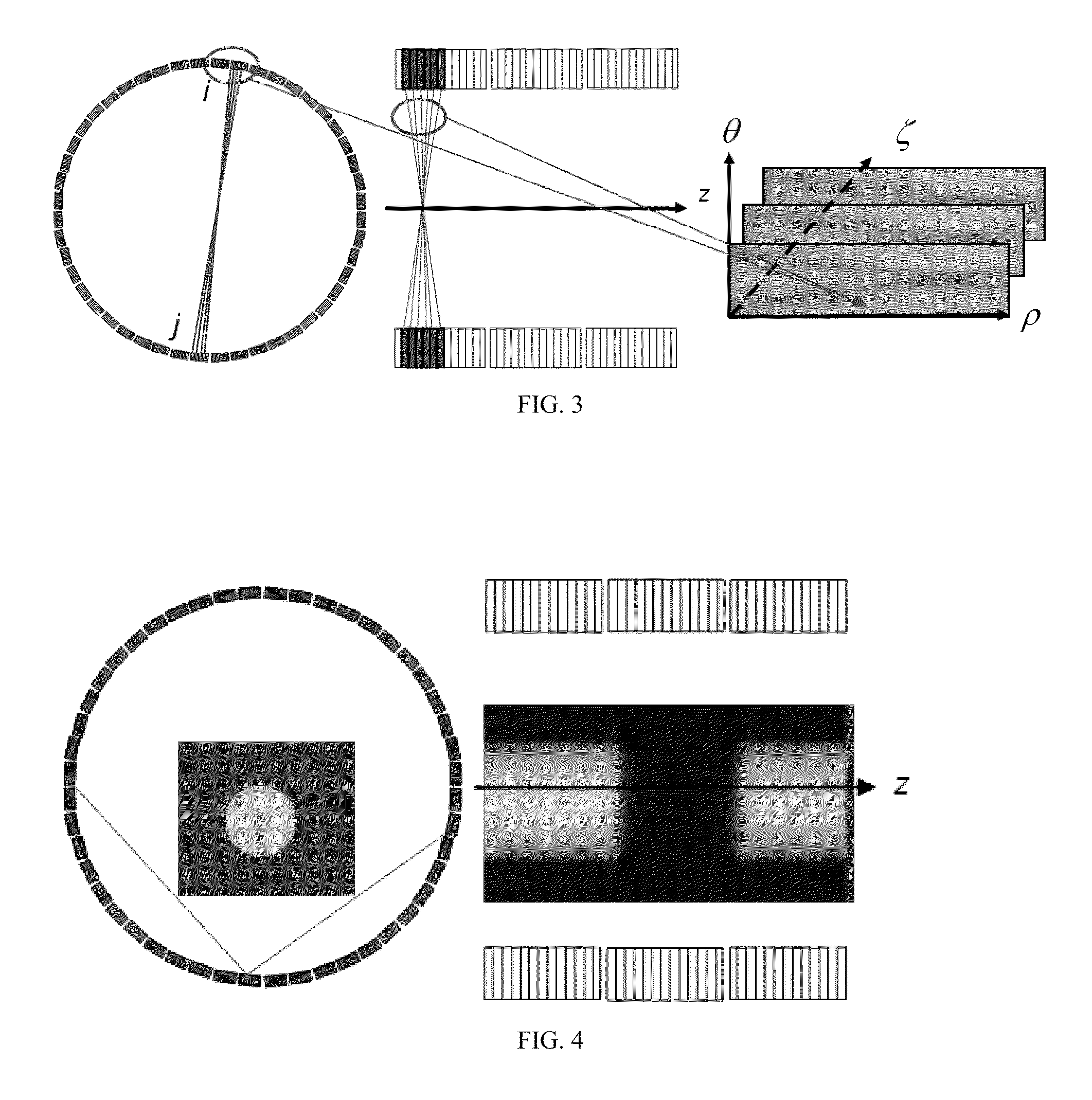

Iterative Algorithms for Variance Reduction on Compressed Sinogram Random Coincidences in PET

ActiveUS20100057819A1Easily adaptEasy parallelizationDigital computer detailsX/gamma/cosmic radiation measurmentLeast squaresVariance function

The use of the ordinary Poisson iterative reconstruction algorithm in PET requires the estimation of expected random coincidences. In a clinical environment, random coincidences are often acquired with a delayed coincidence technique, and expected randoms are estimated through variance reduction (VR) of measured delayed coincidences. In this paper we present iterative VR algorithms for random compressed sinograms, when previously known methods are not applicable. Iterative methods have the advantage of easy adaptation to any acquisition geometry and of allowing the estimation of singles rates at the crystal level when the number of crystals is relatively small. Two types of sinogram compression are considered: axial (span) rebinning and transaxial mashing. A monotonic sequential coordinate descent algorithm, which optimizes the Least Squares objective function, is investigated. A simultaneous update algorithm, which possesses the advantage of easy parallelization, is also derived for both cases of the Least Squares and Poisson Likelihood objective function.

Owner:SIEMENS MEDICAL SOLUTIONS USA INC

Hardware definition language generation for frame-based processing

ActiveUS20080066046A1Increased latencyMinimized in sizeCAD circuit designSoftware simulation/interpretation/emulationProgramming languageGraphics

An automatic code generation application is used to automatically generate code and build programs from a textual model or graphical model for implementation on the computational platform based on the design. One or more model elements may be capable of frame-based data processing. Various options and optimizations are used to generate Hardware Description Language (HDL) code for the frame-based model elements.

Owner:THE MATHWORKS INC

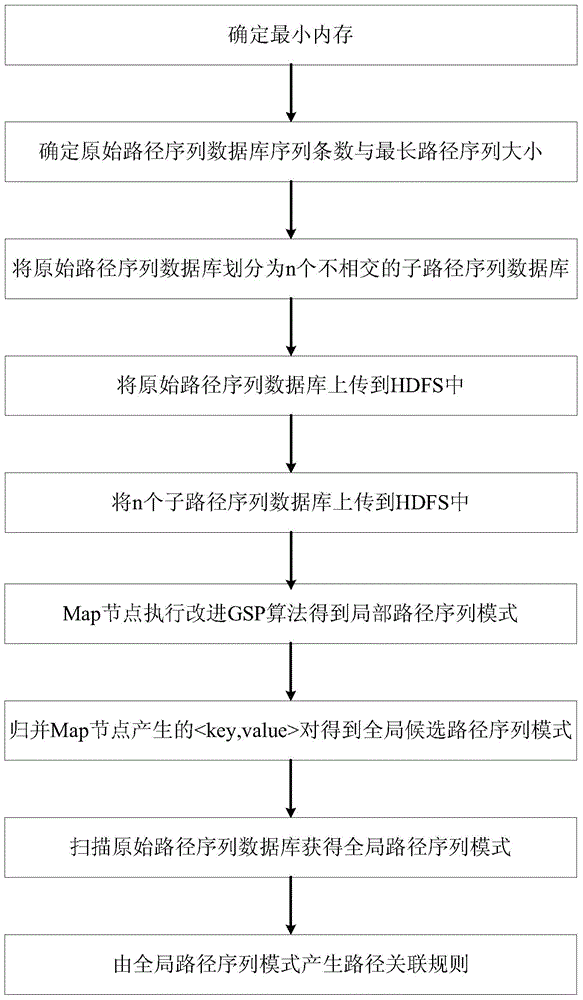

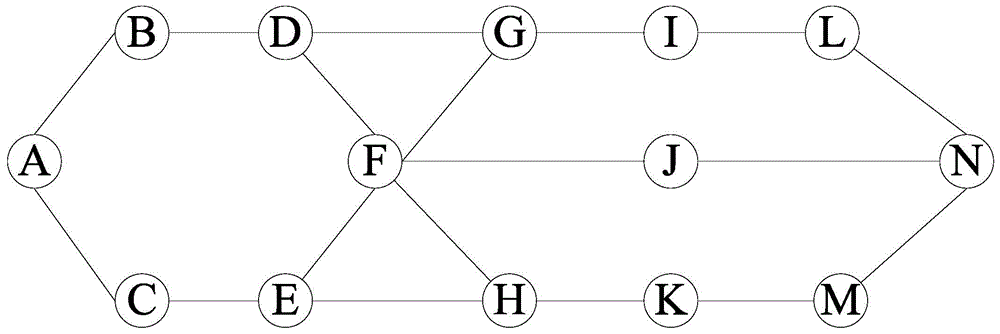

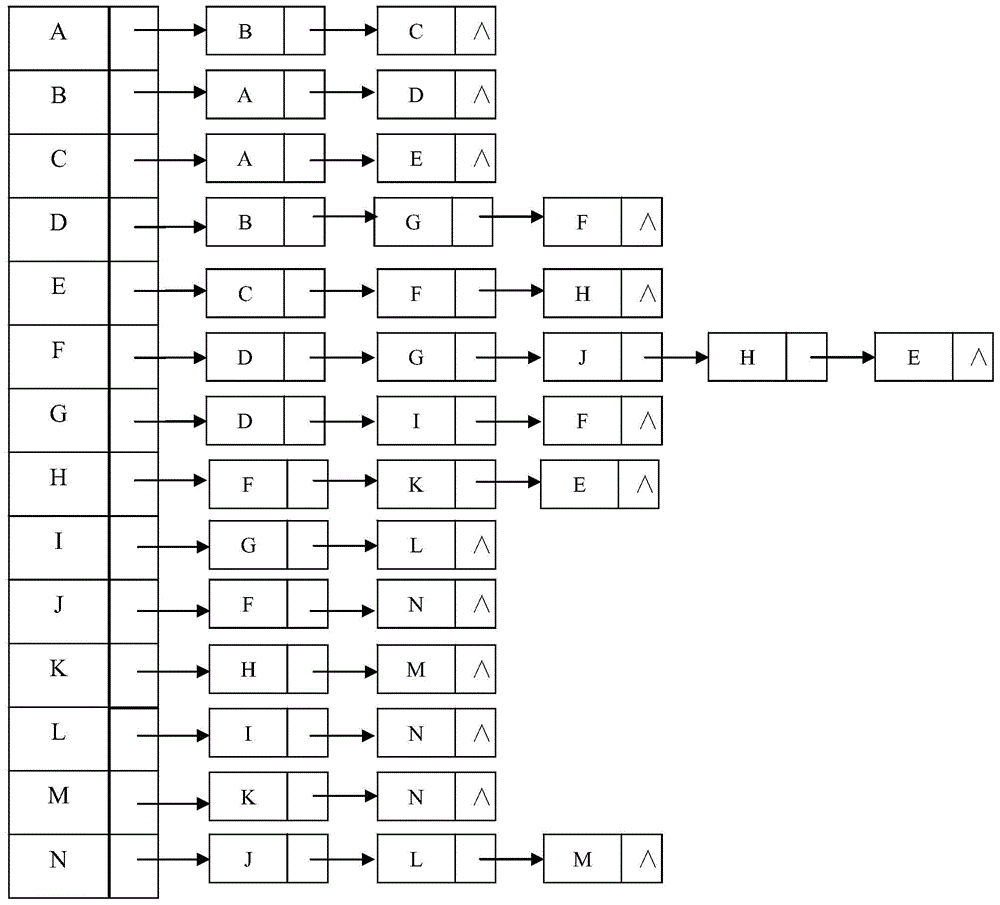

Vehicle driving path prediction method and system

InactiveCN104464344AReduce overheadEasy to parallelizeRoad vehicles traffic controlGeographical information databasesSequence databaseAlgorithm

The invention provides a vehicle driving path prediction method and system. The method includes the steps that a minimum internal storage is determined on the basis of a Hadoop platform, the largest length of a path is scanned, and an original path sequence database is evenly divided into n disjoint sub-path sequence databases; the original path sequence database and the n sub-path sequence databases are respectively uploaded to an HDFS; the n sub-path sequence databases are dispatched to different Map nodes by a master control node, each Map node executes an improved GSP algorithm, the sub-path sequence databases stored in a Map node internal storage are scanned according to a preset minimum supporting degree X, a local path sequence mode is worked out, and Reduce nodes are merged and processed so that an overall candidate sequence mode can be obtained; the original path sequence database is scanned again so that an overall path sequence mode can be obtained; the overall path sequence mode generates a path association rule and the confidence degree of the path association rule is calculated so that a vehicle driving path prediction result can be obtained.

Owner:HUBEI UNIV

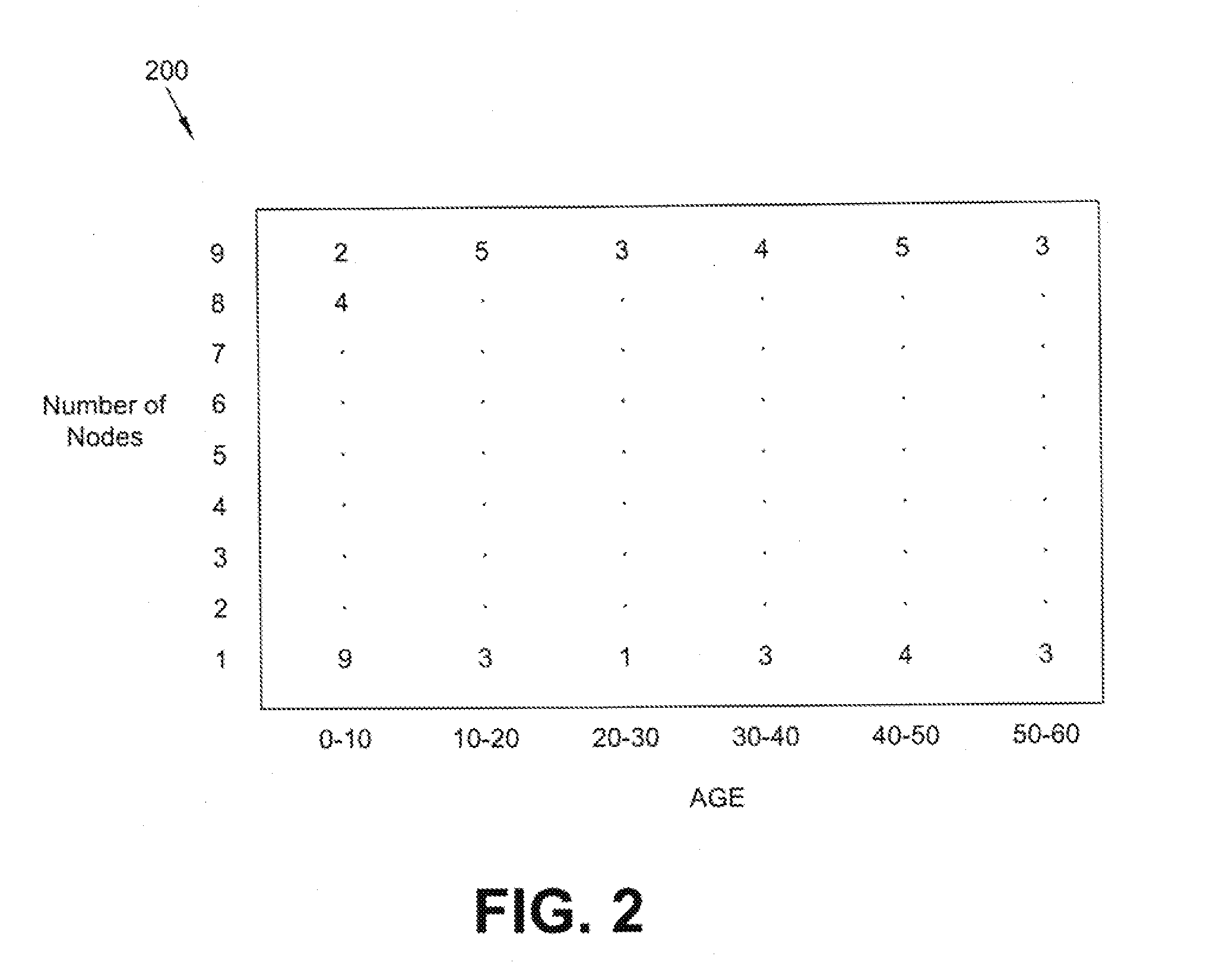

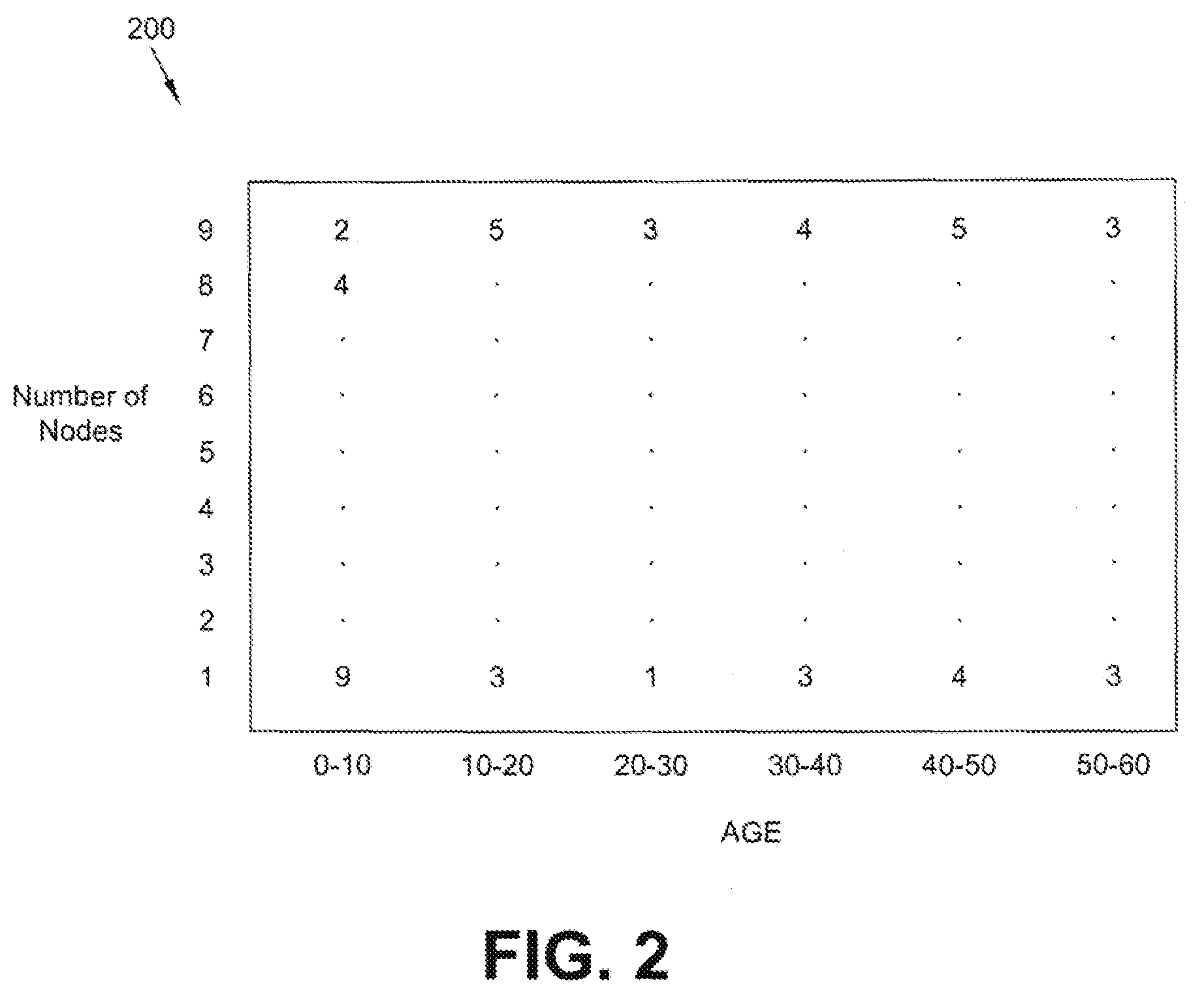

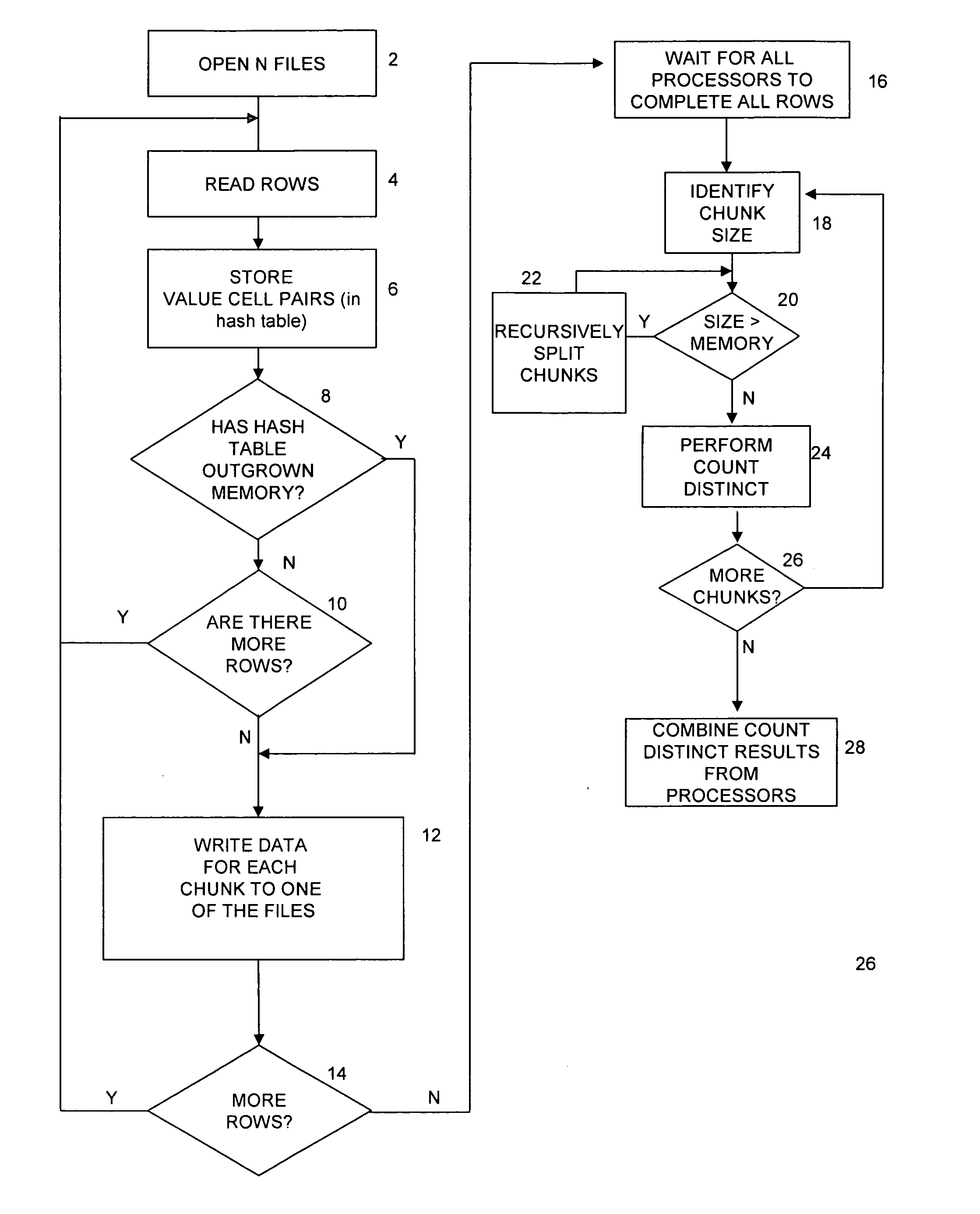

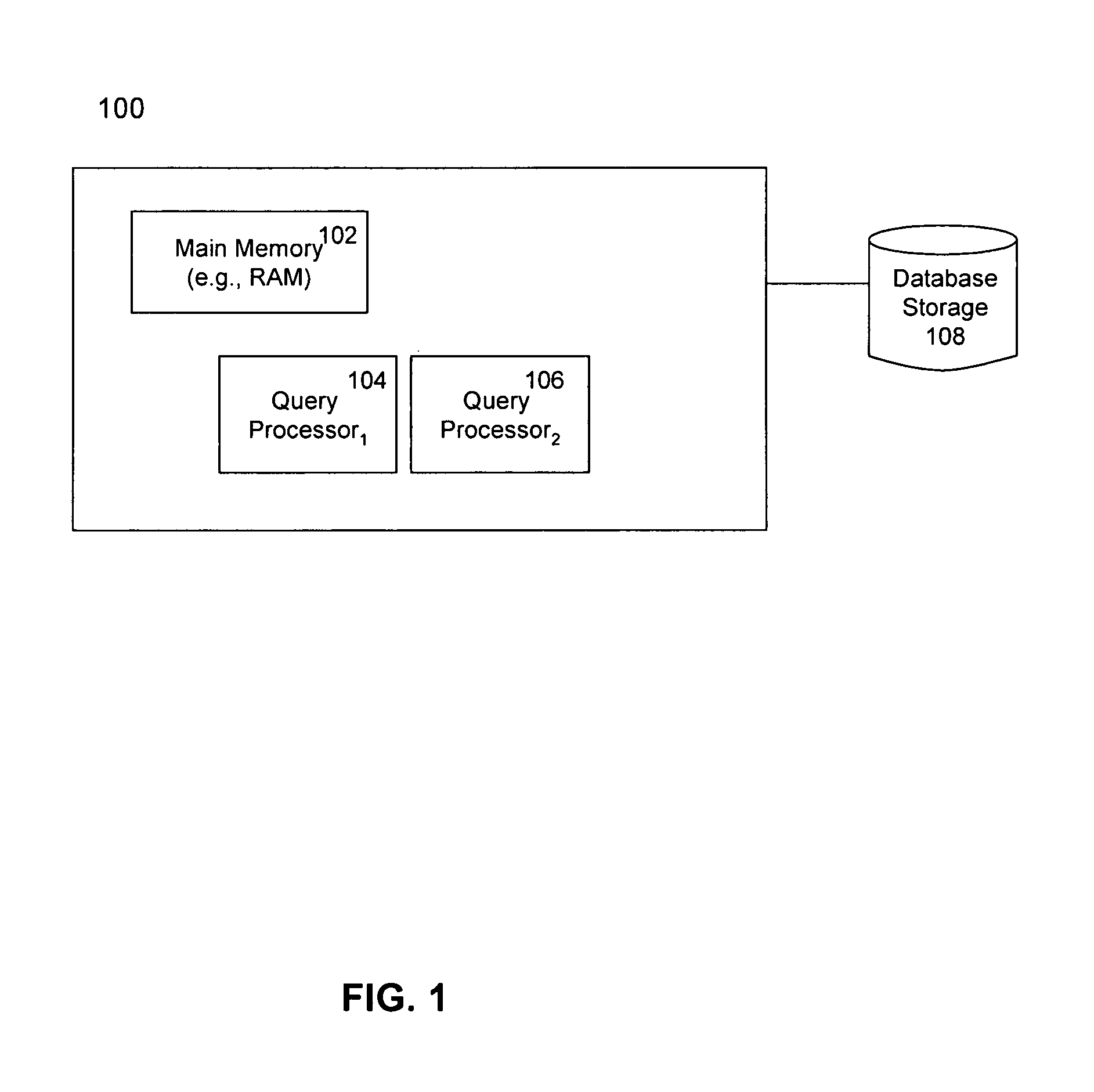

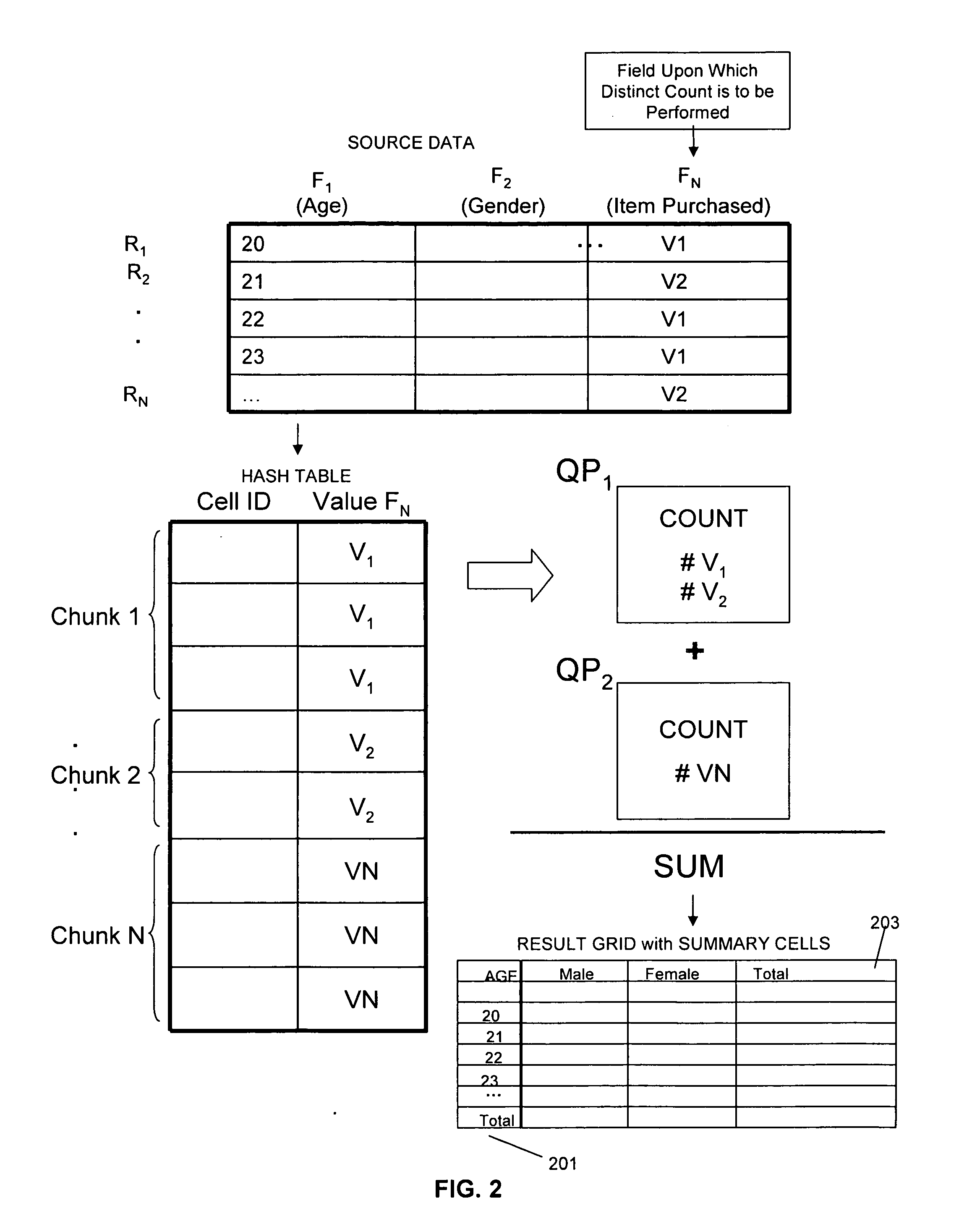

Parallel processing of count distinct values

InactiveUS20070239663A1Easy to parallelizeComputationally efficientDigital data information retrievalSpecial data processing applicationsTheoretical computer scienceTerm memory

A system and method for efficiently determining the number of distinct values in a column of source data is disclosed. Source data (e.g., source table) may be in the form of rows and columns that represent information. From the source table a count distinct function may be carried out to determine the number of distinct values in one or more columns of the source table. Results from an in memory count distinct function performed by a plurality of parallel query processors may be placed into a results grid. Another aspect of the invention relates to determining how many distinct values fall into each cell of the results grid.

Owner:CLAREOS

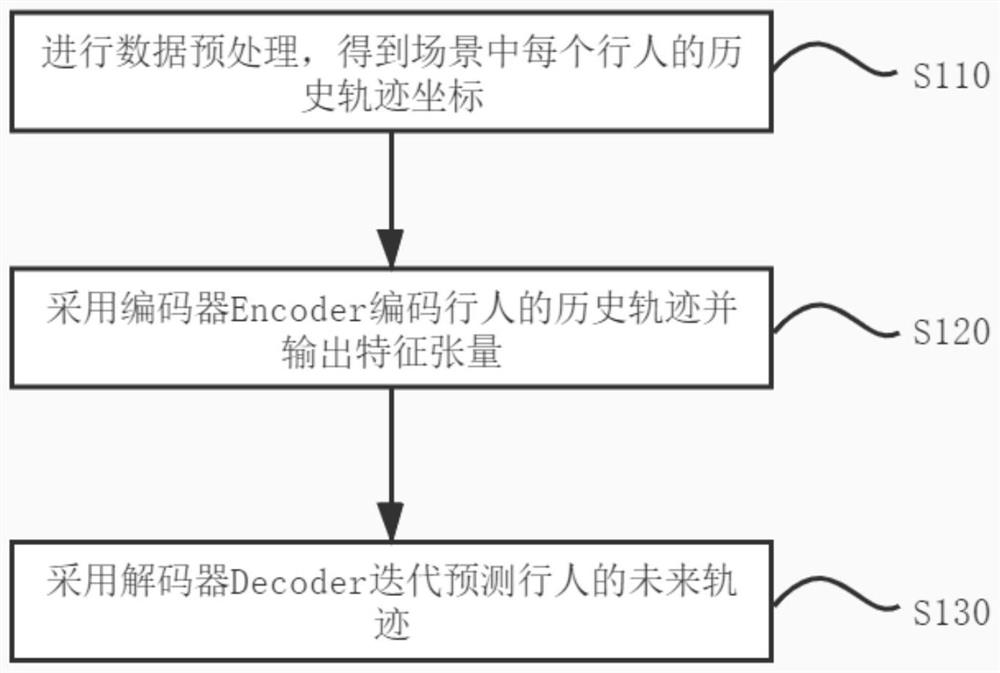

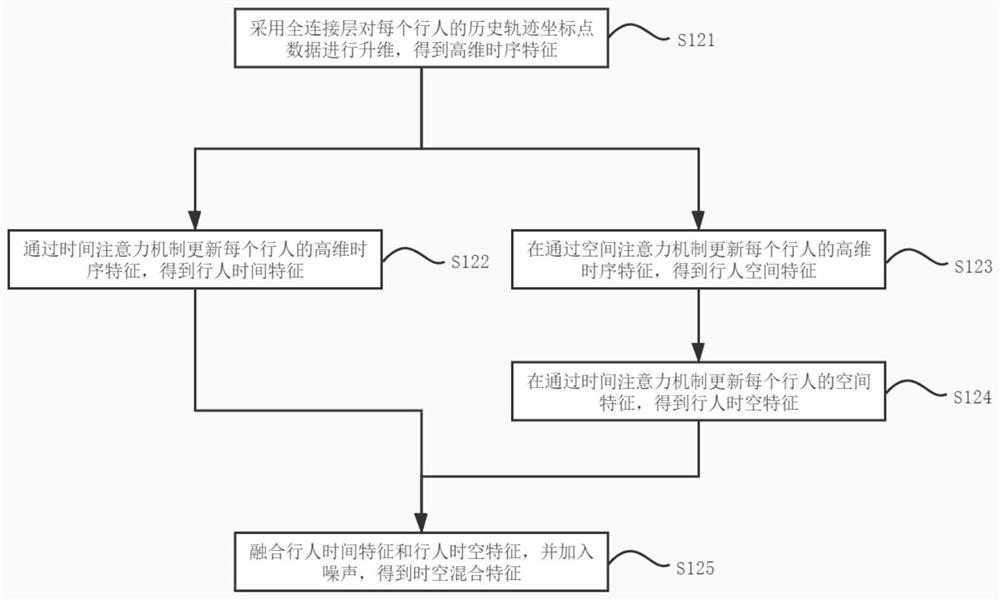

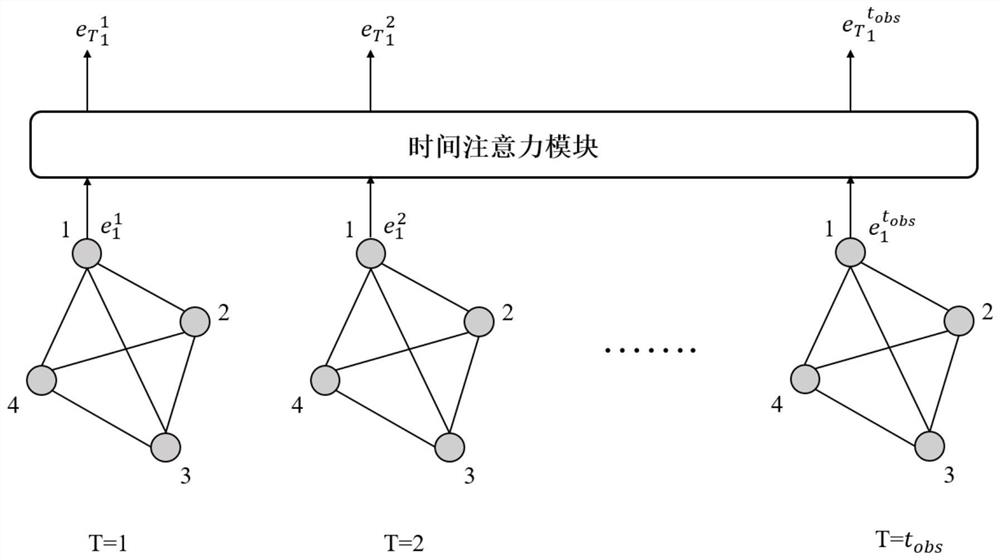

Pedestrian trajectory prediction method based on space-time attention mechanism

ActiveCN113256681AFully excavate the characteristics of historical trajectoryGuaranteed PredictabilityImage enhancementImage analysisComputer graphics (images)In vehicle

A pedestrian trajectory prediction method based on the space-time attention mechanism comprises the following steps: acquiring image information in a scene, and extracting position information of a pedestrian in an image coordinate system; performing data preprocessing to obtain historical track coordinates of each pedestrian in the scene; by adopting an encoder Encoder, encoding the historical trajectory of the pedestrian, and outputting a feature tensor; and by adopting a decoder, iteratively predicting future trajectory coordinates of the pedestrian, wherein the encoder integrates the historical track information of each pedestrian and the interaction information among different pedestrians in the same scene through an attention mechanism. Real-time effective prediction of the pedestrian trajectory in an automatic driving practical application scene is realized, the method adapts to the processing capability of a vehicle-mounted low-power-consumption processor, the accuracy of pedestrian trajectory prediction is improved, a reliable basis is provided for practical automatic driving decision making, and the safety of automatic driving is greatly improved.

Owner:CHANGCHUN YIHANG INTELLIGENT TECH CO LTD

Practical secrecy-preserving, verifiably correct and trustworthy auctions

InactiveUS20110295752A1Preserve secrecyAccurately determineMultiple keys/algorithms usagePayment architectureCorrectness proofsTheoretical computer science

A system and method for conducting verifiably correct auctions that preserves the secrecy of the bids while providing for verifiable correctness and trustworthiness of the auction is disclosed. Some of the elements of the method and apparatus are that the auction operator accepts all bids submitted and follows the published rules of the auction. In one embodiment, the bids are maintained secret from the auctioneer and all bidders until the auction closes and no bidder is able to change or repudiate her bid. In another embodiment, the auction operator computes the auction results and publishes proofs of the results' correctness. In yet another embodiment, any party can check these proofs of correctness via publicly verifiable to computations on encrypted bids.

Owner:PRESIDENT & FELLOWS OF HARVARD COLLEGE

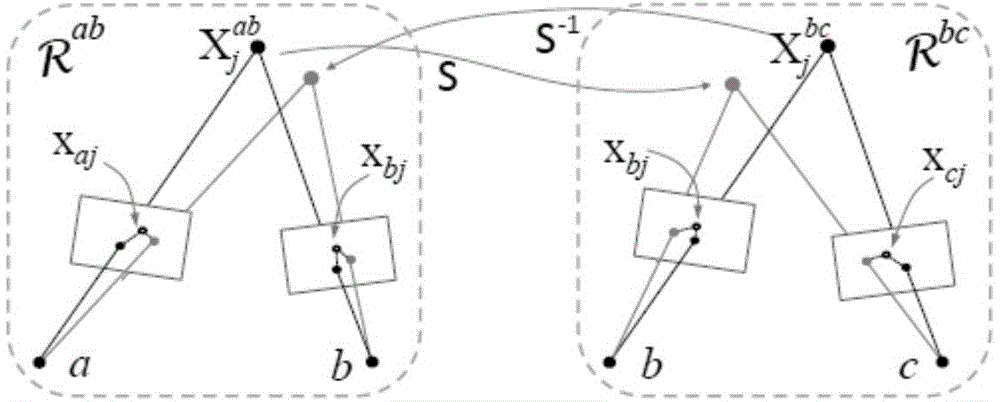

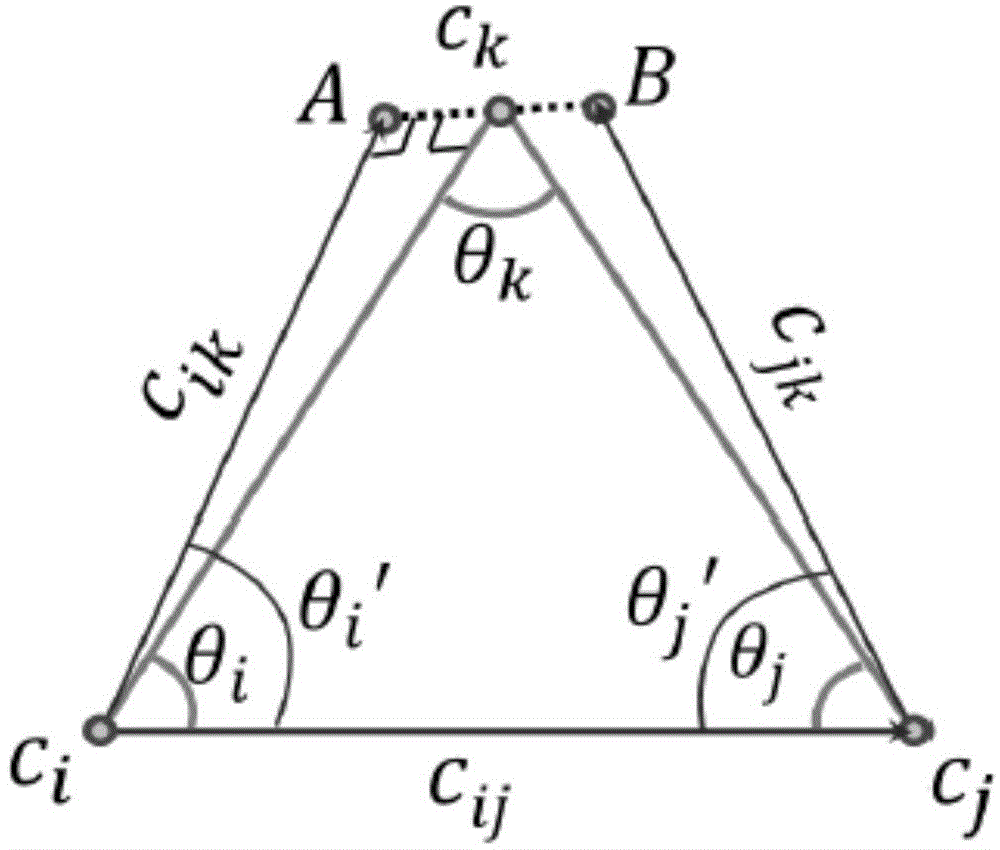

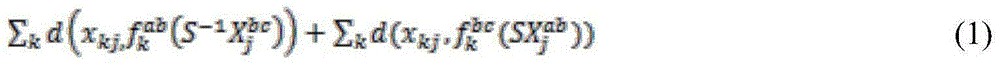

Three-dimensional model reestablishment method based on global linear method

The invention discloses a three-dimensional model reestablishment method based on a global linear method. According to the method, firstly, the orientation array of all cameras is obtained by solving the relative rotating relations between every two cameras; secondly, stable camera triad reestablishment is obtained through the nonlinear optimization technology, and a linear relation in a triad is solved; thirdly, a system of linear equations is formed according to equations provided by the triad, accurate camera postures can be obtained by solution through a numerical method, and finally, final optimization is carried out on reestablishment results through the technology of concentration of beam adjustment. The three-dimensional model reestablishment method based on the global linear method is fast, robust and accurate through experimental verification.

Owner:PEKING UNIV

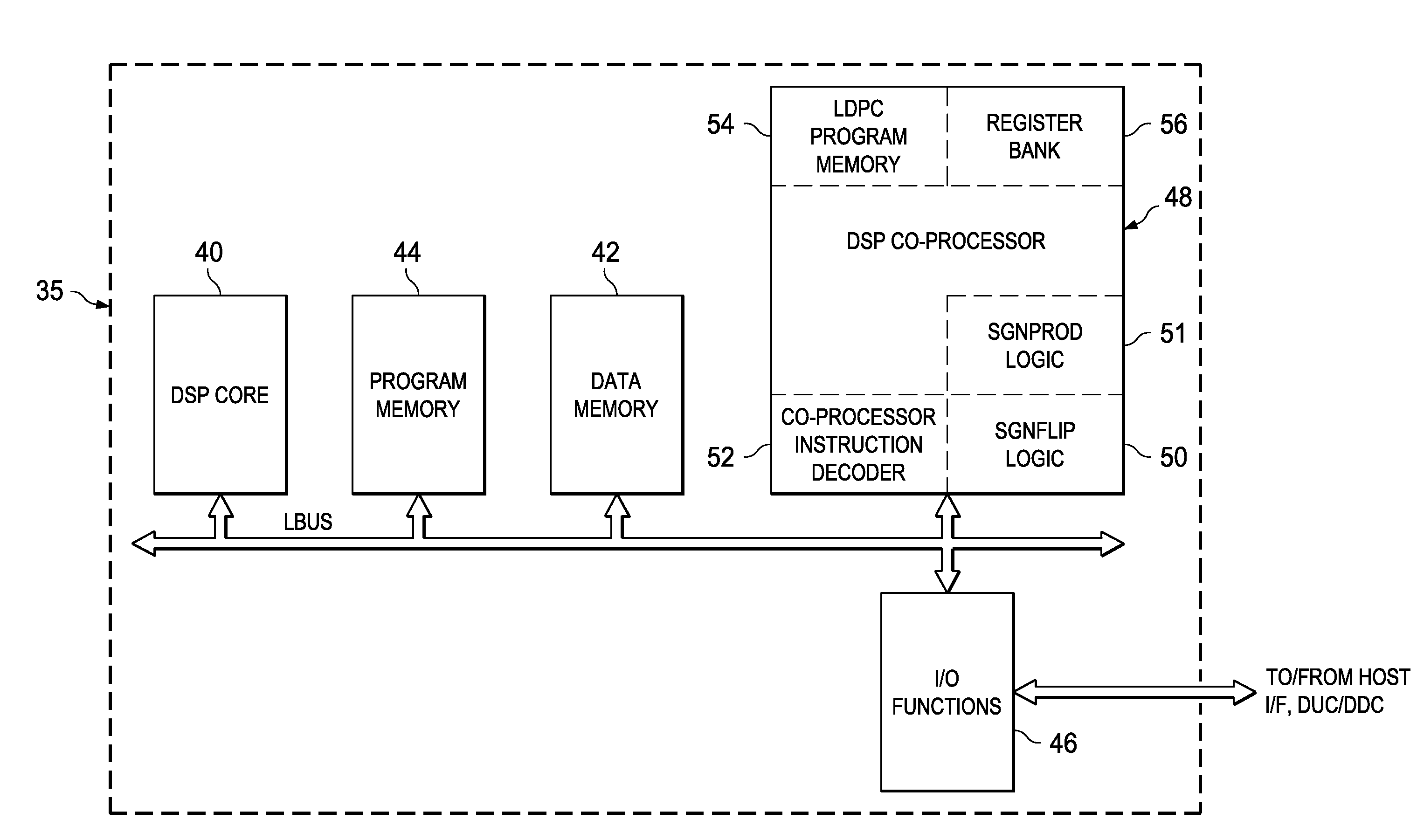

Sign Operation Instructions and Circuitry

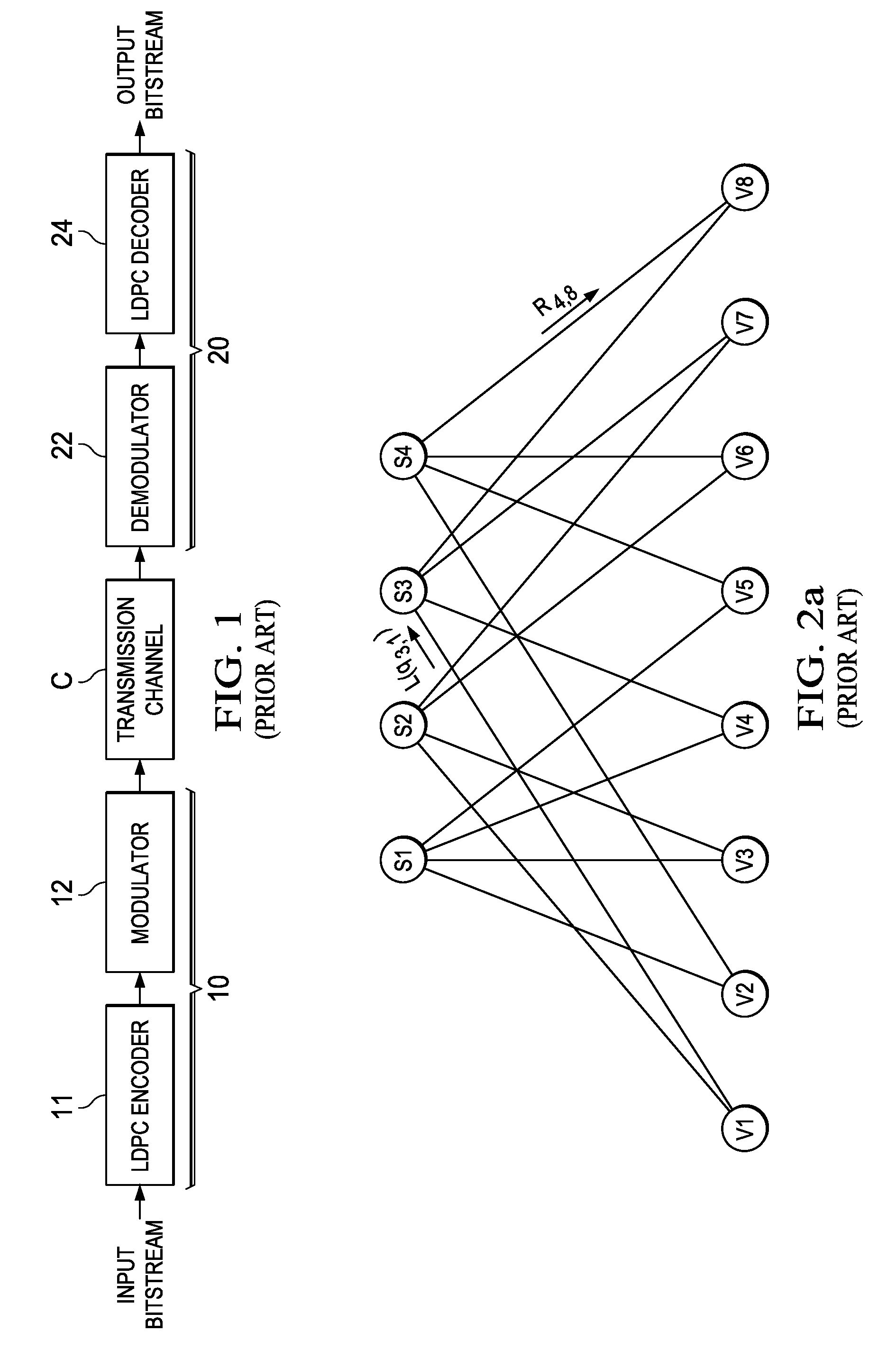

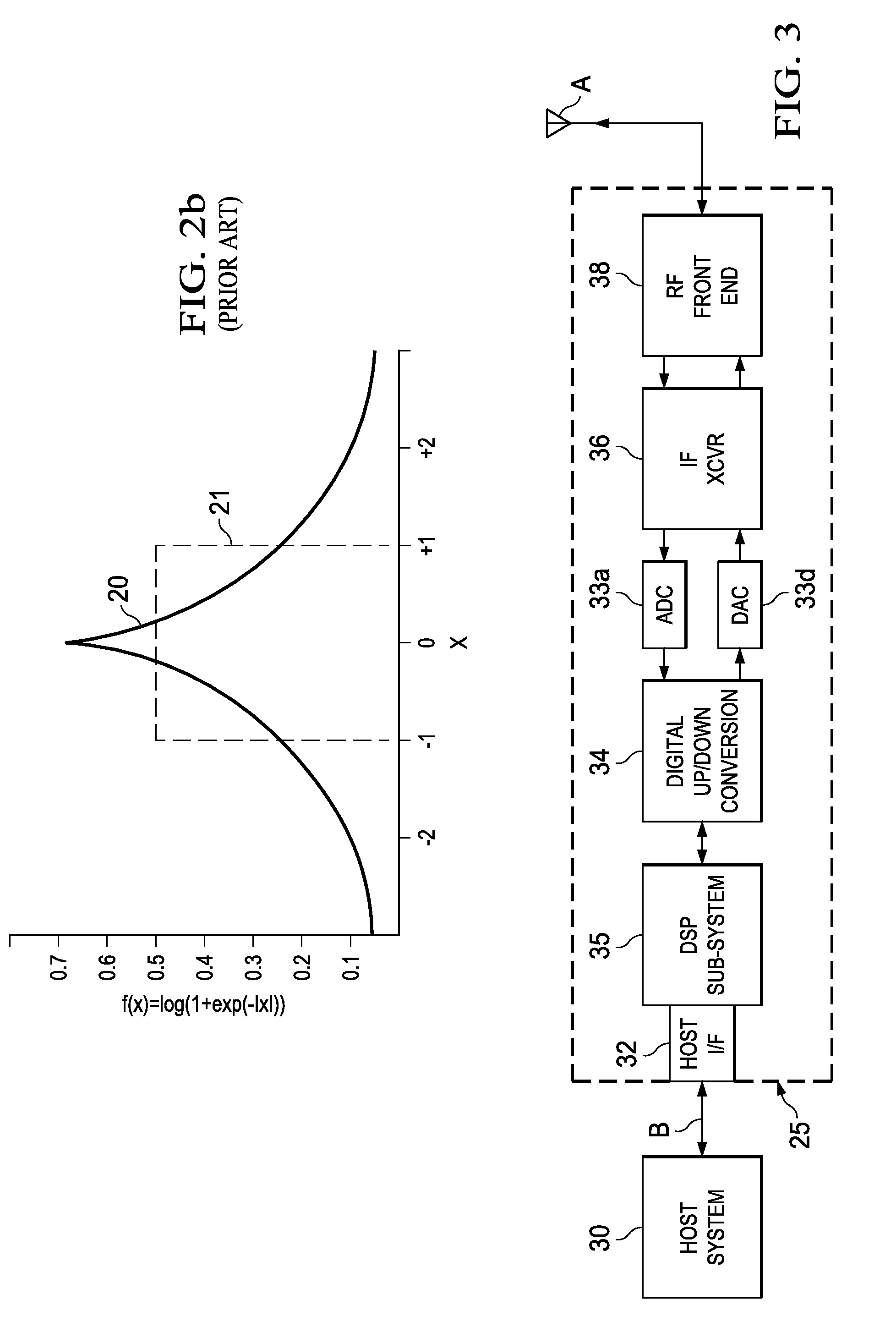

InactiveUS20090113174A1Improve efficiencyReduce in quantityProgram control using wired connectionsCode conversionOperating instructionSign bit

A co-processor for efficiently decoding codewords encoded according to a Low Density Parity Check (LDPC) code, and arranged to efficiently execute an instruction to multiply the value of one operand with the sign of another operand, is disclosed. Logic circuitry is included in the co-processor to select between the value of a second operand, and an arithmetic inverse of the second operand value, in response to the sign bit of the first operand. This logic circuitry is arranged to operate according to 2's-complement integer arithmetic, by also including invert-and-increment circuitry to produce a 2's-complement inverse of the second operand. A comparator determines whether the second operand is at a maximum 2's-complement negative value, in which case the arithmetic inverse is selected to be a hard-wired maximum 2's-complement positive value. Logic circuitry is also included in the co-processor to execute an instruction to multiple the signs of two operands; this logic circuitry is realized as an exclusive-OR function operating on the sign bits of the operands, and a multiplexer for selecting between digital words of the values +1 and −1 in response to the exclusive-OR function. The logic circuitry can be arranged in multiple blocks in parallel, to provide parallel execution of the instruction in wide datapath processors.

Owner:TEXAS INSTR INC

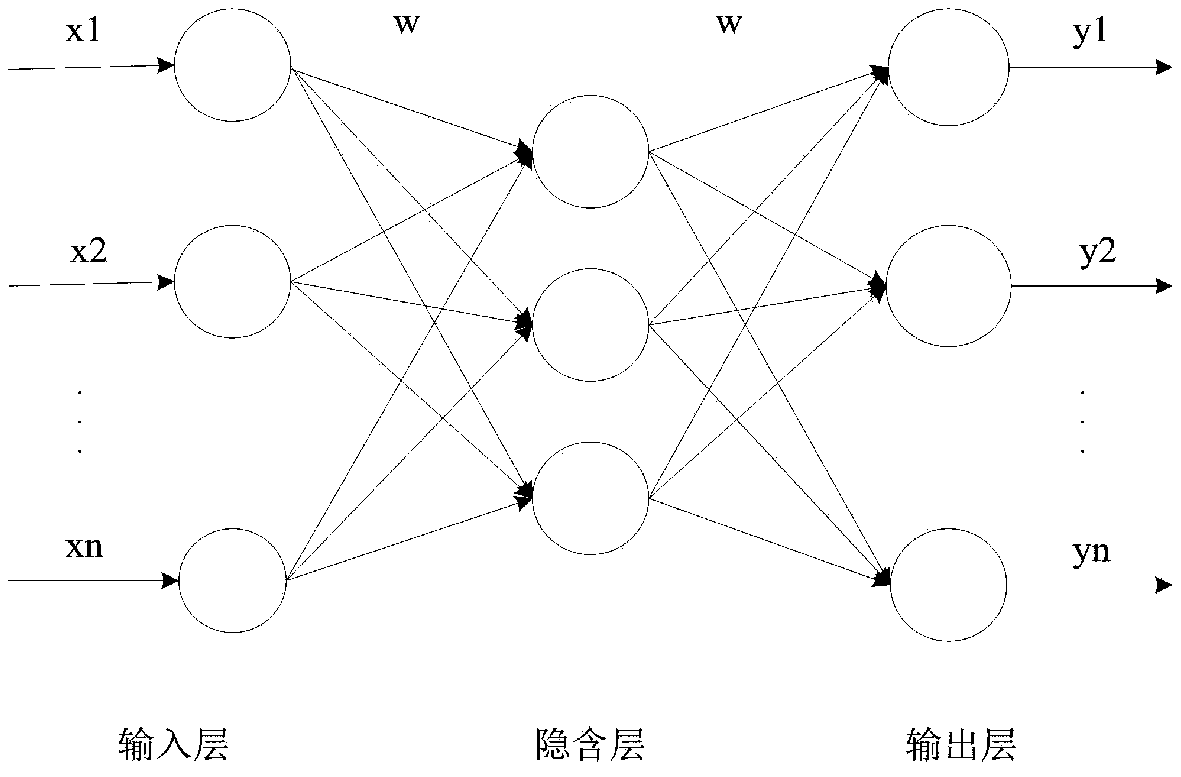

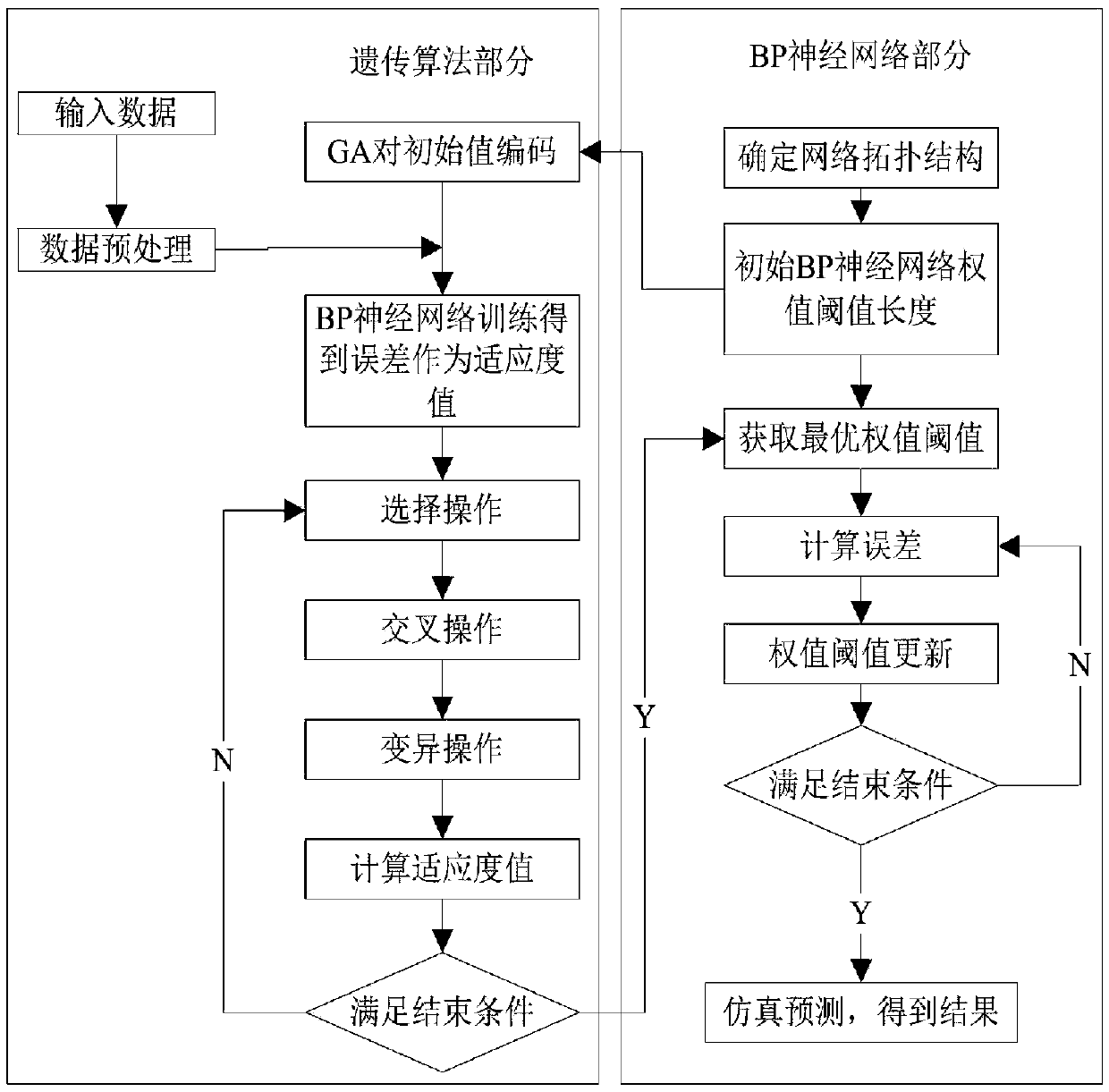

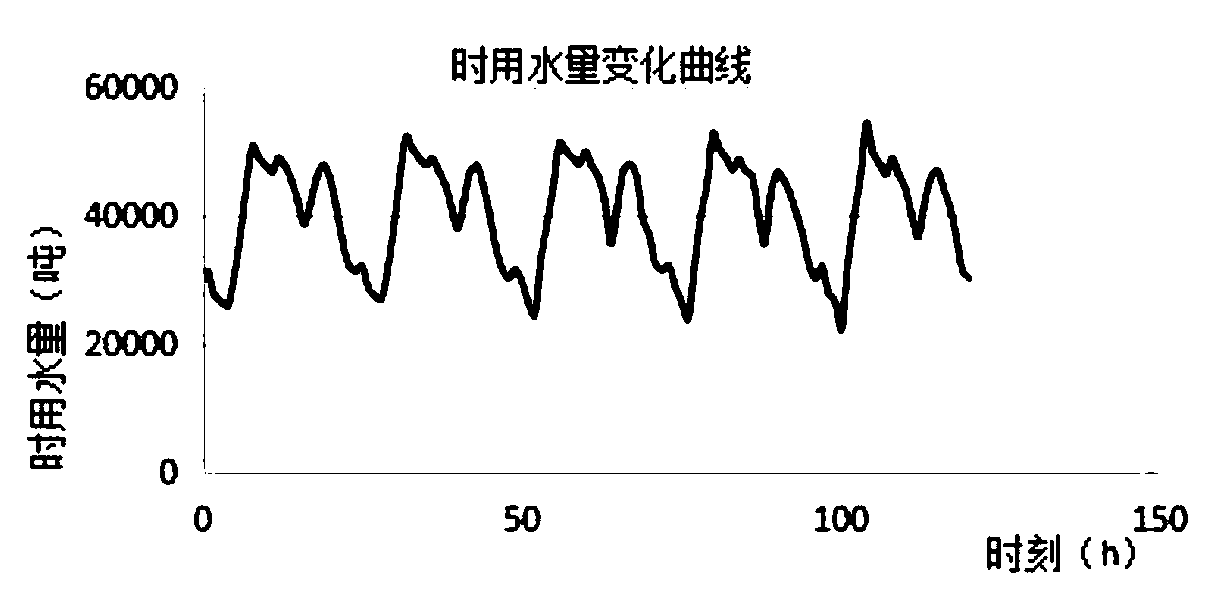

Urban water consumption prediction method based on GA-BP neural network

PendingCN110443418AOvercome the Difficulty of Initial WeightsImprove forecast accuracyForecastingNeural learning methodsPredictive methodsNetwork structure

The invention relates to the field of neural networks and urban water consumption prediction, in particular to an urban water consumption prediction method based on a GA-BP neural network. The methodcomprises the following steps: step 1, constructing a BP neural network structure; step 2, carrying out GA optimization on the initial weight of the BP neural network; step 3, training and predictinga GA-BP neural network; and step 4, applying the trained GA-BP neural network to prediction of urban water consumption. According to the GA-BP neural network-based urban water consumption prediction method, the difficulty of optimizing the initial weight of the neural network is overcome, and the prediction precision of analysis is improved.

Owner:XIAN UNIV OF SCI & TECH

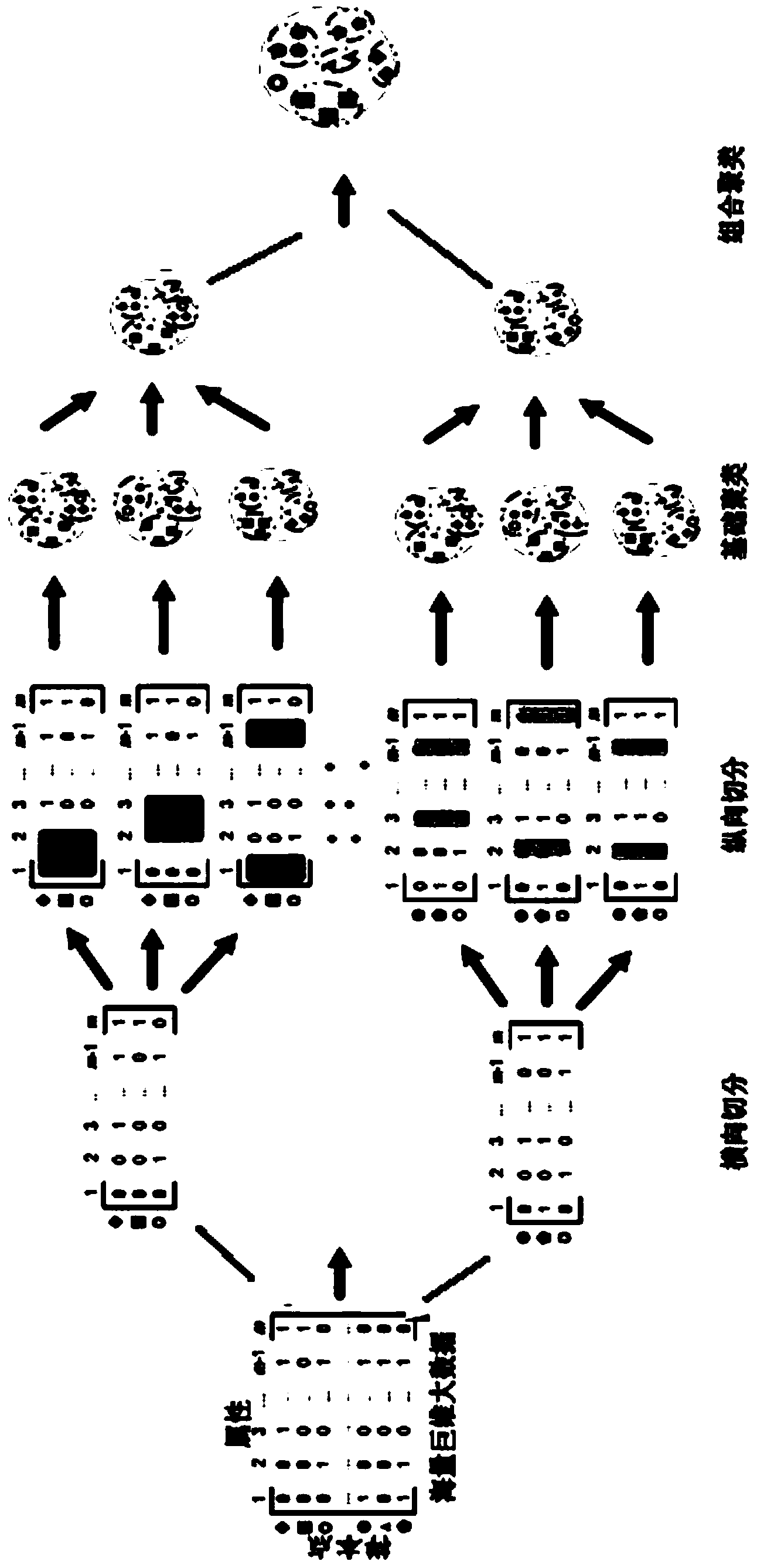

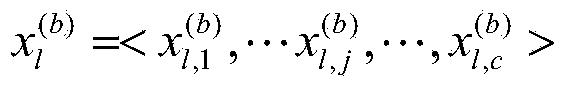

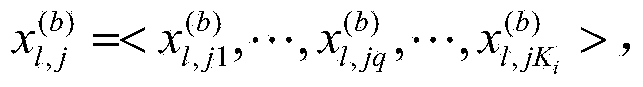

Big data clustering method based on decomposition and composition

ActiveCN104063518AOvercoming difficulties such as massive high-dimensionalEfficientRelational databasesSpecial data processing applicationsDecompositionData science

The invention discloses a big data clustering method based on decomposition and composition. The method includes the steps of transversely segmenting a data set to obtain a plurality of data subsets , transversely segmenting each transverse data subset to obtain a plurality of longitudinal data subsets, and obtaining classification tags of the data subsets obtained through transverse segmentation and longitudinal segmentation by using a basic clustering algorithm, compositing and clustering the classification tags of the longitudinal data subsets, and compositing and clustering the classification tags of the transverse data subsets again to obtain a complete classification tag of the data set. By means of the big data clustering method, the problem of big data clustering is converted into the composition clustering problem, and the big data clustering method has the advantages of having efficiency and robustness, being capable of being parallelized and the like. The big data clustering method is suitable for big data clustering and is particularly suitable for the file classification field, the customer segmentation field, the information retrieval field and other fields.

Owner:广东唯审信息科技有限公司

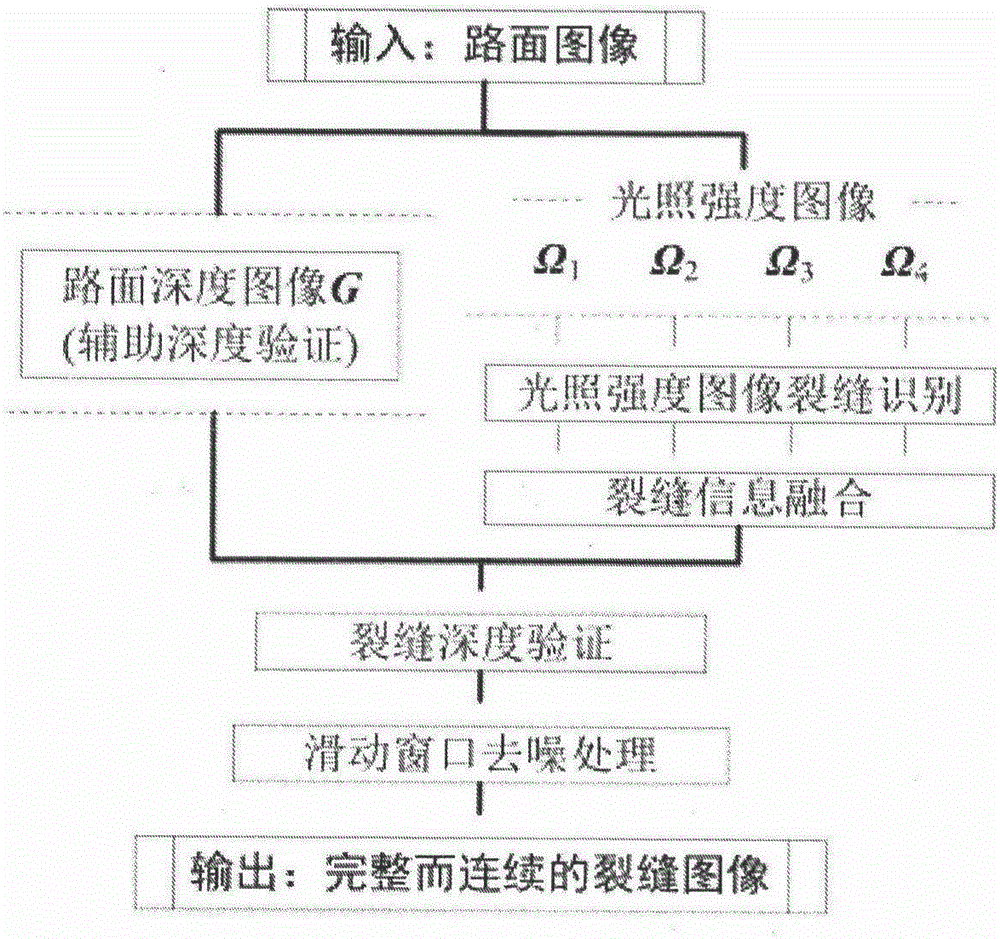

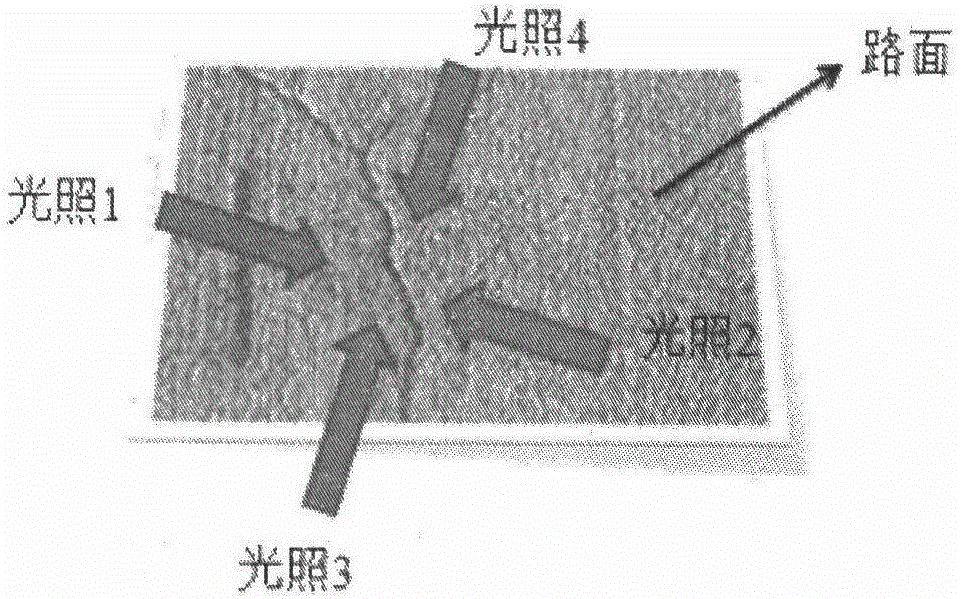

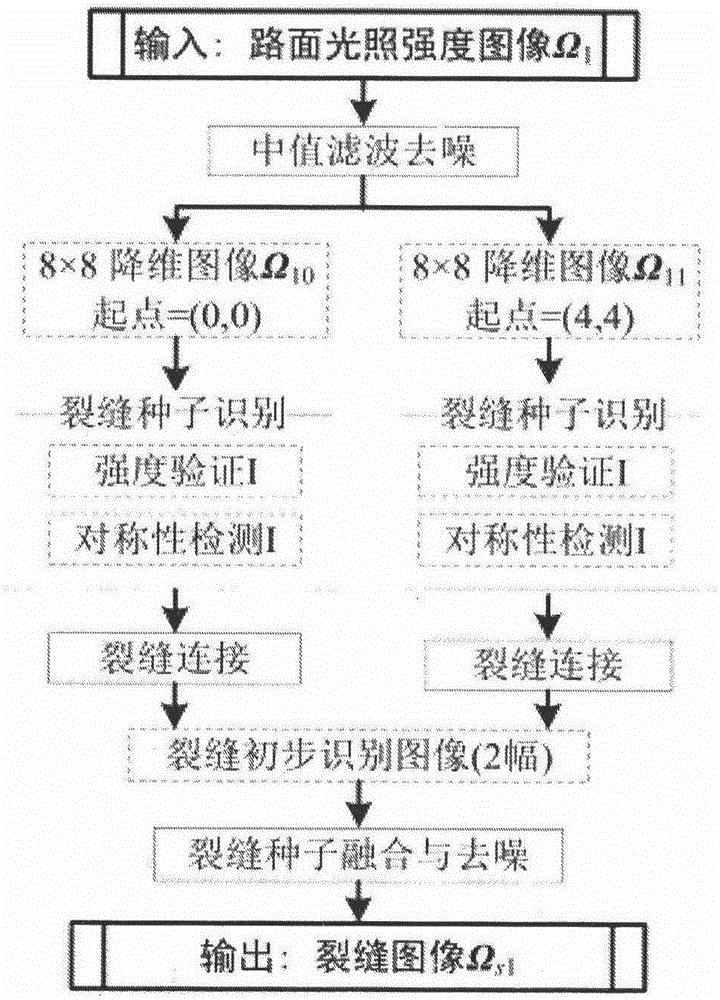

Crack automatic detection method based on three-dimensional virtual pavement

InactiveCN106023226AImprove accuracyEasy to parallelizeImage enhancementImage analysisProjection imageRoad surface

The invention discloses a crack automatic detection method based on a three-dimensional virtual pavement. The crack automatic detection method comprises the steps that (1) the three-dimensional virtual pavement is established by carrying out blanking processing and illumination model processing of a pavement depth image having a pixel of 1mm, and four projection images omega 1 to omega 4 are generated after three-dimensional projection at four angles; (2) the dimensional reduction processing, the crack identification including intensity verification and symmetry detection, and the crack connection of the four projection images omega 1 to omega 4 generated by the step (1) are sequentially carried out to acquire shadow region crack images omega s 1 to omega s 4 and reflection region crack images omega r 1 to omega r 4; (3) the crack information of the shadow region crack images omega s 1 to omega s 4 and the crack information of the reflection region crack images omega r1 to omega r 4 are effectively integrated together, and after depth verification and sliding denoising processing, a crack image is acquired. Based on a test of 255 images (4096*2048), a test result shows that an algorithm has a higher accuracy (average 80.34%) and a higher recall rate (average 83.89%), and is better than an ADA3D algorithm by an F value of 80.47%.

Owner:彭博

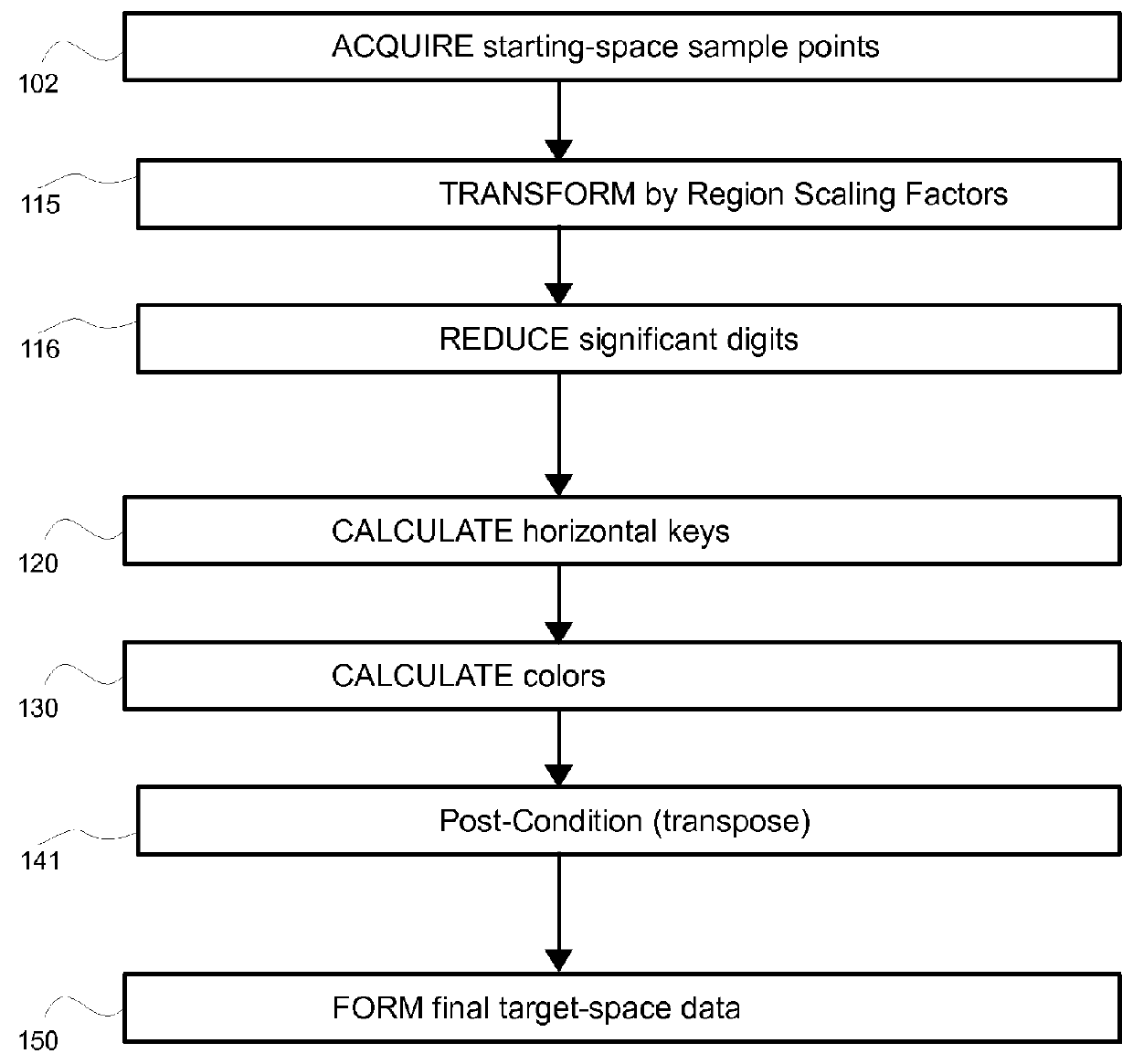

Method and system for high-resolution transforms of frequency-space and inverse frequency-space data

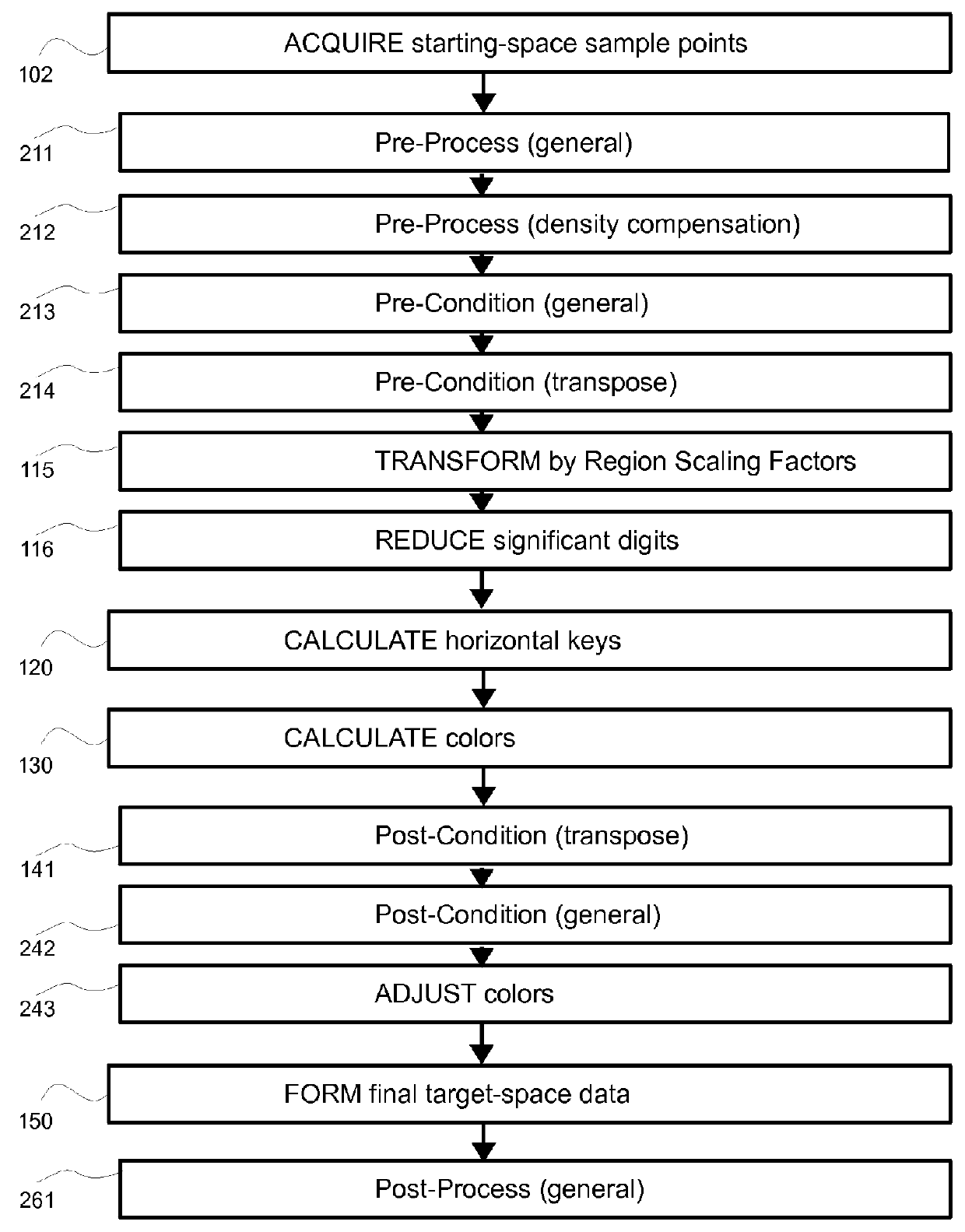

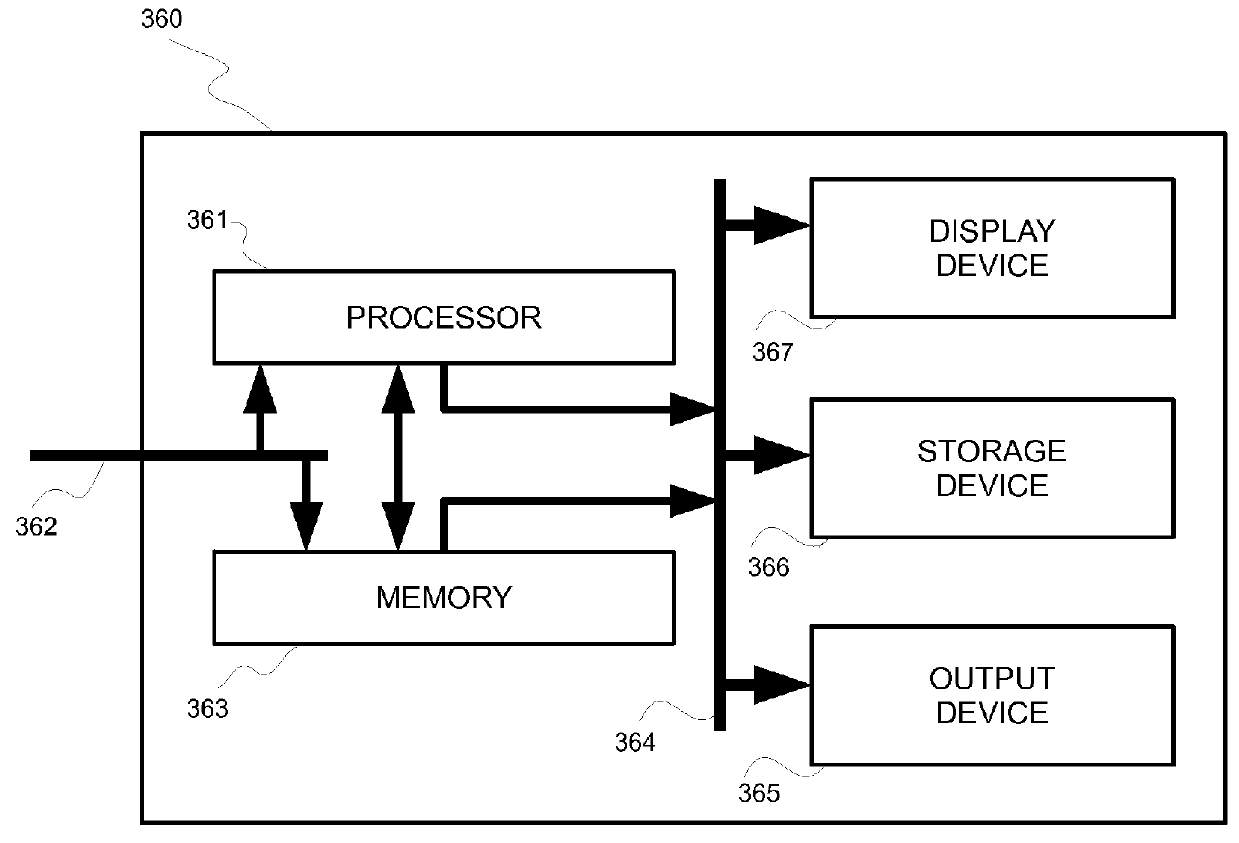

InactiveUS9251566B1Improve parallelismHigh resolutionImage enhancementReconstruction from projectionPre-conditionPre conditioning

A method and system for high-resolution and parallelizable data processing, reconstruction, and deconstruction, uses arbitrary frequency-space (FS) or inverse frequency-space (IFS, such as image, audio, or video space) sample points in N dimensions. According to a preferred embodiment of the invention, a subset of optionally pre-processed and / or pre-conditioned N-dimensional FS data (or IFS data) is acquired (102) by a processing device (360), the data is optionally transformed (115) by “region scaling factors”, and the data is optionally reduced (116) in numerical significant digits. A “horizontal key” of data elements is calculated (120) on a processor (361), preferably in parallel, for each of an arbitrary set of x-coordinates in IFS (or FS). IFS “color” data (or FS data) are calculated (130) on a processor (361), preferably in parallel, at the x-coordinates corresponding to the horizontal keys. The IFS coordinates (or the FS coordinates) are arbitrary, and the reconstruction's calculated IFS data (or the deconstruction's calculated FS data) are optionally rotated or transposed (141) (such as for display purposes), and are thus formed (150) in a memory (363) or on an output device (365). The method can be applied to other subsets, such as in the N-dimensional case.

Owner:BAJIC IVAN

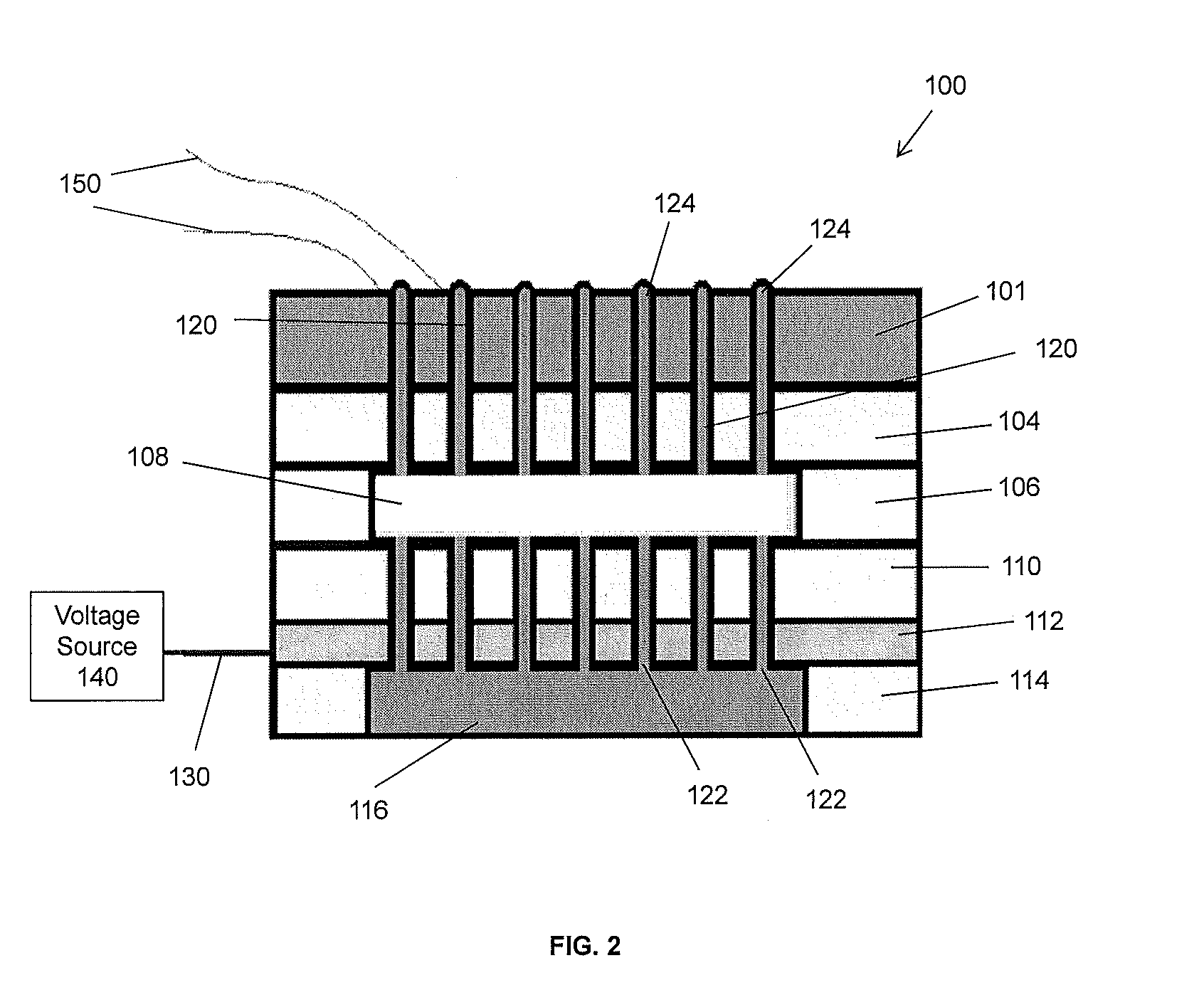

System and methods for moving objects individually and in parallel

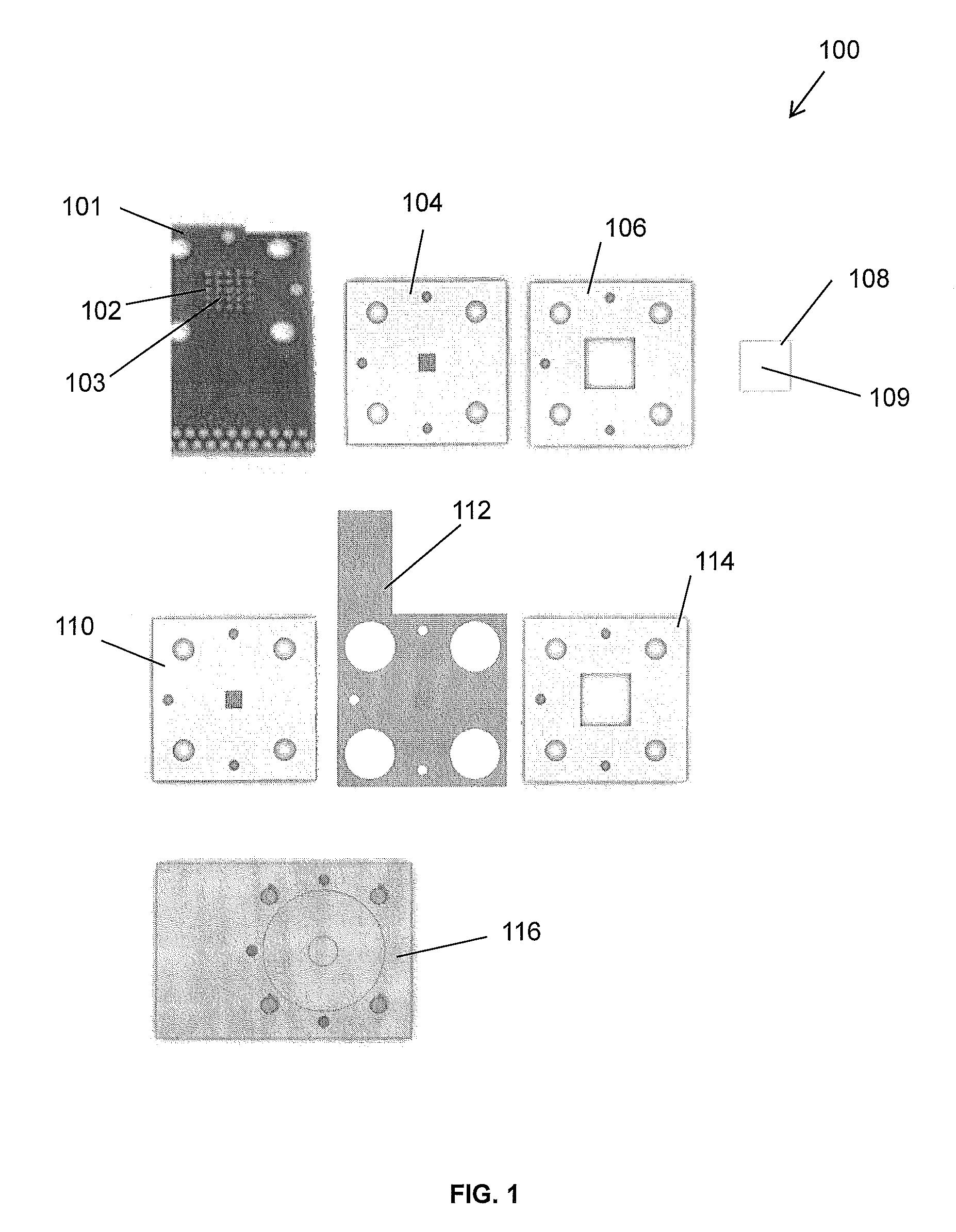

ActiveUS8992183B2Easy to parallelizeSuitableCircuit elementsLaboratory glasswaresElectricityEngineering

Electro-osmosis is used to create droplets in order to easily, carefully, and quickly pick-and-place millions of objects (ranging in size from millimeters to nanometers) individually or in parallel. Droplets are formed within channels that are individually controlled in order to achieve a predetermined configuration of the selected objects.

Owner:CORNELL UNIVERSITY