Negative voltage decoding circuit

A decoding circuit, negative voltage technology, applied in the direction of logic circuit connection/interface layout, logic circuit coupling/interface using field effect transistors, static memory, etc., can solve problems such as reduction, power supply asymmetry, and circuit failure , to achieve the effect of reducing the maximum voltage, reducing the conversion power consumption, and increasing the size

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0033] The specific embodiment of the present invention will be described with reference to the accompanying drawings.

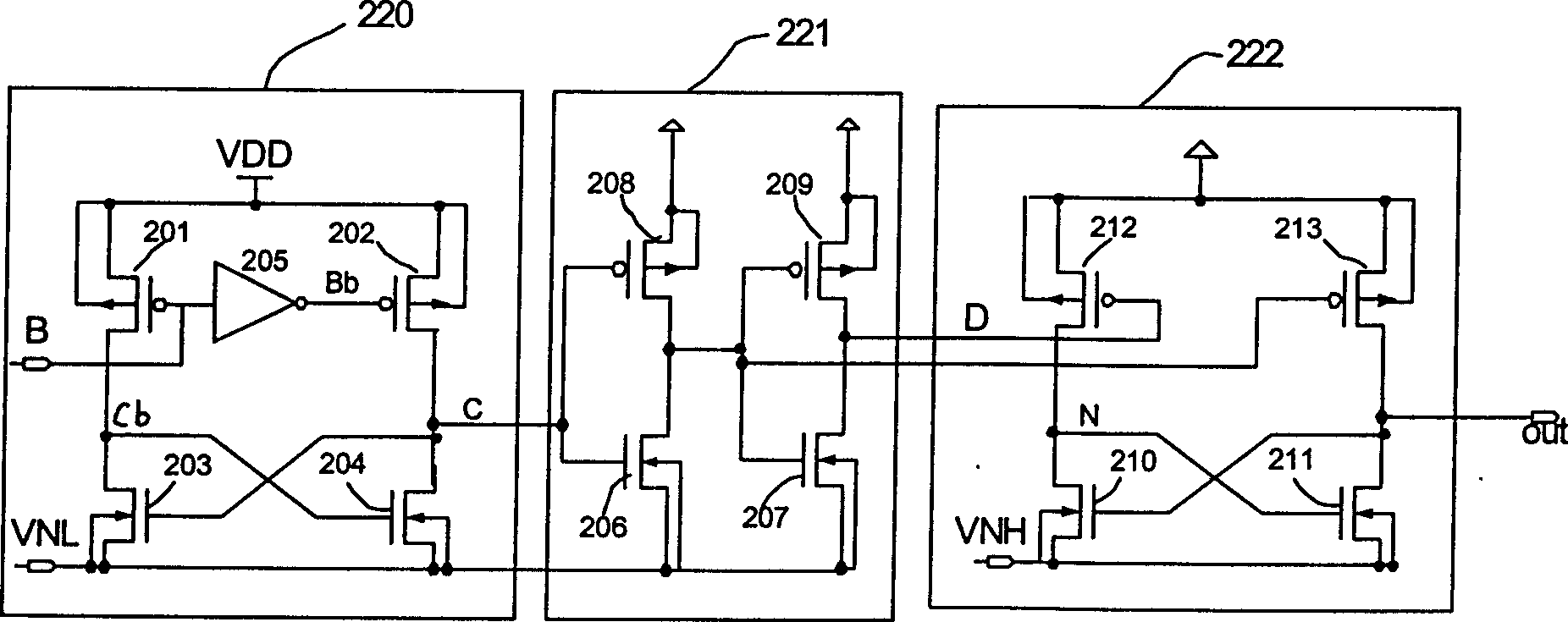

[0034] Figure 4It is the negative voltage decoding circuit proposed by the present invention, wherein the first-stage negative voltage level conversion circuit is composed of high-voltage PMOS transistors 403-406, high-voltage NMOS transistors 401, 402 and a CMOS inverter 407 working at VDD voltage.

[0035] The drain of the high-voltage PMOS transistor 404 is connected to the node E (the drain of the NMOS transistor 401 ), the gate is connected to the output node C (the drain of the NMOS transistor), and the source is connected to the input terminal A. The drain of the high-voltage PMOS transistor 405 is connected to the node E, the gate is fixedly grounded, and the source is connected to the input terminal A. The drain of the high voltage PMOS transistor 403 is connected to the output node C, the gate is connected to the node E, and the source is connect...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More