Contact hole forming method of semiconductor component

A contact hole and semiconductor technology, which is applied in semiconductor devices, semiconductor/solid-state device manufacturing, electrical components, etc., can solve the problems of deformation and deterioration of semiconductor components

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

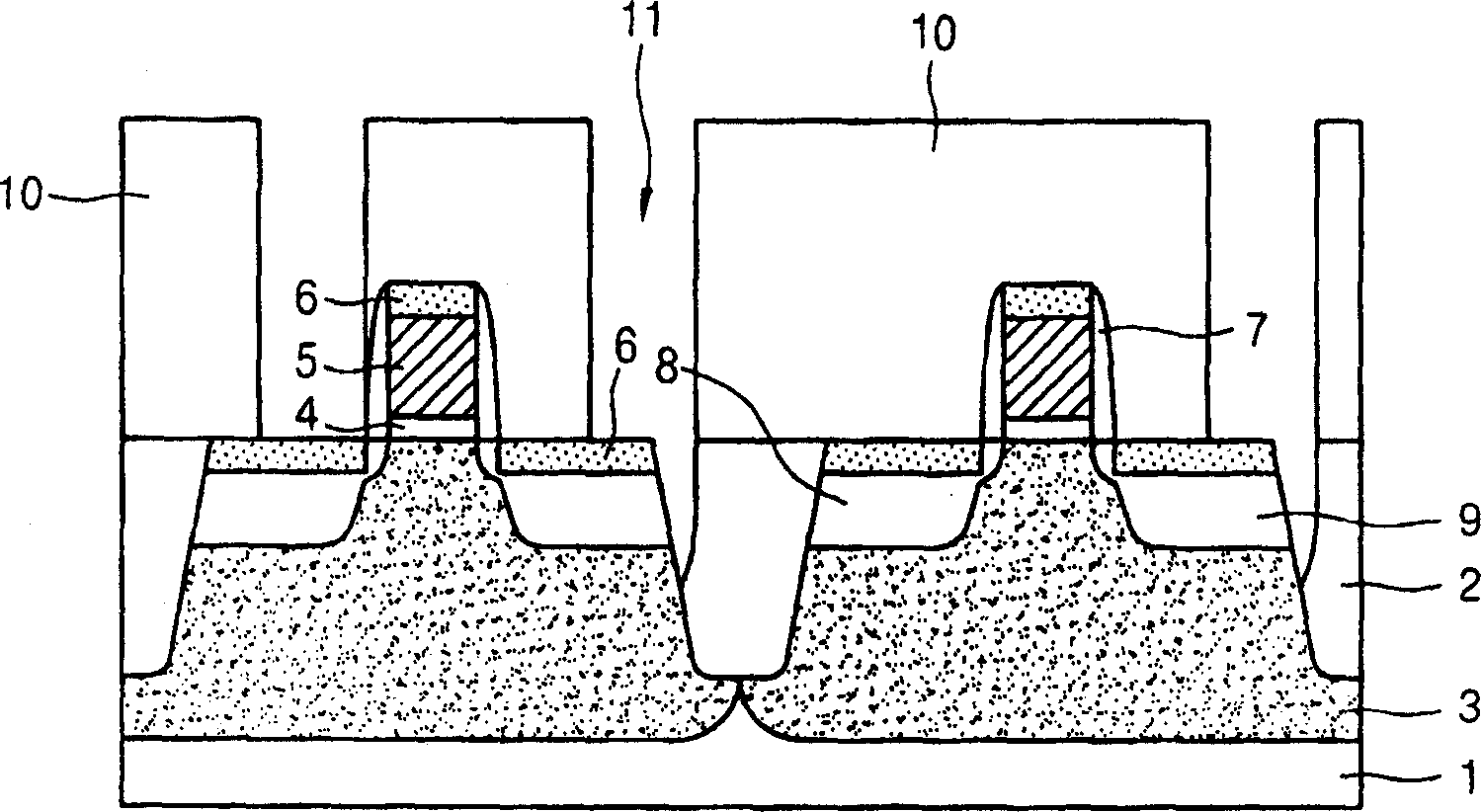

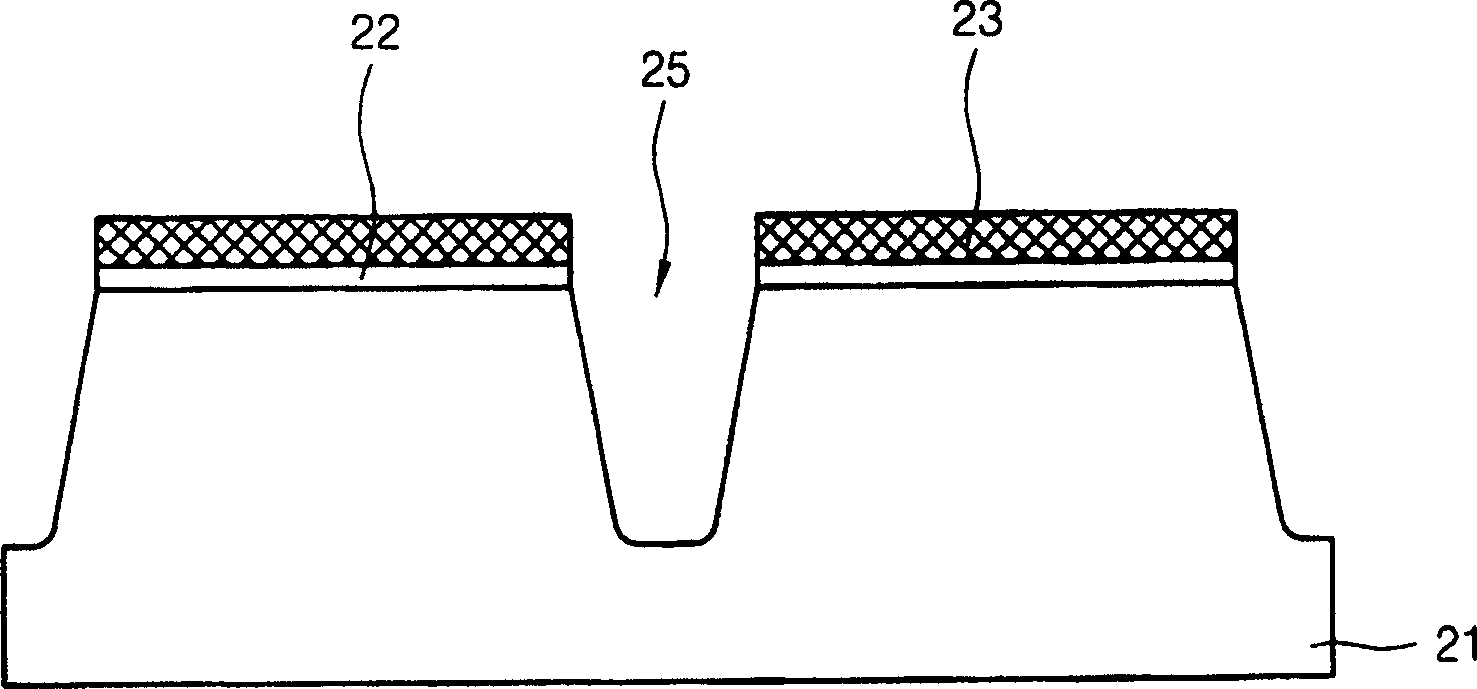

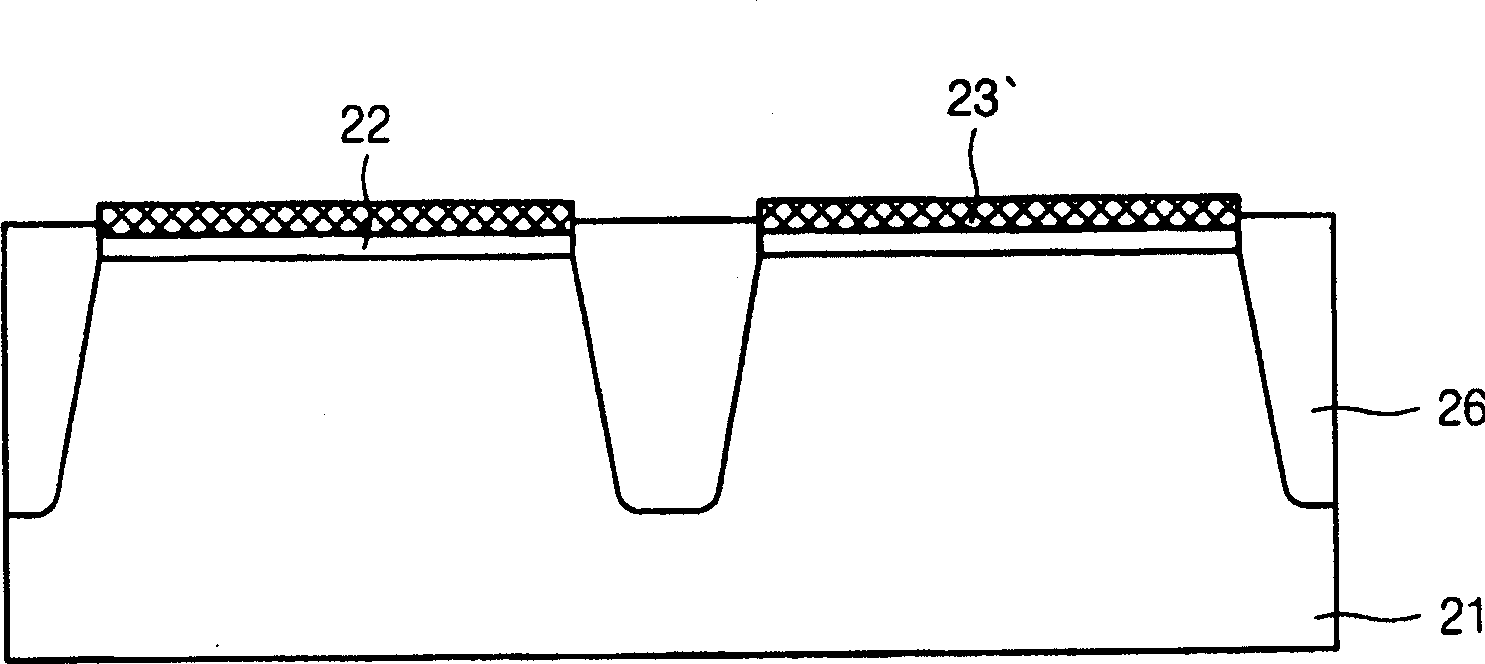

[0070] Below, describe preferred specific embodiment of the present invention in detail with reference to accompanying drawing, in following description and accompanying drawing, with identical reference number designate identical or similar component, and for identical or similar component, its repeated description will give omitted.

[0071] Figures 3A to 3I is a cross-sectional view illustrating a method of forming a contact hole in a semiconductor package according to the present invention.

[0072] see Figure 3A , depositing a pad oxide layer (SiO 2 ) layer 102, and then deposit a predetermined thickness of silicon nitride (Si 3 N 4 ) 104, at this time, the deposited silicon nitride layer (Si 3 N 4 ) 104 fills the interior of the trench with deposited oxide in a subsequent step and serves as a polishing stop layer when planarized using a chemical mechanical polishing (CMP) process;

[0073] Secondly, after coating the photosensitive material 106 on the silicon ni...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More