Integrated circuit layout plan and buffer plan integrated layout method

A technology of layout planning and integrated circuits, applied to circuits, instruments, electrical components, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

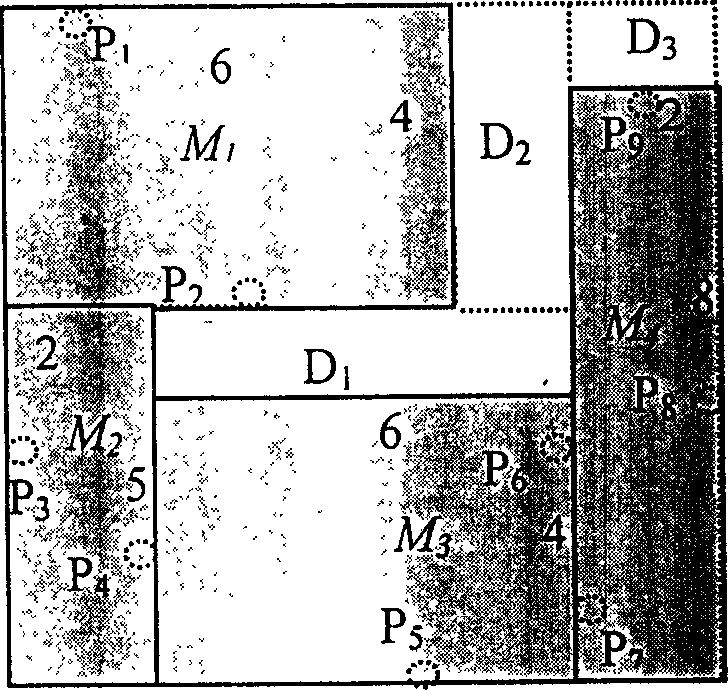

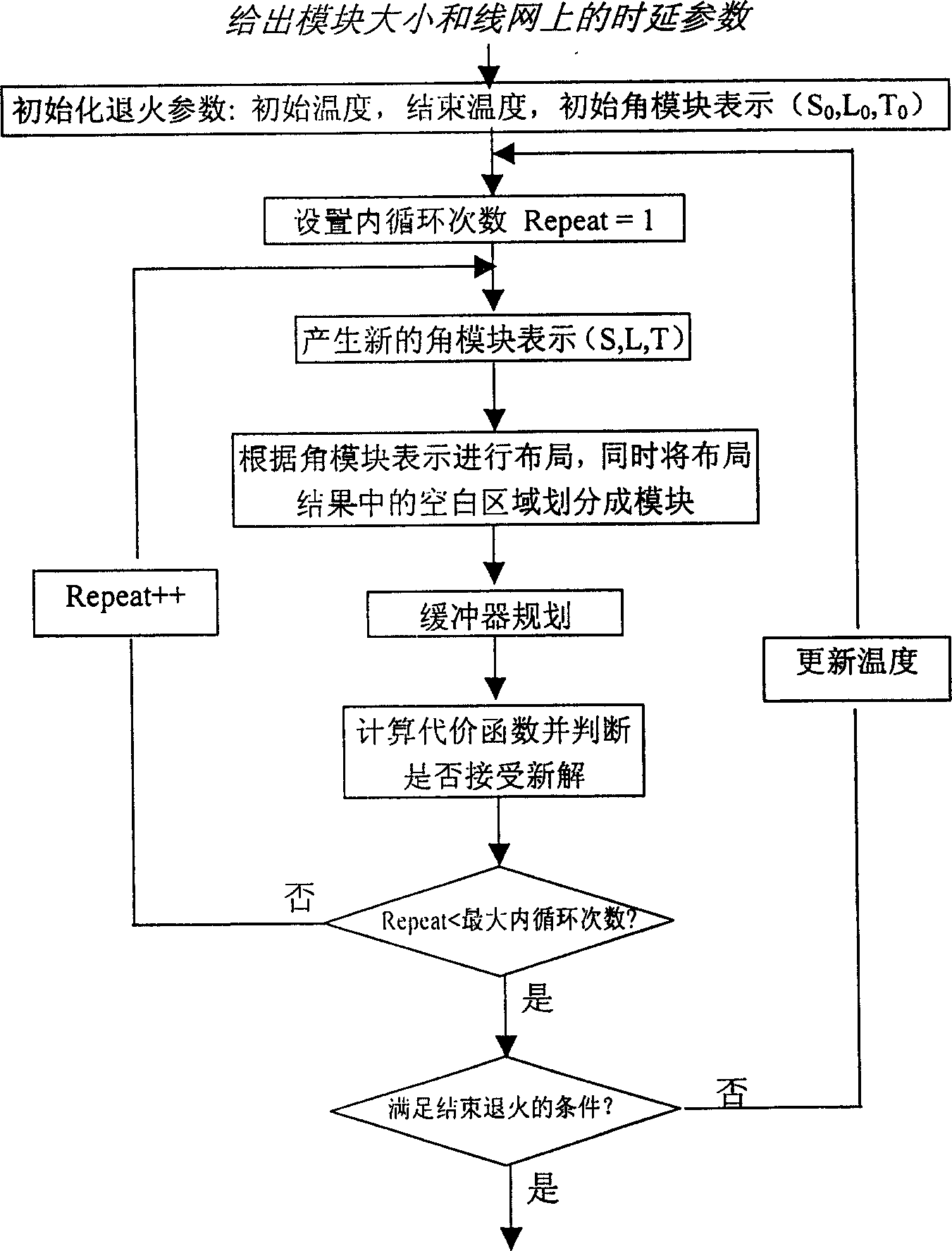

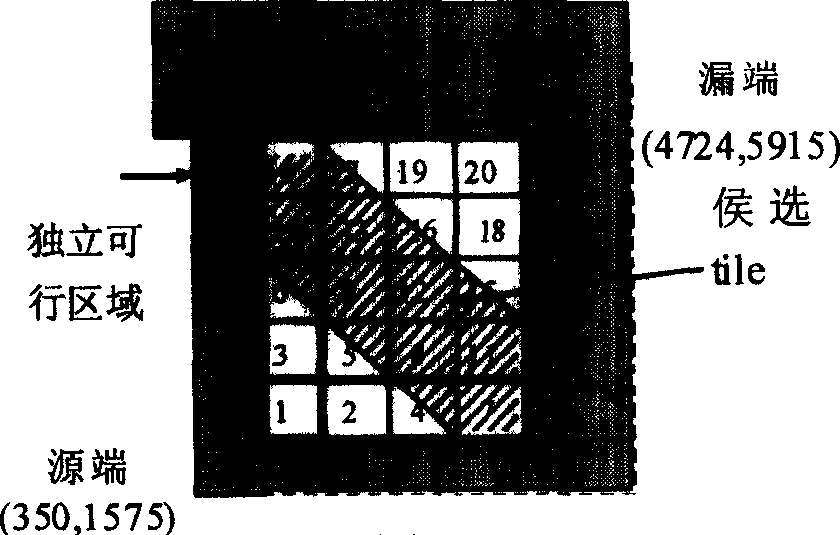

[0112] The present invention can be applied to different layout plans / layout representations based on rectangular divisions (that is to say, this type of layout representation divides chips into rectangular areas whose number is greater than or equal to the number of modules, and each rectangular area has at most one module) accomplish. This part adopts the layout result represented by the corner module as an example of the present invention, and adopts the Elmore time delay model as the model of time delay calculation. combine figure 2 Flowchart of the method of the present invention for floorplanning integrated with buffer insertion planning. Table 1 provides the definitions and values of some variables.

[0113] r

Wire resistance per unit length ( / m)

0.0755

c

Line capacitance per unit length (fF / m)

0.118

T b

Buffer Intrinsic Latency (ps)

36.4

C b

Buffer Input Capacitance (fF)

23.4

...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com